概要

FPGA内部のOneShotトリガの発生状況をLEDで目視したい場合、トリガ信号をLED出力ピンに接続したとしてもパルス幅が短すぎてLEDの発光を目視確認できません。

入力パルスを規定幅以上に引き延ばすモジュールを作っておいて、このモジュールを通してLED出力に接続することで目視確認しやすくなります。

注意事項

本モジュールはFPGA内部にあるクロック同期しているトリガを入力することを前提としています。

ピンから直接入ってくる(同期化していない)パルス入力信号を引き延ばしたい場合は、本モジュールの前段で同期化してエッジ検出する必要があります。

動作概要

- 入力がアサートされると指定カウントをロード

- カウンタはダウンカウント動作で、ゼロ到達でホールド

- 出力パルスはダウンカント中アサートする

- ダウンカウント中に入力が再アサートされた場合も指定カウントをロード(出力は途切れずに延長させる)

ポイント

引き延ばすクロックサイクル数の指定カウントをパラメータ化しています。

論理合成時は500msなど実際に目視できる長さにしますが、シミュレーションの500msは長すぎるのでシミュレーション時のみ10サイクルとか適当な長さにすることができます。

VHDLソース

------------------------------------------------------------------

--入力パルスを規定幅以上に引き延ばすモジュール

------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity PULSE_EXTENDER is

generic(

EXTEND_CYCLE :integer := 50000000--引き延ばすクロックサイクル数(50MHzで0.5s)

);

port (

i_CLK :in std_logic;--クロック入力

i_RST_p :in std_logic;

i_SOURCE_PULSE_p:in std_logic;--元のパルス

o_EXTEND_PULSE_p:out std_logic--引き延ばしたパルス

);

end entity;

architecture RTL of PULSE_EXTENDER is

signal pulse_count :integer range 0 to EXTEND_CYCLE-1;

signal pulse_ext :std_logic;

begin

process(i_CLK,i_RST_p)begin

if(i_RST_p='1')then

pulse_count <= 0;

pulse_ext <= '0';

elsif(rising_edge(i_CLK))then

if(i_SOURCE_PULSE_p='1')then

pulse_count <= EXTEND_CYCLE-1;--カウントをロード

pulse_ext <= '1';

else

--ダウンカウントさせて0まで到達したら止める

if(pulse_count = 0)then

pulse_count <= 0;

pulse_ext <='0';

else

pulse_count <= pulse_count - 1;

pulse_ext <='1';

end if;

end if;

end if;

end process;

o_EXTEND_PULSE_p <= pulse_ext;--出力パルス

end architecture;

テストベンチ

`timescale 1ns / 1ps

module PULSE_EXTENDER_tb();

reg i_CLK =0;

reg i_RST_p =1;

reg i_SOURCE_PULSE_p=0;

wire o_EXTEND_PULSE_p;

PULSE_EXTENDER #(

.EXTEND_CYCLE(20) // 新しいクロックサイクル数を指定

) PULSE_EXTENDER (

.i_CLK (i_CLK ),

.i_RST_p (i_RST_p ),

.i_SOURCE_PULSE_p(i_SOURCE_PULSE_p),

.o_EXTEND_PULSE_p(o_EXTEND_PULSE_p)

);

//パルス入力

task TASK_TRIGGER;

begin

@(posedge i_CLK);

i_SOURCE_PULSE_p = 1;

@(posedge i_CLK);

i_SOURCE_PULSE_p = 0;

end

endtask

//クロック50MHz

always #20 i_CLK = ~i_CLK;

initial begin

#200;

i_RST_p = 0;//リセット解除

#500;

TASK_TRIGGER();

#1200;

//アサート中に入力させる

TASK_TRIGGER();

#400;

TASK_TRIGGER();

#500;

TASK_TRIGGER();

end

endmodule

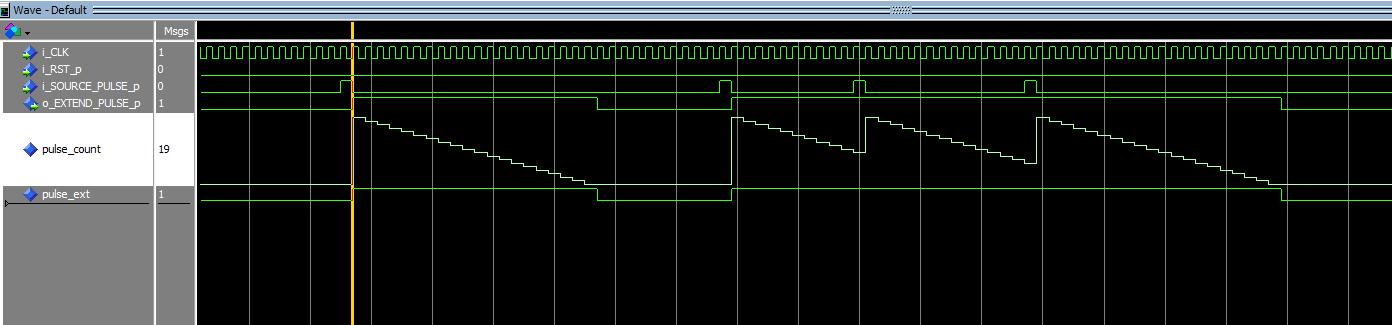

シミュレーション

シミュレーションでは延長設定を20サイクル

に短縮しています。

1発目の入力は20サイクル(カウント19~0)に引き延ばされ、2~4発目ぱ延長した動作になります。

その他応用

パルスの発生状況をレジスタリードでモニタしたい場合にも応用できます。

リード周期より長めに引き延ばしておけばパルスが来ているか否かをモニタしやすくなります。