GUI を使うと後々便利かも?

前回の環境を引き継ぎつつ回路図エディター(Diagram) を使えるようにします。

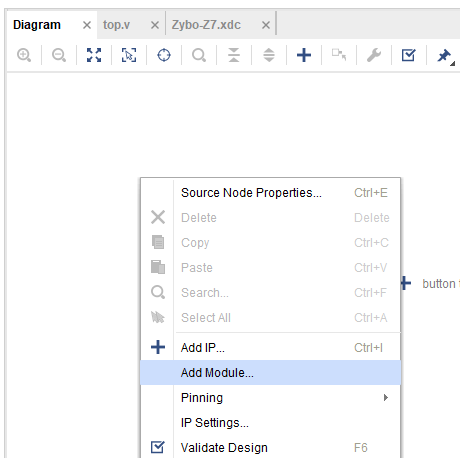

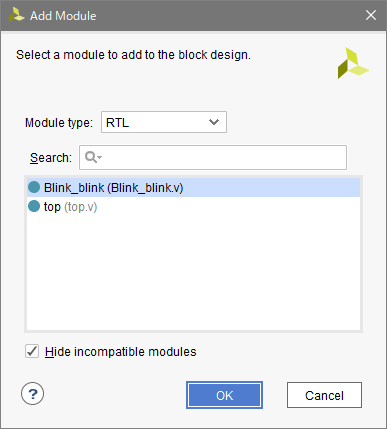

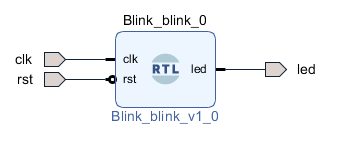

Diagram に追加

Diagram 右クリックのメニューから Add Module.. を選択し Blink_blink を追加。

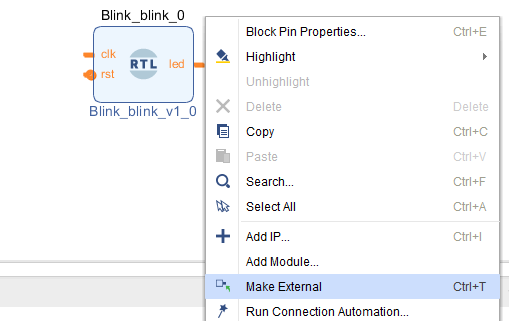

Diagram の完成

まずは3つの線を外に出すために Make External を選択します。

clk_0, rst_0, led_0 という名前になってしまったので _0 を取り除きます。

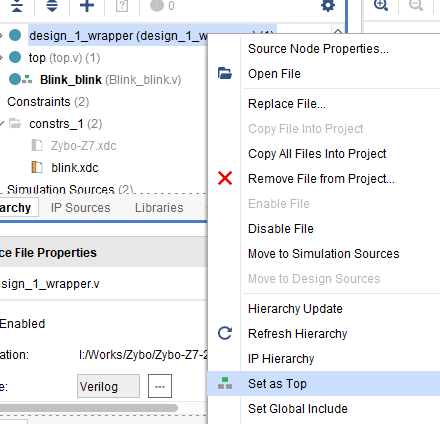

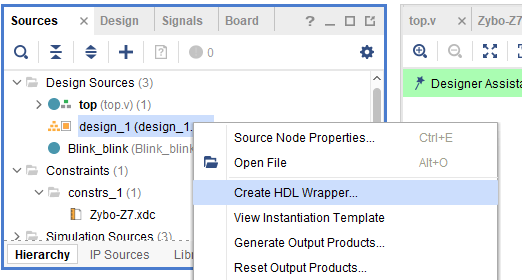

デザインの入れ替え

トップが Verilog になっているのでそれを入れ替えます。

Create HDL Wrapper を選択します(普通に Verilog 追加した方がよかった?

Set As TOP でトップモジュールに指定します。

合成&実行

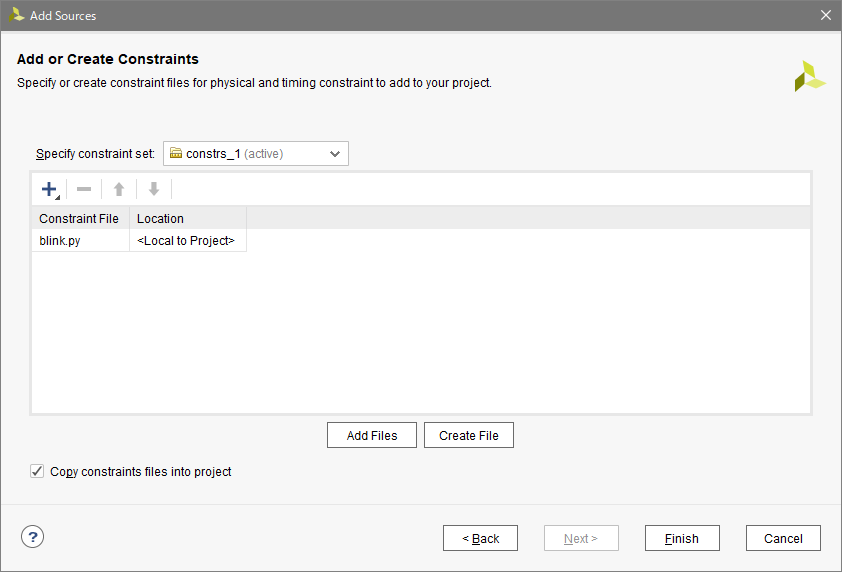

xdc は前作と同じでよいので、そのままで合成&実行です。

念のため再掲。

set_property -dict { PACKAGE_PIN K17 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L12P_T1_MRCC_35 Sch=sysclk

create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports { clk }];

# LED

set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports { led }]; #IO_L23P_T3_35

set_property -dict { PACKAGE_PIN K18 IOSTANDARD LVCMOS33 } [get_ports { rst }]; #IO_L12N_T1_MRCC_35

行時にビットストリームが見つからないと言ってくることがあるので、その時はファイル選択をあらためてしてください。Vivado の TCL の Console に debug_hub に関するワーニングが出ますがこれは(clk の設定の問題)気にしなくてよいでしょう。

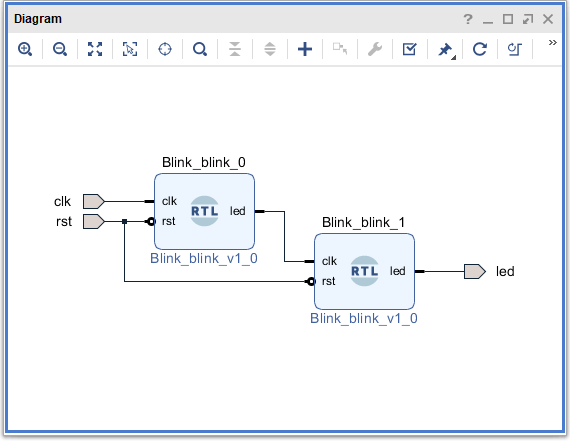

Lチカにする

clk が早すぎて LED が点灯しっぱなしに見えるのは Diagram を使っても変わりません。そこで、Blink_blink 二段重ねにしてみます。

GUI なので比較的簡単に絵のようにできるのではないでしょうか?Blink_blink_0 をコピー&ペーストすれば Blink_blink_1 ができます。後は絵の通りにつなぎなおすだけです。再合成して実行してみるとうまく Lチカになりました。クロックは 125MHz のはずでこれを 1/10000 の 1/10000 にしているので 1.25 秒で点滅している”はず"です。