「もう一つの」というフレーズは、何かしらのメインラインがあった上に、今までスポットライトが当たっていないストーリの存在を見つけた。そんなキュレータの思いを伝える言葉のように読み取れる。

Lチカにそんな折り重なるようなストーリ性を見いだせるか?

Vivado にモジュールとして組み込む

Polyphony で生成した Verilog-HDL を Vivado のIP Integrator のブロックデザインの中にに組み入れることは比較的容易にできる。

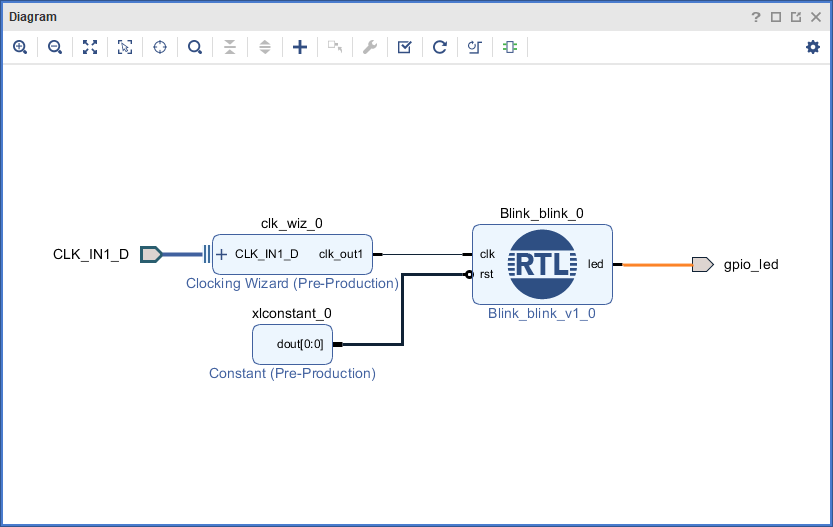

Add Module を使えば RTL を直接ブロック・デザインの中に配置できる。このモジュールを使う際の難点はバージョン管理がなされないことか? Verilog-HDL を更新すれば、例えば Polyphony を起動してコンパイルし Verilog のファイルを更新すれば、もちろんVivado は気が付いてくれて再合成が必要なことを教えてくれる。ただ、IP-XACT とは違い IP Report のバージョンはそのままだ。

RTL の文字デザインもなんとなくどんくさい。

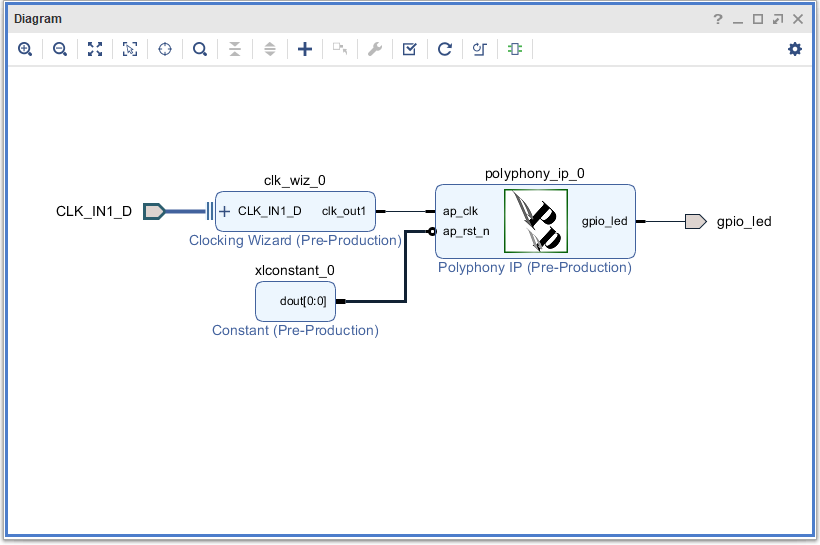

Vivado HLS ライクに組み込む

Vivado HLS のように IP-XACT をうまく作り、高位合成コンパイラを合成時に呼び出せないか?試しにやってみた。ついでにロゴも入れてみる。

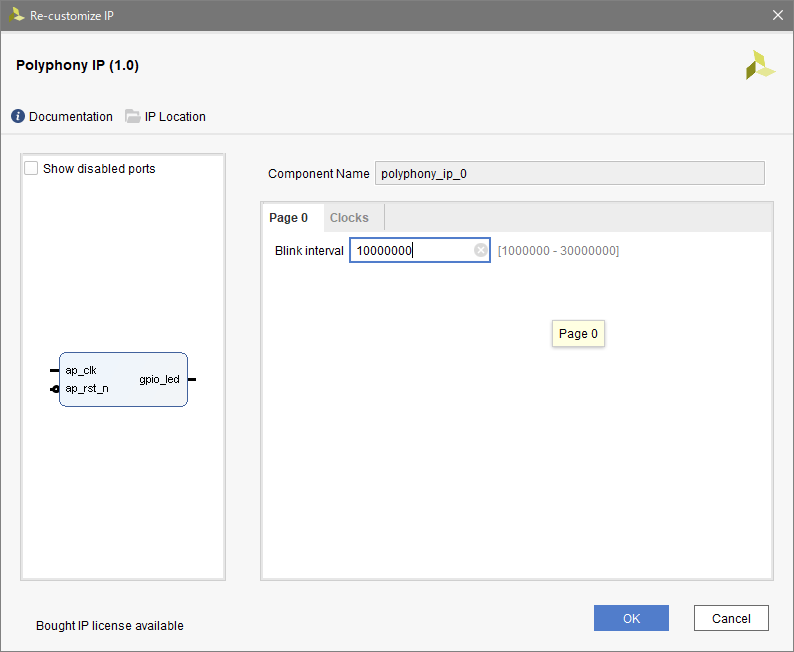

少々強引なつくりなっているがウィザード画面も表示できLチカの間隔を変えることが出来る。ウィザードを閉じれば Polyphony によって新たに Verilog のソースが生成される。

Python3 とPolyphony が特定の場所にあること前提だがこの形式が使えれば Polyphony で生成する Verilog はより柔軟性を持つ。使用者は IP-XACT の使い方さえ分かっていればよい。

Python は次のディレクトリにあることを前提にしている。

C:/Users/ryos/AppData/Local/Programs/Python/Python36/python

使う際には、Windows 用の Python3.6 をインストールして polyphony を pip3 でインストールしたうえで環境に応じて IP-XACT 内の polyphony_compile.ttcl を書き直す必要があるので注意されたい。

IP-XACT は次の URL からダウンロード可能だ。

polyphony_ip_blink.zip