Vivado のシミュレーションを使う

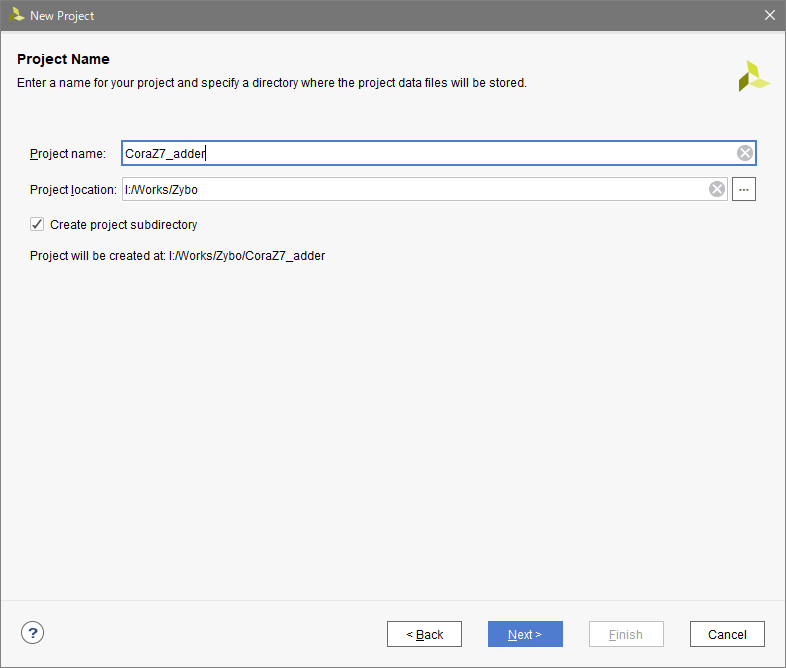

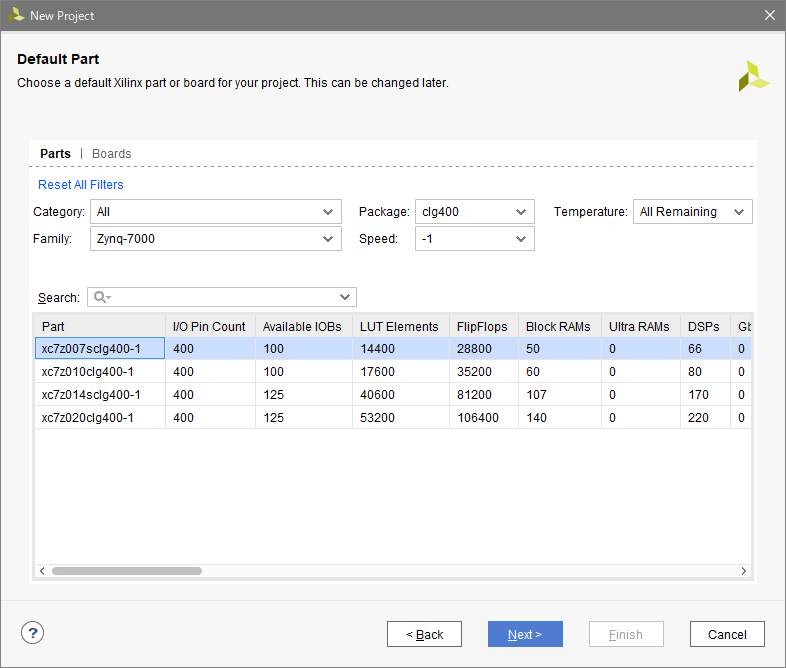

Cora Z7 を対象としたいのでまずは xc7z7007sclg400-1 のプロジェクトを作ります。

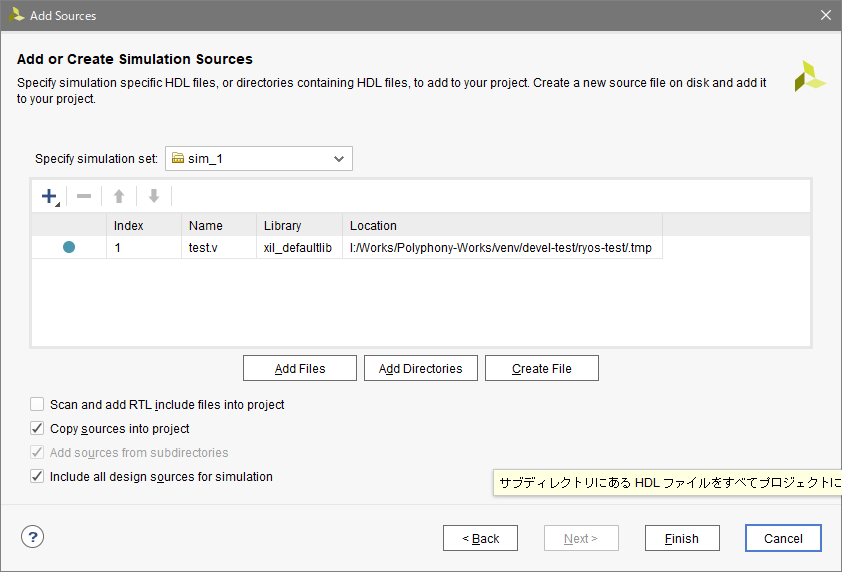

polyphony が生成した Verilog ファイル

simu.py で出来たファイルは .tmp 内にあります。ここでは前回と同様 adder.py をコンパイルしています。

simu.py 実行

> ../polyphony/simu.py adder.py

Compiling: [=========================] 100% ... printresouces

(99, 66, 2)

v = 3

170:finish

> ls .tmp

_adder.v debug_log debug_log.top.adder test*

adder.v debug_log.top debug_log.top.test test.v

簡単な足し算プログラムで出来た test.v _adder.v の Verilog を Vivado に追加します。test.v はシミュレーション用です。

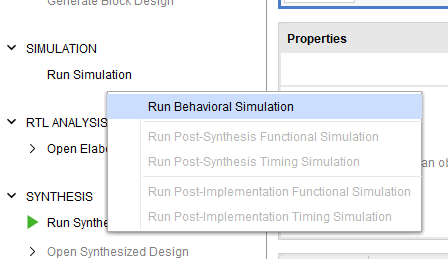

シミュレーション実行

Run Behavioral Simulation を実行します。

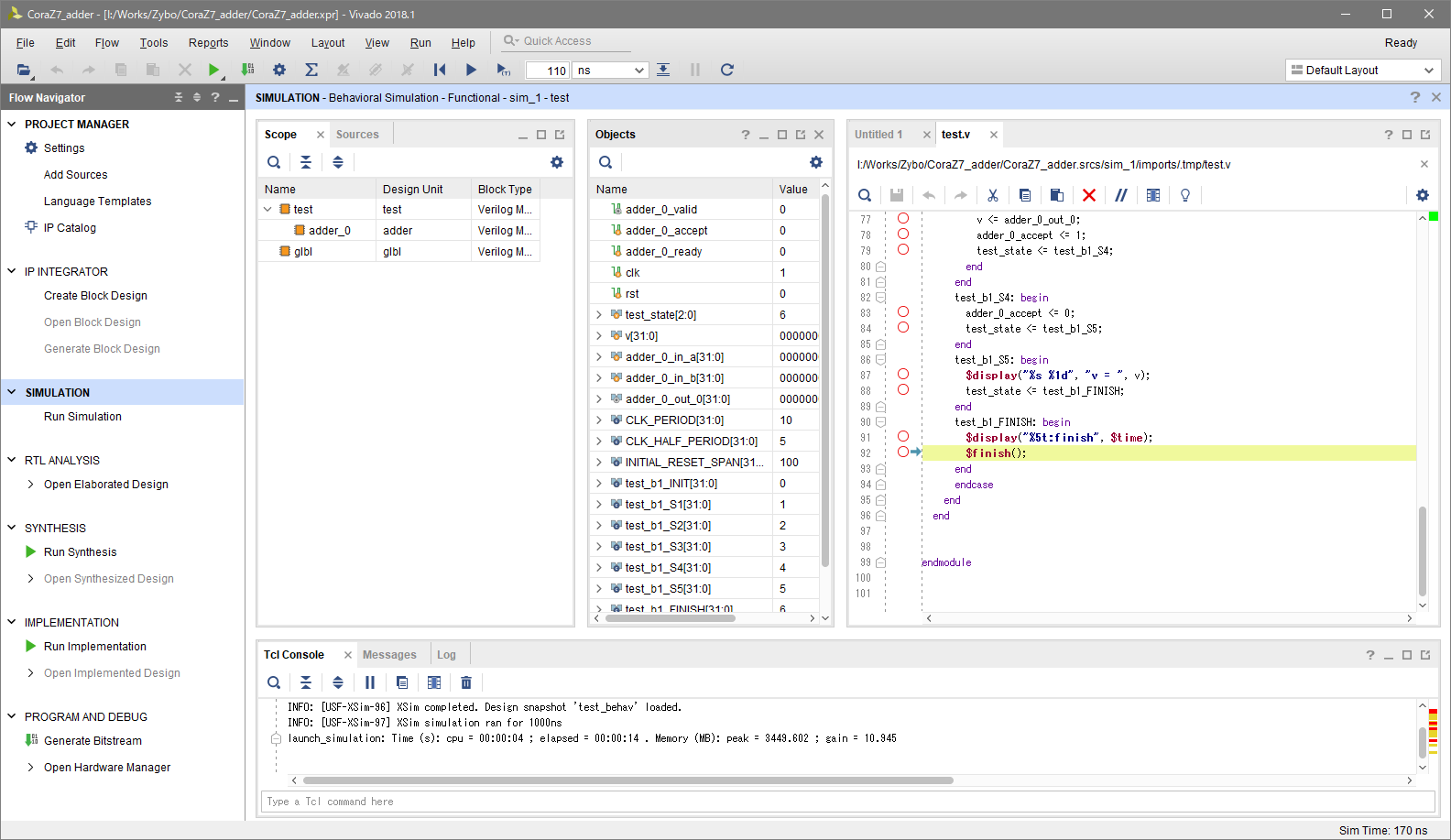

シミュレーション用の画面になりました。finish で止まっていてすでに実行済みのようです。

シミュレーション結果を見る

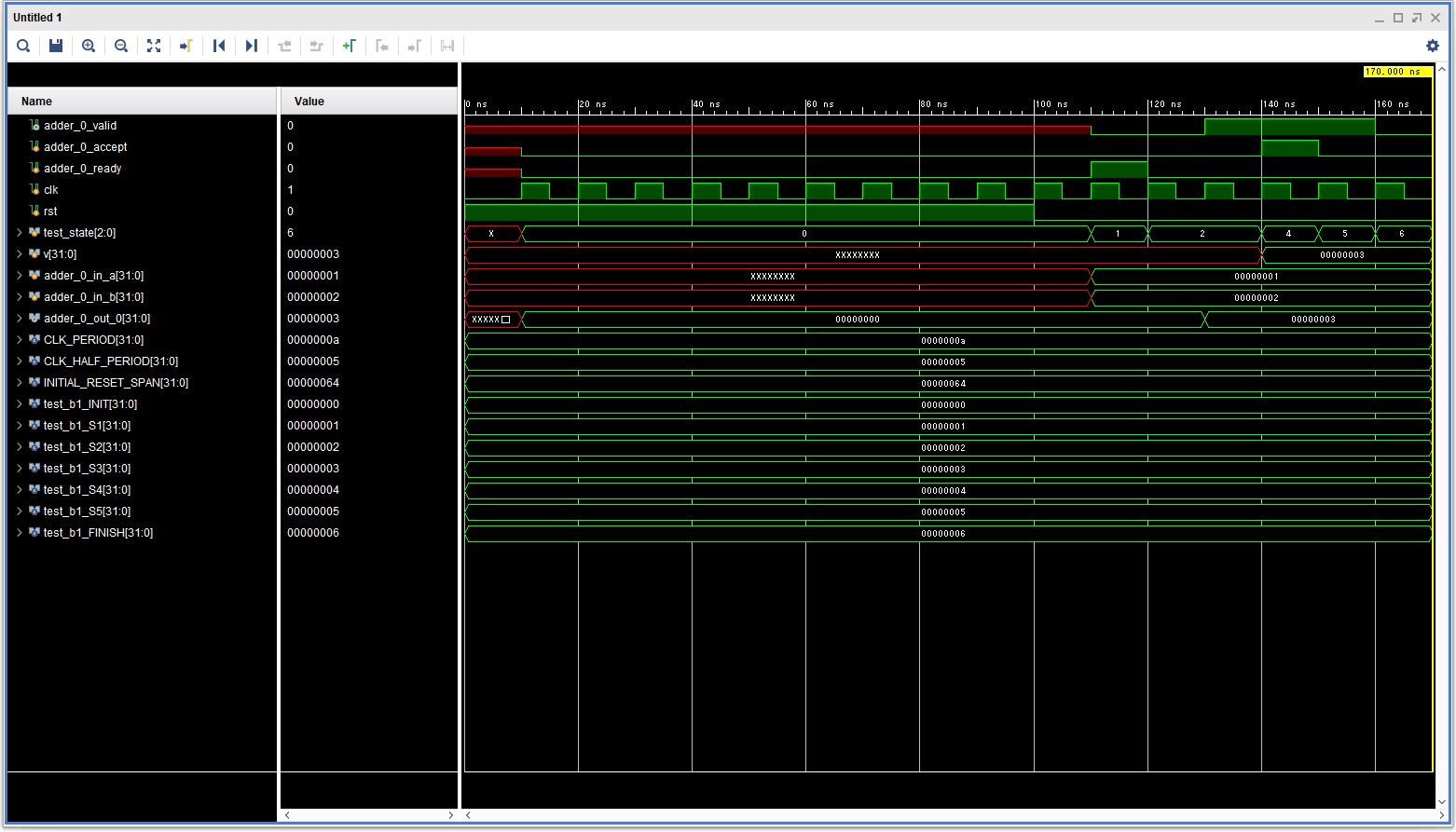

Untitled のタブがシミュレーション結果です。うまくいったようです。