Digilent の Zynq

いままでまったく気が付かなかったのですが、Diglilent がかかわっている一連の Zynq の評価ボードは回路的にちゃんと PL で使える sysclk なるものがあります。これを使えば Lチカが簡単にできます。SDK を使う必要がありません!!

確認したのは次の基板

- Zybo

- Zybo Z7

- PYNQ

- Cora Z7

- Arty Z7

あと UltraZed も大丈夫です。

逆にそういった考慮がされていないのは

- ZedBoard

- Ultra96

です。

ここでは Zybo Z7 のサンプルの使い方を順を追って説明します。あまりビギナー向けではないかもしれません。そして目的も曖昧。

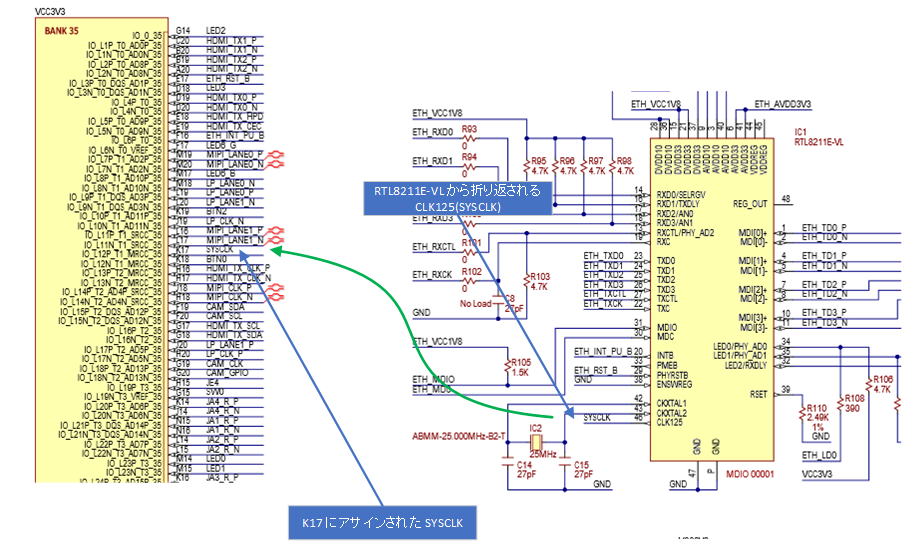

回路図の確認方法

Zybo Z7 なら schematic というキーワードをつけて検索すると回路図に行き当たるでしょう。回路図を下に貼り付けます。見方としては ETHER 用の PHY のチップである RTL8211E-VL が出力している CLK125 が SYSCLK として Zynq の PL(FPGA側) に繋がっています。この SYSCLK を間借りすれば ARM からのわざわざクロックを供給してもらう必要はありません。

ARM から供給してもらう場合は SDK の助けが必要になり FPGA 側単体でうまくうごかせません(なれればどうという事もないと言えなくもない)

Zybo Z7 のデモ

こんどは Zybo Z7 を使ってみましょう。

Example Projects には次の5つがあります。XADC デモがそれっぽいのでそれを展開実行することにしましょう。

- [Zybo Z7 DMA Audio Demo] (https://reference.digilentinc.com/learn/programmable-logic/tutorials/zybo-z7-dma-audio-demo/start)

- Zybo Z7 HDMI Demo

- Zybo Z7 Pcam 5C Demo

- Zybo Z7 Pmod VGA Demo

- Zybo Z7 XADC Demo

XADC デモを展開する

https://github.com/Digilent/Zybo-Z7-20-XADC/releases)

git を使う場合はちょっと面倒

https://github.com/Digilent/Zybo-Z7-20-XADC

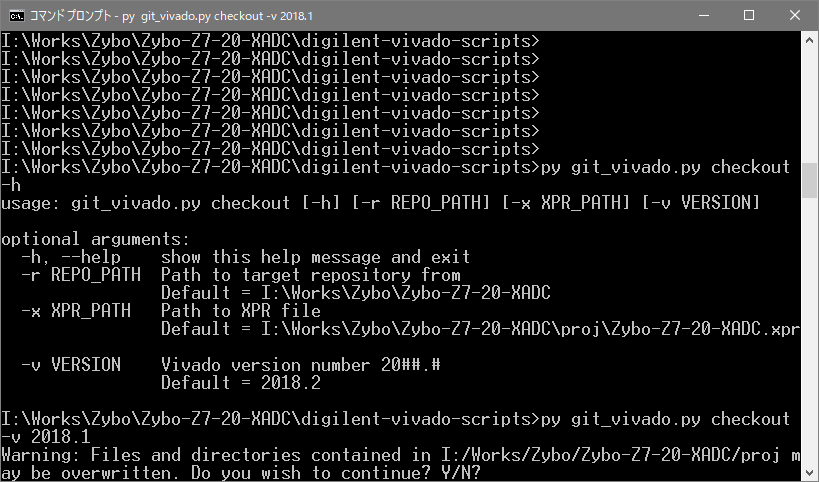

に詳細があるのでこれをたよりに Vivado のプロジェクトとして使えるようにします。もともとは 2018.2 用なので Vivado 2018.2 を使った方がいいのですが、今回は 2018.1 をつかってしまいました(<=トラブルのもとです)

- git clone https://github.com/Digilent/Zybo-Z7-20-XADC (7020 用)

- git のサブモジュールを使っているので git submodule update --init

- Vivado 2018.1 に board file を予め追加しておく

- cmd 起動

- py git_vivado.py checkout -v 2018.1 (Linux なら単純に python でよい)

使うのが Vivado 2018.2 なら -v 以降の引数は必要ありません。

うまくいけば proj に Zybo-Z7-20-XADC.xpr が出来ているはずです。

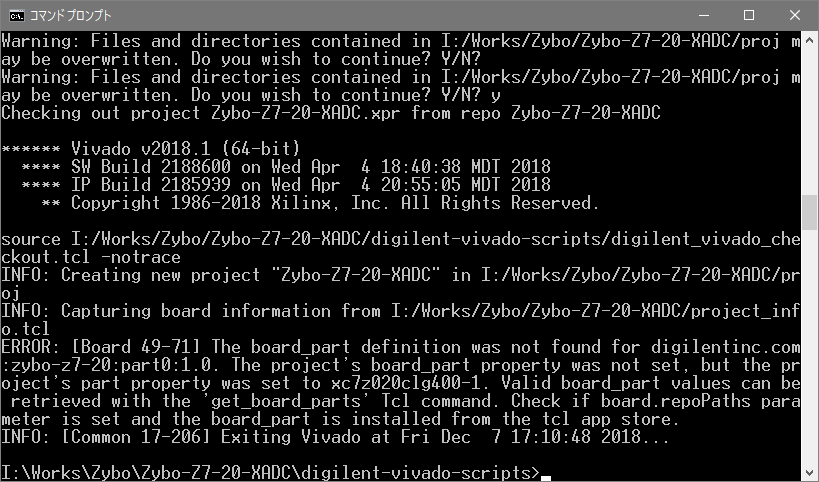

ボードファイルがなくて失敗した例

毎度毎度です。失敗します。がめげません。

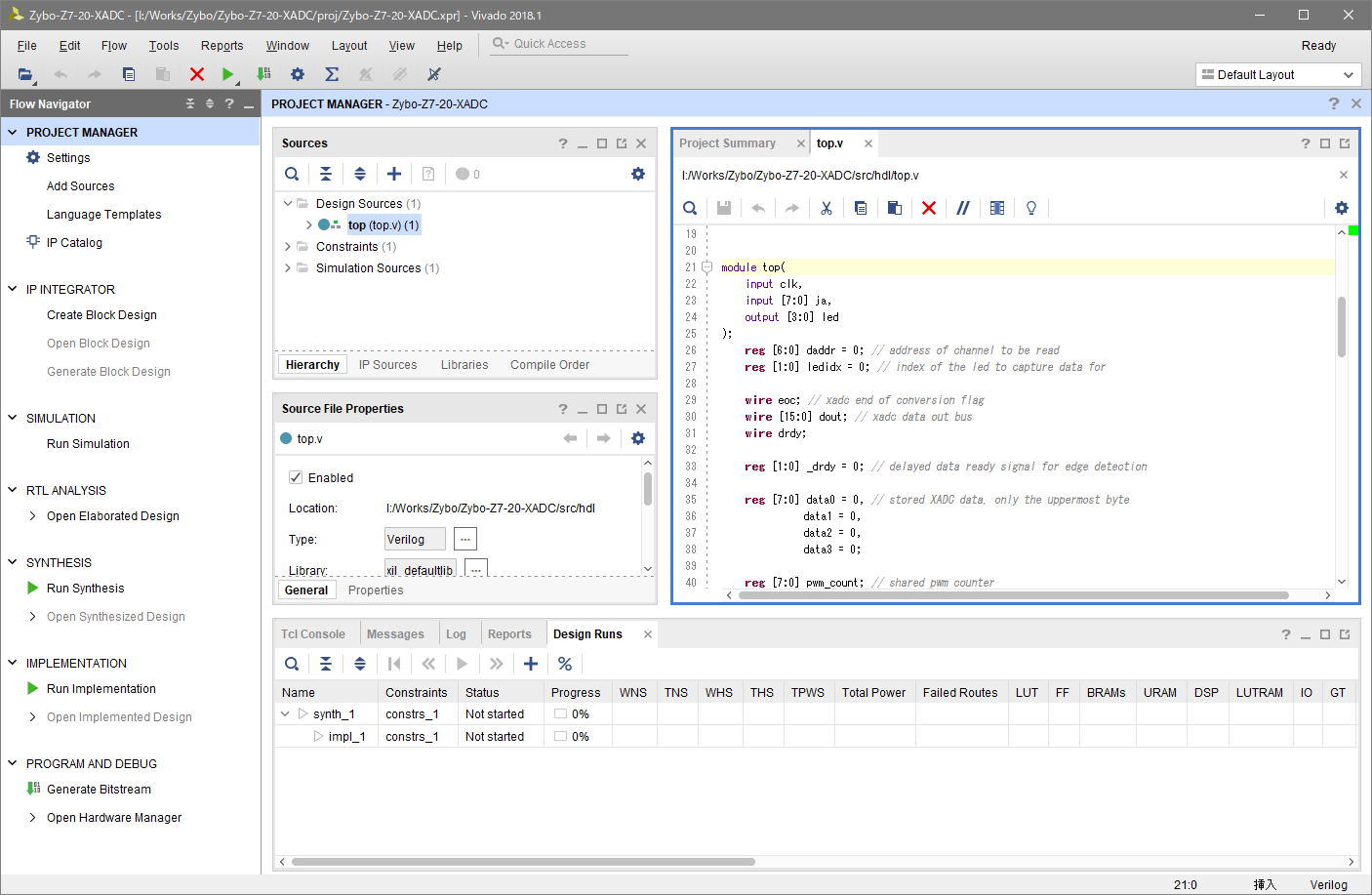

Vivado 2018.1 起動

できた!!

トップは Block Design (回路図風のデザイン) ではなく Verilog-HDL そのものです。

module top(

input clk,

input [7:0] ja,

output [3:0] led

);

xdc をみると K17 で回路図と一致しています。

set_property -dict { PACKAGE_PIN K17 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L12P_T1_MRCC_35 Sch=sysclk

何が出来た?

これを動かすと、下の URL と同じデモが動くはずです。これは XADC の AD コンバータの機能を使っていて 1.0 がきたら LED がつくように設計されているようです。くれぐれも下のドキュメントをちゃんと読んで、とくにショートさせないようにしましょう。

何がしたかった?

このデモでは PMOD と LED "だけ"をつかって FPGA のデモが出来ました。これを参考にすれば Polyphony で作った Lチカ を Vivado だけで動かすことが出来ます。SDK の立ち上げが必要なくなり、ソフトウェアなしの実行環境が出来上がる、、、という寸法です。