私はメモリデバイスの不揮発性メモリ制御やホストIFなどを扱うソフト屋です。

仕事でCXL(Compute Express Link)まわりの技術に関わっています。

CXL技術に関連するメモ書きを残していこうと思います。

ホストまわりのこと経験・知識共に乏しいので、詳しい親切な方は教えて下さると幸いです。

また、間違い、アドバイス、その他、ご意見やご要望ありましたらお気軽にどうぞ。

1. CXLデバイス(Type3)の主な機能

CXL2.0に対応Type3デバイスの主な機能は以下の通りです。それぞれの詳細は、今後書いていくことにします。

Type3が何なのかは、過去に投稿済みの記事をご参照ください。

-

MLD (Multi Logical Device)

オプションの機能。1つのデバイスのメモリ空間を分割して、それぞれを別のホストCPUに割り当てて使用するための機能。MLDに対応していないデバイスは、1つのホストCPUに占有させて使用するSLD (Single Logical Device)として扱われます。 -

Security

オプションの機能。ホストCPUとCXLデバイス間の通信路の暗号化とデータ完全性の保証するための機能です。仕様書では、CXL IDE(Integrity and Data Encryption)と呼ばれています。具体的には、AES-GCM鍵長256bitが使用されています。 -

Global Persistent Flush (GPF)

必須の機能。不揮発性メモリを記憶媒体とするType3のCXLデバイスは、ホストCPUからデータの読み書きの指示に対する応答のレイテンシを短縮するため、キャッシュやバッファを持つことが一般的な実装となります。GPFは、キャッシュやバッファ内のデータを不揮発性メモリへの退避を、ホストCPUが指示するための機能です。CXLデバイスの交換等で、ホストからCXLデバイスへの電源の供給を止める前に使用されます。 -

Managed Hot-Plug

ホストでOSやアプリケーションが動作している状態で、新たなCXLデバイスを接続して動作させるための機能です。この機能も、CXLデバイスの交換等で使用されます。

一般的に、DDR DIMMは、サーバへの電源供給を止めた状態で抜き差しされ、サーバの起動時に、BIOSが接続されたDDR DIMMの情報を読み取り、ACPIのテーブルを作成し、OSなどのソフトウェアに情報を渡す、という手順で使用されています。

CXL2.0対応のサーバでは、BIOSなしで、OSなどのソフトウェアが、Type3のCXLデバイスを認識し、ACPIテーブルの作成とメモリ空間の割り当てを行います。

どちらかというと、CXLデバイス側よりも、ホスト側が対応しなければならない機能ですが、必須の機能です。

CXLデバイスは、電源投入後、短時間でホストからのコマンド受信可能状態となることが要求されると予想されます。 -

Memory Error Reporting

Error Reportingは複数の機能で構成されており、必須の機能とオプションの機能があります。詳細は追々書いていきます。SSDなどNAND Flash Memoryが使用された製品でも分かるかと思いますが、一般的に不揮発性メモリでは、読み出しの際の読み出しエラーや、書き換えで寿命を迎えた際の書き込みエラー等のエラーが発生します。不揮発性メモリを記憶媒体として使用するデバイスで、DRAMを記憶媒体として使用するデバイスよりも高確率でエラーが発生することになります。Memory Error Reportingでは、これらCXLデバイスで発生したエラーの詳細をホストに伝えることができるようになっています。 -

QoS Telemetry

QoS Telemetryは複数の機能で構成されており、必須の機能とオプションの機能があります。QoS Telemetryは、CXLデバイスの負荷の状態をホストに通知するために使われる機能です。負荷の状態とは、CXLデバイスで処理しているデータの読み書きの混み具合を表しています。CXLデバイスの負荷が高い状態になると、ホストへの応答のレイテンシが長くなります。CXLの接続は、CXLデバイスとCPU間の接続となるため、応答のレイテンシが延びることによりCPUの動作効率に大きな影響を与えることになります。この機能で、CXLデバイスの負荷状況を知らせることにより、ホストCPUは応答のレイテンシを予測することができるようになります。

ホストCPUはこの情報を使用して、CXLデバイスに対して送るコマンドの数を調整することが想定されます。 -

Interleave

必須の機能。DDR DIMMのDRAMのように、ホストCPUに複数のCXLデバイスを並列に繋いで、CXLデバイスをインターリーブして使用するための機能です。Interleave自体は、CXL1.1でも記載されていますが、CXL2.0で強化されています。詳細は、どう違っているのかは追々書いていきます。

「CXLその2」で、「CXL 2.0はType3デバイス不揮発性メモリへの対応」が考慮された仕様と書きましたが、CXL2.0では上記のように、GPFやMemory Error Reportingなど不揮発性メモリを扱い易くするための機能が追加されています。

2. CXLデバイスとDDR DIMMとの接続の違い

CXL2.0対応デバイス(Type3)は、DDR DIMMと似た使い方ですが、CPUとDDR DIMMとでは、やり取りされない情報が仕様で定義されています。CPUとDDR DIMMとでやり取りされない情報が、CXL2.0デバイス(Type3)で必要となるのは、DDR DIMMとの接続の違いに起因しています。

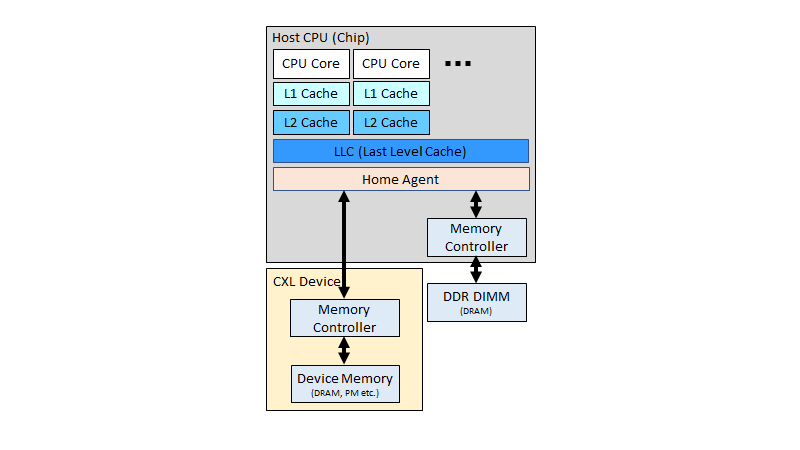

CPUとCXLデバイスとの接続、CPUとDDR DIMMとの接続、それぞれの概略を下図に示します。

図中のHome Agentは、キャッシュのコヒーレンシおよびメモリアクセスの管理を行っています。

CPUとCXLデバイスとの接続では、CXLを通して、CPUのHome AgentとCXLデバイスのメモリーコントローラが通信をします。一方、CPUとDDR DIMMとの接続では、DDRを通してメモリーコントローラとDDR DIMMが通信をします。

CPUとDDR DIMMとの接続では、Host CPUのChip内でやり取りされていたHome Agentとメモリコントローラの情報が、CXLではHost CPUのChipの外に出てくることになり、CXLの仕様で定義されています。

メモリコントローラは、制御する対象となる記憶媒体により異なります。CXLでは、ホストCPUのChip内に入っていたメモリコントローラをChip外に追い出したため、これまではCPUが直接高速にアクセスできるメモリが(一般的には)DRAMのみでしたが、DRAM以外も扱えるようになりました。

CPUのChip内からメモリコントローラを追い出してDRAM以外も使えるようにしたい、というのがCXLとして標準化する動機の一つとなっています。

次回以降もCXLの仕様の詳細について書いていこうと思っています。