概要

windowsでiverilogやってみた。

俺cpuにserialつけて見た。

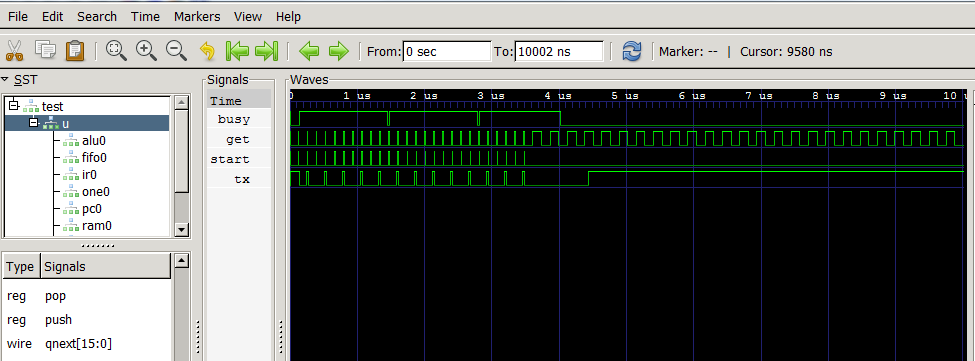

写真

動かしたコード

serialにaからzを吐く。

mem[0] = 16'h1000;//push 0

mem[1] = 16'h300f;//set 15

mem[2] = 16'h200f;//get 15

mem[3] = 16'h101a;//push 26

mem[4] = 16'hf00f;//>

mem[5] = 16'h5005;//if 5

mem[6] = 16'h200f;//get 15

mem[7] = 16'h1061;//push 97

mem[8] = 16'hf000;//+

mem[9] = 16'he000;//out

mem[10] = 16'h200f;//get 15

mem[11] = 16'h1001;//push 1

mem[12] = 16'hf000;//+

mem[13] = 16'h300f;//set 15

mem[14] = 16'h4002;//jp 2

mem[15] = 16'h0000;//i

サンプルコード

module test2(input clk, input rst, output tx, output reg led5 = 0, output reg led4 = 0, output reg led2 = 0);

wire [2:0] cs;

wire [15:0] irout,

dbus,

qtop,

qnext,

ramout,

aluout,

pcout;

reg [15:0] in;

reg [11:0] abus;

reg halt = 0,

cont = 0,

pcinc,

push,

pop,

abus2pc,

dbus2ir,

dbus2qtop,

dbus2ram,

dbus2obuf,

pc2abus,

ir2abus,

ir2dbus,

qtop2dbus,

alu2dbus,

ram2dbus,

in2dbus;

counter pc0(.clk(clk), .rst(rst), .load(abus2pc), .inc(pcinc), .d(abus), .q(pcout));

tx2 tx2(.clk(clk), .rst(rst), .start(start), .data(out), .tx(tx), .busy(busy), .get(get));

oneshot one0(.clk(clk), .rst(rst), .in(get), .out(get2));

fifo fifo0(.clk(clk), .rst(rst), .put(dbus2obuf), .get(get2), .data(dbus), .out(out), .empty(empty), .start(start));

buffer ir0(.clk(clk), .rst(rst), .load(dbus2ir), .d(dbus), .q(irout));

state state0(.clk(clk), .rst(rst), .cont(cont), .halt(halt), .cs(cs));

stack stack0(.clk(clk), .rst(rst), .load(dbus2qtop), .push(push), .pop(pop), .d(dbus), .qtop(qtop), .qnext(qnext));

alu alu0(.a(qtop), .b(qnext), .f(irout[4:0]), .s(aluout));

ram ram0(.clk(clk), .load(dbus2ram), .addr(abus[11:0]), .d(dbus), .q(ramout));

assign dbus = ir2dbus ? {{4{irout[11]}}, irout[11:0]} : 16'hzzzz;

assign dbus = qtop2dbus ? qtop : 16'hzzzz;

assign dbus = alu2dbus ? aluout : 16'hzzzz;

assign dbus = ram2dbus ? ramout : 16'hzzzz;

assign dbus = in2dbus ? in : 16'hzzzz;

always @(pc2abus or ir2abus)

begin

if (pc2abus)

begin

abus <= pcout;

end

else if (ir2abus)

begin

abus <= irout[11:0];

end

else

begin

abus <= 12'hxxx;

end

end

always @(cs)

begin

halt = 0;

pcinc = 0;

push = 0;

pop = 0;

cont = 0;

abus2pc = 0;

dbus2ir = 0;

dbus2qtop = 0;

dbus2ram = 0;

dbus2obuf = 0;

pc2abus = 0;

ir2abus = 0;

ir2dbus = 0;

qtop2dbus = 0;

alu2dbus = 0;

ram2dbus = 0;

in2dbus = 0;

led5 = 1;

led4 = 1;

led2 = 1;

if (cs == `FETCHA)

begin

pcinc = 1;

pc2abus = 1;

led5 = 0;

end

else if (cs == `FETCHB)

begin

ram2dbus = 1;

dbus2ir = 1;

led4 = 0;

end

else if (cs == `EXECA)

begin

led2 = 0;

case (irout[15:12])

`PUSH:

begin

ir2dbus = 1;

dbus2qtop = 1;

push = 1;

end

`GET:

begin

ir2abus = 1;

cont = 1;

end

`SET:

begin

ir2abus = 1;

qtop2dbus = 1;

dbus2ram = 1;

pop = 1;

end

`JMP:

begin

ir2abus = 1;

abus2pc = 1;

end

`JZ:

begin

if (qtop == 0)

begin

ir2abus = 1;

abus2pc = 1;

end

pop = 1;

end

`JNZ:

begin

if (qtop != 0)

begin

ir2abus = 1;

abus2pc = 1;

end

pop = 1;

end

`OUT:

begin

qtop2dbus = 1;

dbus2obuf = 1;

pop = 1;

end

`OP:

begin

alu2dbus = 1;

dbus2qtop = 1;

if (irout[4] == 0)

begin

pop = 1;

end

end

default:

begin

//halt = 1;

end

endcase

end

else if (cs == `EXECB)

begin

if (irout[15:12] == `GET)

begin

ram2dbus = 1;

dbus2qtop = 1;

push = 1;

end

end

end

endmodule

以上。