概要

windowsでiverilogやってみた。

dma見つけたので、ベンチテスト書いてみた。

参考にしたページ

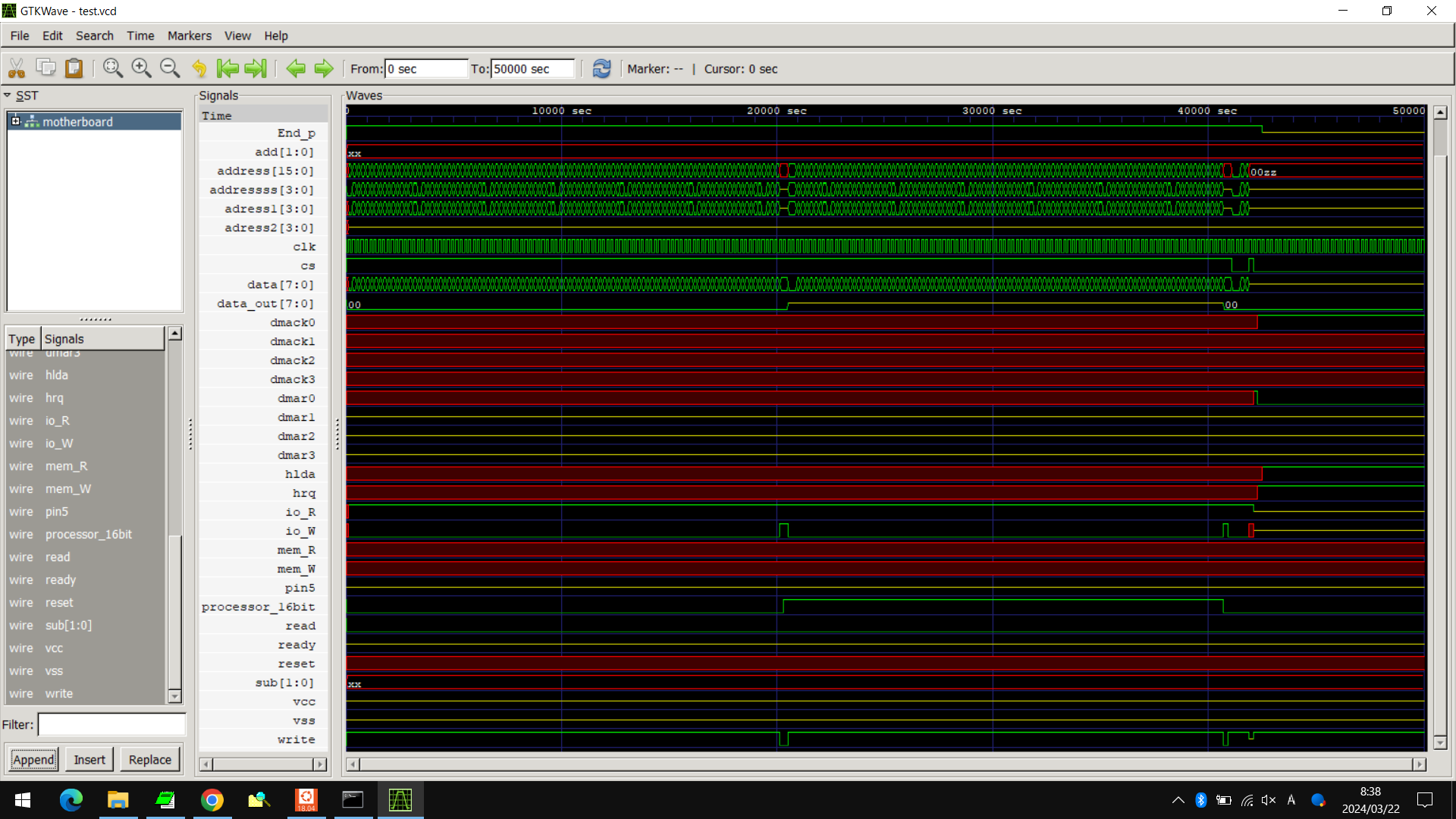

写真

サンプルコード

module motherboard();

wire [15:0] address;

wire [1:0] add,

sub;

wire [7:0] data,

data_out;

wire [3:0] adress1,

adress2,

addressss;

assign {address[7:4]} = adress2;

assign addressss = {address[3:0]};

assign {address[15:8]} = data_out;

clockgen c1(clk);

processor cpu1(address, read, write, data, clk, dmar0, dmack0, hrq, hlda, End_p, reset, processor_16bit);

DMA DD(add, sub, vcc, vss, clk, cs, reset, ready, hlda, dmar0, dmar1, dmar2, dmar3, data, io_R, io_W, End_p, adress1, adress2, hrq, dmack0, dmack1, dmack2, dmack3, Aen, Ad_strobe, mem_R, mem_W, pin5);

DMA_interface DD2(io_R, io_W, mem_R, mem_W, cs, address, read, write, dmar0, dmar1, dmar2, dmar3, dmack0, dmack1, dmack2, dmack3, clk, adress1, processor_16bit);

mem_interface mm1(read, write, address, data, clk);

IO1_interface d1(read, write, address, data, clk);

IO2_interface d2(read, write, address, data, clk);

latch l1(addressss, data, data_out, Aen, Ad_strobe, write, read, add, sub, processor_16bit);

initial

begin

$dumpfile("test.vcd");

$dumpvars(0, motherboard);

$display("read, write, address, data");

$monitor("%d %d %d %d", read, write, address, data);

#50000

$finish;

end

endmodule

実行結果

>vvp a.out

VCD info: dumpfile test.vcd opened for output.

read, write, address, data

0 1 X x

0 1 80 0

0 1 81 1

0 1 82 2

0 1 83 3

0 1 84 4

0 1 85 5

0 1 86 6

0 1 87 7

0 1 88 8

0 1 89 9

0 1 90 10

0 1 91 11

0 1 92 12

0 1 93 13

0 1 94 14

0 1 95 15

0 1 96 16

0 1 97 17

0 1 98 18

0 1 99 19

0 1 100 20

0 1 101 21

0 1 102 22

0 1 103 23

0 1 104 24

0 1 105 25

0 1 106 26

0 1 107 27

0 1 108 28

0 1 109 29

0 1 110 30

0 1 111 31

0 1 112 32

0 1 113 33

0 1 114 34

0 1 115 35

0 1 116 36

0 1 117 37

0 1 118 38

0 1 119 39

0 1 120 40

0 1 121 41

0 1 122 42

0 1 123 43

0 1 124 44

0 1 125 45

0 1 126 46

0 1 127 47

0 1 128 48

0 1 129 49

0 1 130 50

0 1 131 51

0 1 132 52

0 1 133 53

0 1 134 54

0 1 135 55

0 1 136 56

0 1 137 57

0 1 138 58

0 1 139 59

0 1 140 60

0 1 141 61

0 1 142 62

0 1 143 63

0 1 144 64

0 1 145 65

0 1 146 66

0 1 147 67

0 1 148 68

0 1 149 69

0 1 150 70

0 1 151 71

0 1 152 72

0 1 153 73

0 1 154 74

0 1 155 75

0 1 156 76

0 1 157 77

0 1 158 78

0 1 159 79

0 1 160 80

0 1 161 81

0 1 162 82

0 1 163 83

0 1 164 84

0 1 165 85

0 1 166 86

0 1 167 87

0 1 168 88

0 1 169 89

0 1 170 90

0 1 171 91

0 1 172 92

0 1 173 93

0 1 174 94

0 1 175 95

0 1 176 96

0 1 177 97

0 1 178 98

0 1 179 99

0 0 Z 100

0 1 280 0

0 1 281 1

0 1 282 2

0 1 283 3

0 1 284 4

0 1 285 5

0 1 286 6

0 1 287 7

0 1 288 8

0 1 289 9

0 1 290 10

0 1 291 11

0 1 292 12

0 1 293 13

0 1 294 14

0 1 295 15

0 1 296 16

0 1 297 17

0 1 298 18

0 1 299 19

0 1 300 20

0 1 301 21

0 1 302 22

0 1 303 23

0 1 304 24

0 1 305 25

0 1 306 26

0 1 307 27

0 1 308 28

0 1 309 29

0 1 310 30

0 1 311 31

0 1 312 32

0 1 313 33

0 1 314 34

0 1 315 35

0 1 316 36

0 1 317 37

0 1 318 38

0 1 319 39

0 1 320 40

0 1 321 41

0 1 322 42

0 1 323 43

0 1 324 44

0 1 325 45

0 1 326 46

0 1 327 47

0 1 328 48

0 1 329 49

0 1 330 50

0 1 331 51

0 1 332 52

0 1 333 53

0 1 334 54

0 1 335 55

0 1 336 56

0 1 337 57

0 1 338 58

0 1 339 59

0 1 340 60

0 1 341 61

0 1 342 62

0 1 343 63

0 1 344 64

0 1 345 65

0 1 346 66

0 1 347 67

0 1 348 68

0 1 349 69

0 1 350 70

0 1 351 71

0 1 352 72

0 1 353 73

0 1 354 74

0 1 355 75

0 1 356 76

0 1 357 77

0 1 358 78

0 1 359 79

0 1 360 80

0 1 361 81

0 1 362 82

0 1 363 83

0 1 364 84

0 1 365 85

0 1 366 86

0 1 367 87

0 1 368 88

0 1 369 89

0 1 370 90

0 1 371 91

0 1 372 92

0 1 373 93

0 1 374 94

0 1 375 95

0 1 376 96

0 1 377 97

0 1 378 98

0 1 379 99

0 0 Z 100

0 1 Z 100

0 1 0 0

0 1 2 110

0 1 4 20

0 z Z z

0 1 Z z

0 1 Z z

dma.v:1893: $finish called at 50000 (1s)

以上。