概要

vistaでquartusやってみた。

serialに、fifoとoneshotを導入してみた。

環境

windows vista 32bit

quartus ii v13.0

ep2c5t144ボード

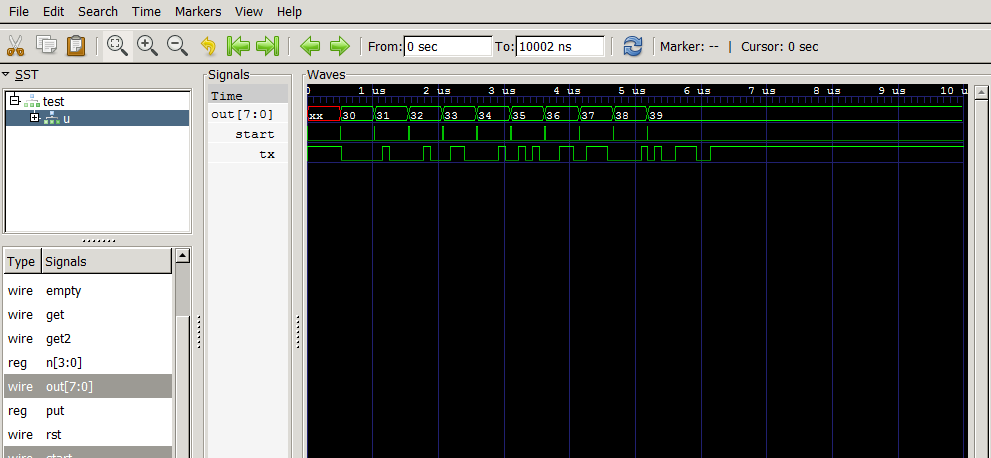

iverilog実行結果

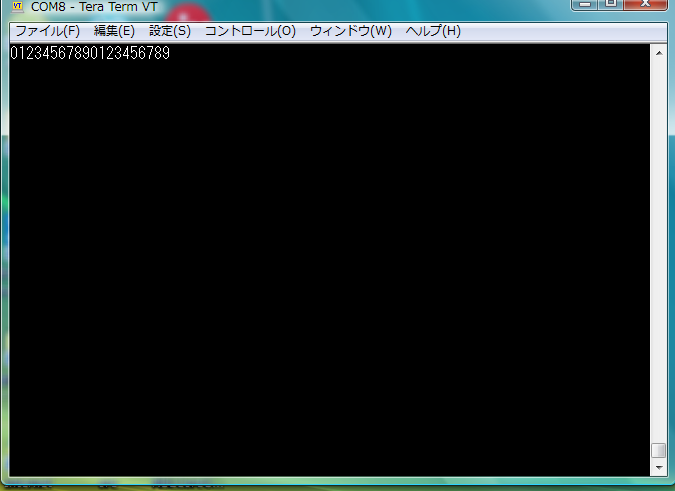

写真

サンプルコード

`timescale 1ns / 1ps

module fifo(input clk, input rst, input put, input get, input [7:0] data, output reg [7:0] out, output empty, output reg start);

reg [7:0] mem[32:0];

reg [4:0] rd_pos;

reg [4:0] wr_pos;

assign empty = ((wr_pos - rd_pos) == 0) ? 1'b1 : 1'b0;

assign full = ((wr_pos - rd_pos) == 32) ? 1'b1 : 1'b0;

always @(posedge clk or negedge rst)

begin

if (!rst)

begin

wr_pos <= 0;

rd_pos <= 0;

start <= 0;

end

else

begin

if (put & full == 1'b0)

begin

mem[wr_pos] <= data;

wr_pos <= wr_pos + 1;

end

if (get & empty == 1'b0)

begin

out <= mem[rd_pos];

rd_pos <= rd_pos + 1;

start <= 1;

end

else

begin

start <= 0;

end

end

end

endmodule

module oneshot(input clk, input rst, input in, output reg out);

reg prev = 0;

always @(posedge clk)

begin

if (in ^ prev)

out <= in;

else

out <= 0;

prev <= in;

end

endmodule

module test2(input clk, input rst, output tx);

localparam NEXT = 4'b0000;

localparam DONE = 4'b1111;

wire [7:0] out;

reg [3:0] n = 0;

reg [7:0] char;

reg [3:0] state = NEXT;

reg put = 0;

tx2 tx2(.clk(clk), .rst(rst), .start(start), .data(out), .tx(tx), .busy(busy), .get(get));

oneshot one0(.clk(clk), .rst(rst), .in(get), .out(get2));

fifo fifo0(.clk(clk), .rst(rst), .put(put), .get(get2), .data(char), .out(out), .empty(empty), .start(start));

always @(posedge clk or negedge rst)

begin

if (!rst)

begin

state <= NEXT;

n <= 0;

end

else if (put)

begin

put <= 0;

end

else if (state == NEXT)

begin

state <= 1;

end

else if (state != DONE)

begin

if (n == 10)

begin

state <= DONE;

end

else

begin

char <= 48 + n;

put <= 1;

n <= n + 1;

end

end

end

endmodule

module test;

reg clk,

rst;

test2 u(.clk(clk), .rst(rst), .tx(tx));

initial

begin

clk = 0;

rst = 1;

#1

rst = 0;

#1

rst = 1;

#10000

$finish;

end

always

begin

#1

clk = ~clk;

end

initial

begin

$dumpfile("test.vcd");

$dumpvars(0, u);

end

endmodule

以上。