第4話 CPU毎のマザーボード構成

"自作の組込みマザーボードを作って自作のコンピュータを作りたい"

第1話は以下より

https://qiita.com/nonNoise/items/c4800ac35c529c04e941

第2話は以下より

https://qiita.com/nonNoise/items/01427a281ceb7bdc0238

第3話は以下より

https://qiita.com/nonNoise/items/e4bcb08c4e86ab87d0d5

CPU毎のマザーボード構成

早速、CPU毎に実際にマザーボードの構成を考えていきたいと思います。

その前に、SiPについておさらいをしておきます。

なぜSiPにしたのか

SiP(System in Package)については第1話で触れていますが、

ここでは、なぜSiPにしたのかを話します。

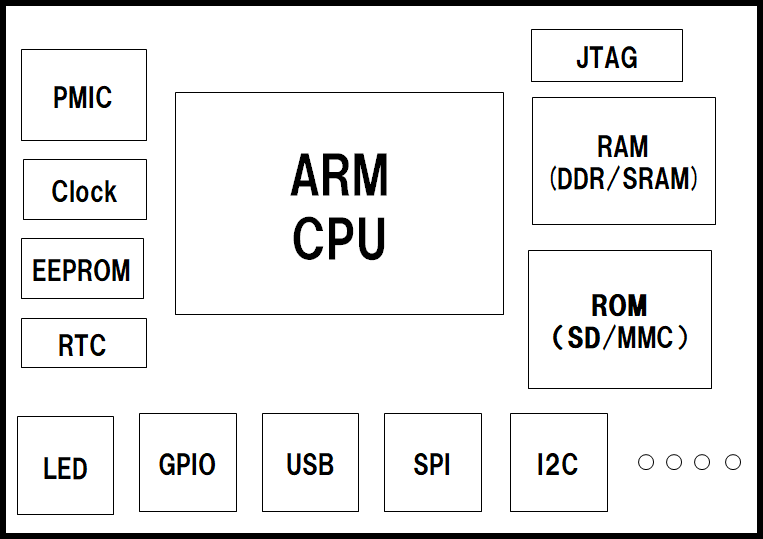

第3章で語りました、マザーボードの構成を再び見ていきましょう。

この構成のうち、基板設計で最難所はDDRメモリの部分だったりします。

http://ww1.microchip.com/downloads/jp/AppNotes/00002717A_JP.pdf

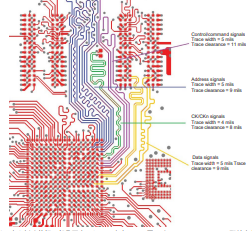

DDR系のメモリは等長配線という技を使います。

等長配線は、同じ長さで配線するという意味です。

DDRは差動で動作するピンや、タイミングがシビアなピンが多く、長さを合わせることで同期しやすい回路になります。

長さを合わせるために、こう、グネグネした配線を行います。お互いが同じ長さになるように少し遠回りして合わせるといった形です。

この等長配線を行うのは、ものすっごく大変(とはいえ高級CADで可能となりましたが)であり、

実際に配線できても、動作するかどうか不安が多い点です。

このDDRの配線さえ無くしてしまえば基板はもっと簡単に作ることが出来る。そういうシナリオです。

そんなシナリオを元に、配線が大変なものはチップ内部に入れてしまえという形で、SiPが登場しました。

皆さん忘れているかもしれませんが、RaspberryPiも同様に、メモリ配線を省略した基板であることが多いです。

SiPとは言いませんが、別の仕組みで、CPUとRAMを結合したチップを使用しています。

まぁ、わかるように、DDRメモリの配線はクッソ疲れます。

そういった疲れる部分を肩代わりしてるのが、SiPのいいところです。

SiPの内部構成

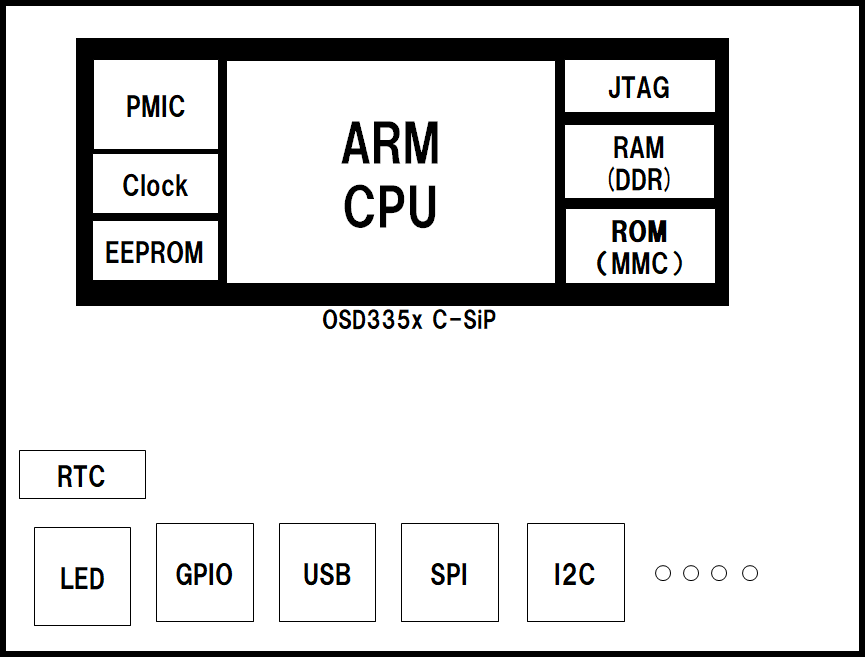

OSD335x C-SiPの場合

ほとんどの機能が、SiPによりチップ内部に封入されています。

そのため、外部に必要な回路や部品が少なく、その他のインターフェースに力を集中することが出来ます。

これは大変すばらしく、得意としている分野に特化することが出来ます。

ただ、値段が高いという難点があります。これが安くなれば幸せですが、そうも成りそうもありません。

値段が高い点を見るに、この状態は、かなり特殊な状態と思われます。

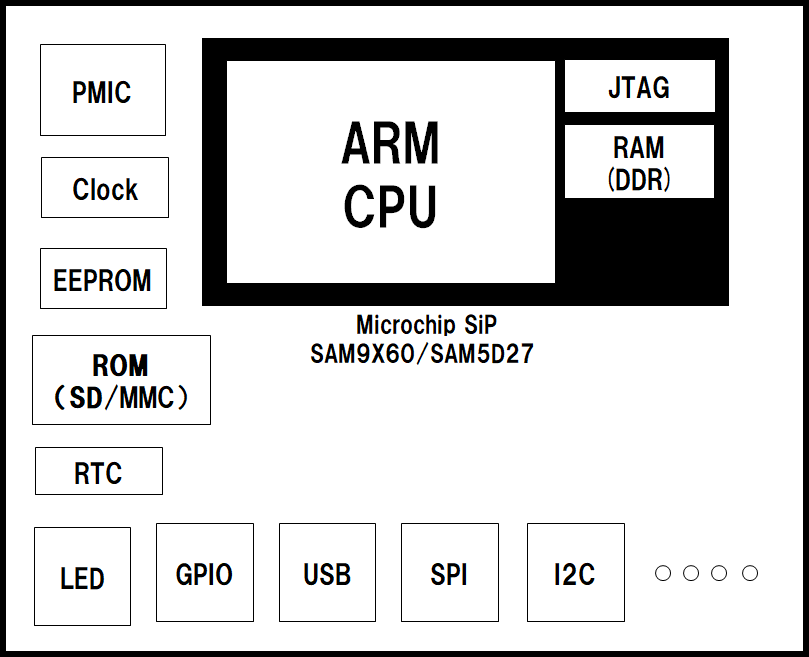

SAMA5D2とSAM9X60の場合

逆に、本当にDDRメモリの部分のみチップに封入するメーカーもいます。

まぁ、値段が本当に安いので、チップ単品との差が数百円ですので、SiPパッケージを使った方がむしろ良い状態です。

ただ、DDRメモリの次に難易度が高いPMICが外部に出ている為、その辺は頑張りどころです。

安い点や小さい点も含め、非常に小回りが利くので、自分としてはこの当たりのチップは気に入っています。

マザーボード構成 まとめ

さて、SiPにより大半の機能がワンチップで実現されているため、あとは残りの機能を実現して下れば、自作マザボの完成です。

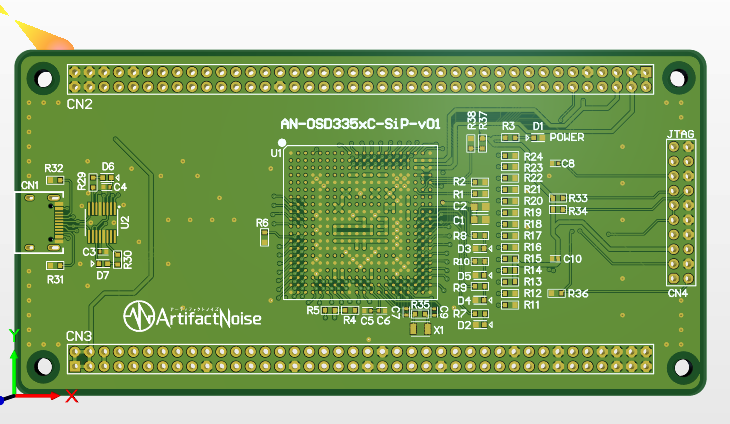

今回、記事を書きながらですが、基板設計も同時に行っています。

このボードは、意味合い的にはマザーボードではありません。CPUボードと呼んだり、CPUモジュールと呼んだりします。

本当は、1枚のボードで納めてマザーボードと言いますが、マザーボードを作るうえで気にしなければならない点が多く

今回は、CPUをちゃんと動かすバージョンの基板と、1枚に収めたマザーボードを作るの二部構成で進めていこうかなと思います。

というのも、この先の話には、U-BootやLinuxの話もあり、基板や配線どころの問題ではない点が多いので、

後段にある大きな敵と戦うために、今は被害を最小限にしたテスト用の基板を作るという戦略をとりたいとおもいます。

次回・・・

そろそろ、ちゃんと基板設計を進めないとネタがない汗

とりあえず、現在の基板設計で必要となるベースの話が出来てよかった。

ここから先は、時間がかかるので、二週間~三週間程度お待ちいただければと思います。

ではでは。