やること

GHRDはいっぱい入っててすごいんだけど、構成がよくわからない。最小限の構成から始めたいところ。

linux等のソフトはGHRDを使って、FPGAだけ最小構成で作ってみる。

ハードはCPUとLEDをつける独自コンポーネントだけ。

バスは簡単に作れそうなAvalon-MMを使うことにした。

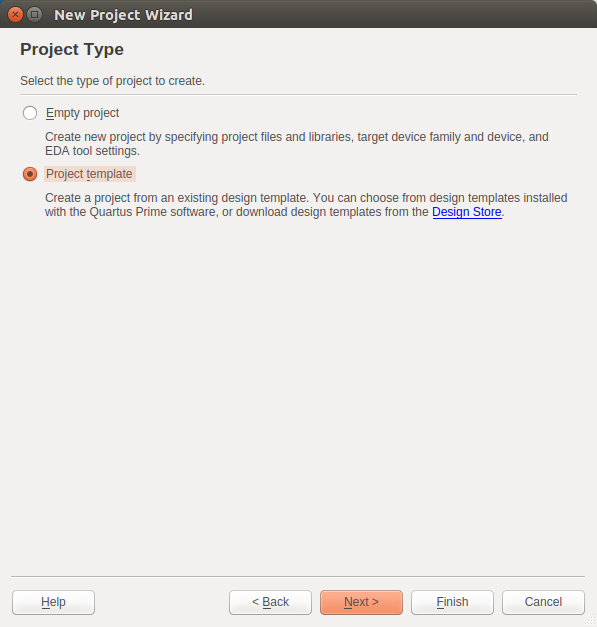

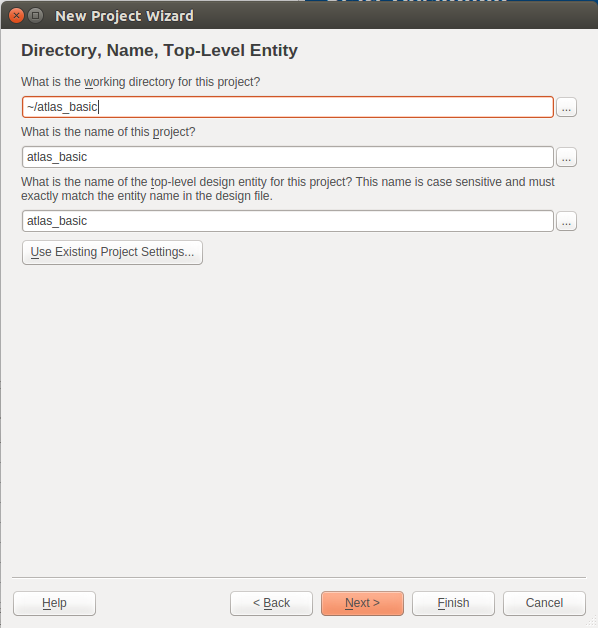

プロジェクトの作成

Quartusを起動して、メニューから

FILE-New Project Wizard..

を実行

プロジェクト名はatlas_basicとした。

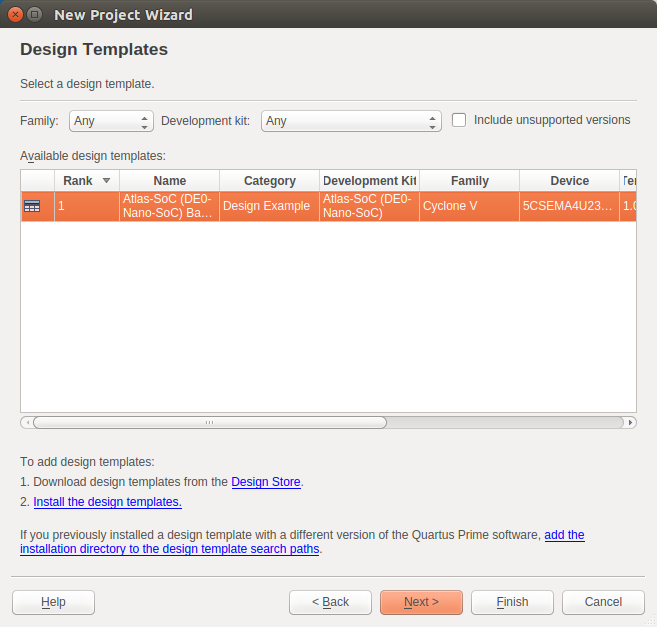

プロジェクトテンプレートを使うとピンアサインとか設定しなくていいので楽。

テンプレートはAlteraのHPからダウンロードすることができる。

TOPも自動でできる。

//--------------------------------------------------------------------------//

// Title: de0_nano_soc_baseline.v //

// Rev: Rev 0.1 //

// Last Revised: 09/14/2015 //

//--------------------------------------------------------------------------//

// Description: Baseline design file contains DE0 Nano SoC //

// Board pins and I/O Standards. //

//--------------------------------------------------------------------------//

//Copyright 2015 Altera Corporation. All rights reserved. Altera products

//are protected under numerous U.S. and foreign patents, maskwork rights,

//copyrights and other intellectual property laws.

//

//This reference design file, and your use thereof, is subject to and

//governed by the terms and conditions of the applicable Altera Reference

//Design License Agreement. By using this reference design file, you

//indicate your acceptance of such terms and conditions between you and

//Altera Corporation. In the event that you do not agree with such terms and

//conditions, you may not use the reference design file. Please promptly

//destroy any copies you have made.

//

//This reference design file being provided on an "as-is" basis and as an

//accommodation and therefore all warranties, representations or guarantees

//of any kind (whether express, implied or statutory) including, without

//limitation, warranties of merchantability, non-infringement, or fitness for

//a particular purpose, are specifically disclaimed. By making this

//reference design file available, Altera expressly does not recommend,

//suggest or require that this reference design file be used in combination

//with any other product not provided by Altera

//----------------------------------------------------------------------------

//Group Enable Definitions

//This lists every pinout group

//Users can enable any group by uncommenting the corresponding line below:

//`define enable_ADC

//`define enable_ARDUINO

//`define enable_GPIO0

//`define enable_GPIO1

//`define enable_HPS

module de0_nano_soc_baseline(

//////////// CLOCK //////////

input FPGA_CLK_50,

input FPGA_CLK2_50,

input FPGA_CLK3_50,

`ifdef enable_ADC

//////////// ADC //////////

/* 3.3-V LVTTL */

output ADC_CONVST,

output ADC_SCLK,

output ADC_SDI,

input ADC_SDO,

`endif

`ifdef enable_ARDUINO

//////////// ARDUINO ////////////

/* 3.3-V LVTTL */

inout [15:0] ARDUINO_IO,

inout ARDUINO_RESET_N,

`endif

`ifdef enable_GPIO0

//////////// GPIO 0 ////////////

/* 3.3-V LVTTL */

inout [35:0] GPIO_0,

`endif

`ifdef enable_GPIO1

//////////// GPIO 1 ////////////

/* 3.3-V LVTTL */

inout [35:0] GPIO_1,

`endif

`ifdef enable_HPS

//////////// HPS //////////

/* 3.3-V LVTTL */

inout HPS_CONV_USB_N,

/* SSTL-15 Class I */

output [14:0] HPS_DDR3_ADDR,

output [2:0] HPS_DDR3_BA,

output HPS_DDR3_CAS_N,

output HPS_DDR3_CKE,

output HPS_DDR3_CS_N,

output [3:0] HPS_DDR3_DM,

inout [31:0] HPS_DDR3_DQ,

output HPS_DDR3_ODT,

output HPS_DDR3_RAS_N,

output HPS_DDR3_RESET_N,

input HPS_DDR3_RZQ,

output HPS_DDR3_WE_N,

/* DIFFERENTIAL 1.5-V SSTL CLASS I */

output HPS_DDR3_CK_N,

output HPS_DDR3_CK_P,

inout [3:0] HPS_DDR3_DQS_N,

inout [3:0] HPS_DDR3_DQS_P,

/* 3.3-V LVTTL */

output HPS_ENET_GTX_CLK,

inout HPS_ENET_INT_N,

output HPS_ENET_MDC,

inout HPS_ENET_MDIO,

input HPS_ENET_RX_CLK,

input [3:0] HPS_ENET_RX_DATA,

input HPS_ENET_RX_DV,

output [3:0] HPS_ENET_TX_DATA,

output HPS_ENET_TX_EN,

inout HPS_GSENSOR_INT,

inout HPS_I2C0_SCLK,

inout HPS_I2C0_SDAT,

inout HPS_I2C1_SCLK,

inout HPS_I2C1_SDAT,

inout HPS_KEY,

inout HPS_LED,

inout HPS_LTC_GPIO,

output HPS_SD_CLK,

inout HPS_SD_CMD,

inout [3:0] HPS_SD_DATA,

output HPS_SPIM_CLK,

input HPS_SPIM_MISO,

output HPS_SPIM_MOSI,

inout HPS_SPIM_SS,

input HPS_UART_RX,

output HPS_UART_TX,

input HPS_USB_CLKOUT,

inout [7:0] HPS_USB_DATA,

input HPS_USB_DIR,

input HPS_USB_NXT,

output HPS_USB_STP,

`endif

//////////// KEY ////////////

/* 3.3-V LVTTL */

input [1:0] KEY,

//////////// LED ////////////

/* 3.3-V LVTTL */

output [7:0] LED,

//////////// SW ////////////

/* 3.3-V LVTTL */

input [3:0] SW

);

endmodule

これは後で変更しよう。

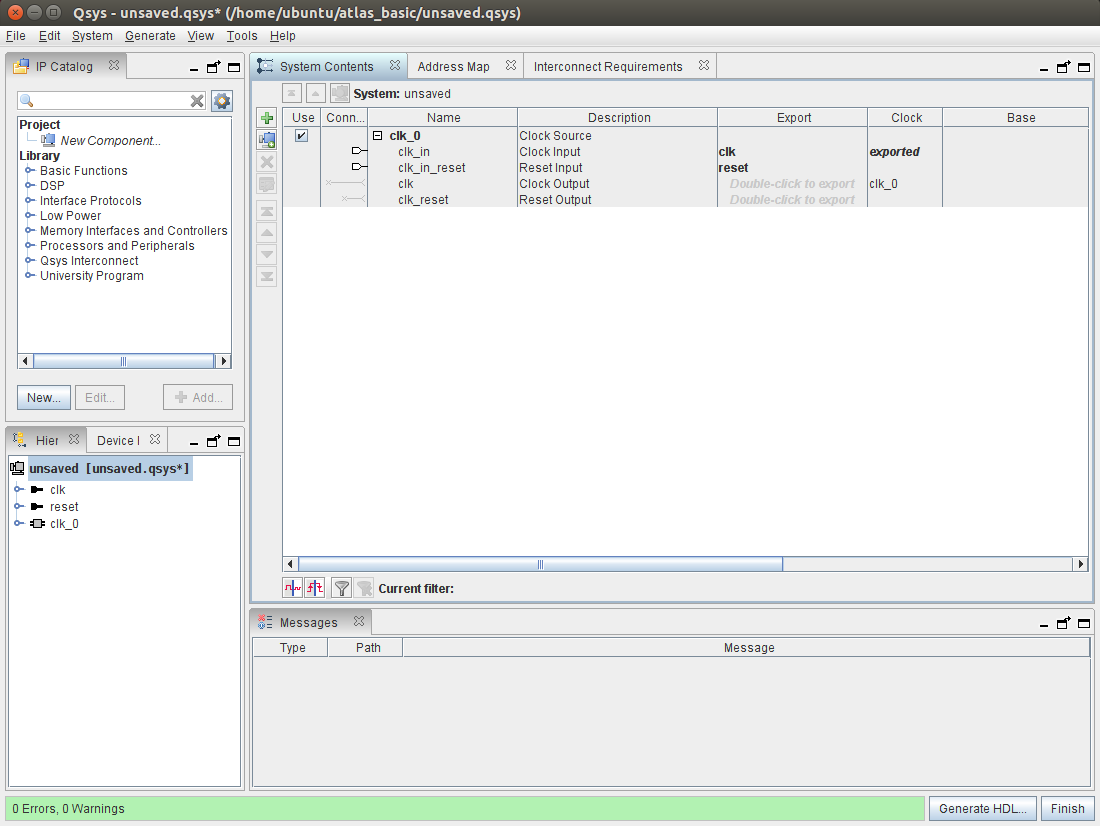

HPSの追加

こんな画面のQsysが起動して、clk_0が最初から入ってる。clk_0の使い方が分からなくて(勉強不足)、clkが出ないのでとってしまう。clk_0を選択してDELキーを押して削除する。

IP CatalogのサーチにHPSと入力して

Arria V/Cyclon V Hard Processor System

を探してAddする。

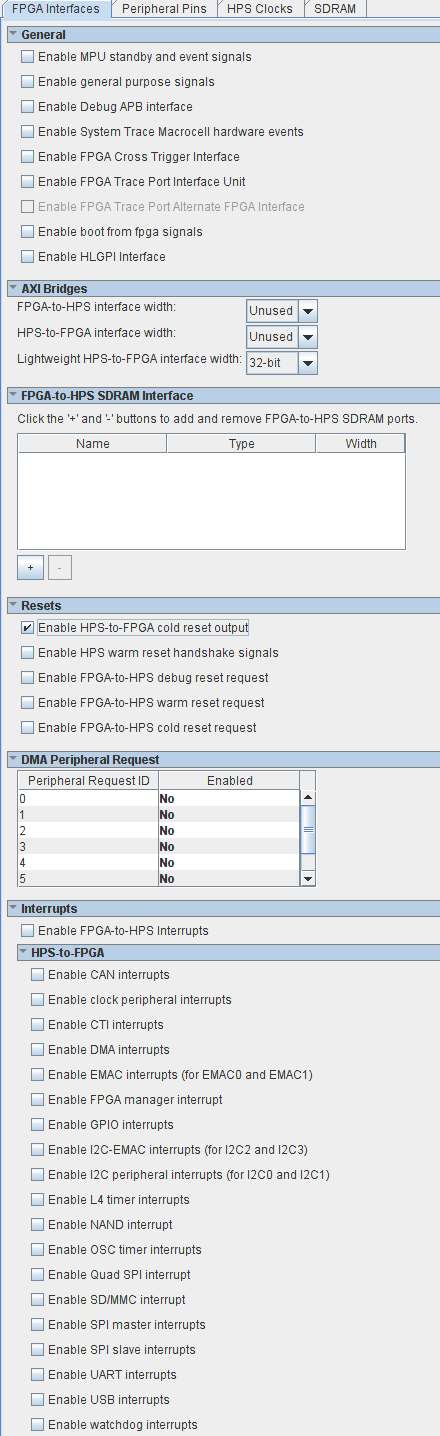

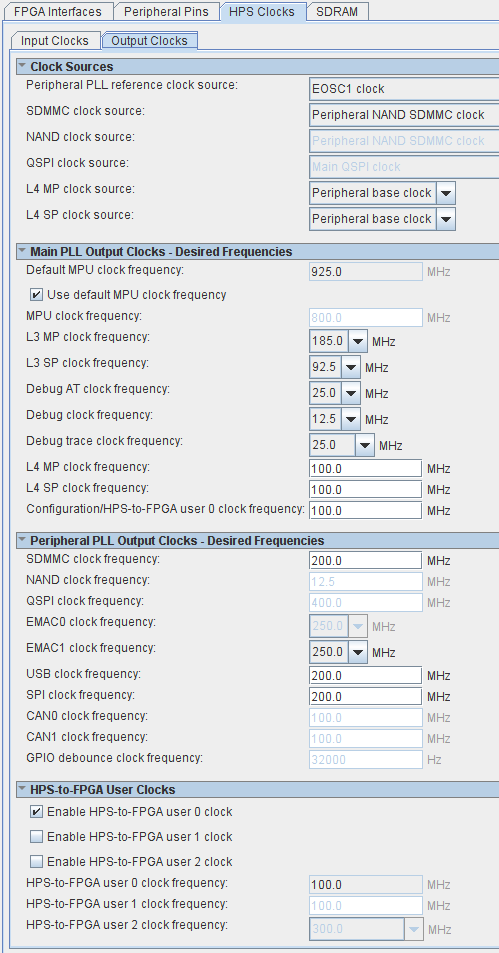

hps_0の設定をする。

Lightweight HPS-to-FPGA intrefaceだけつかう。32bitにする。

cold resetもだしておこう。他はOFFにする。

クロックも出しておく。

他はGHRDの設定を見ながら同じように設定する。1個1個設定を変える度にツールが固まるので結構面倒くさい。SDRAMの設定を間違うとCPUが起動しないかもしれない。注意して合わせる。

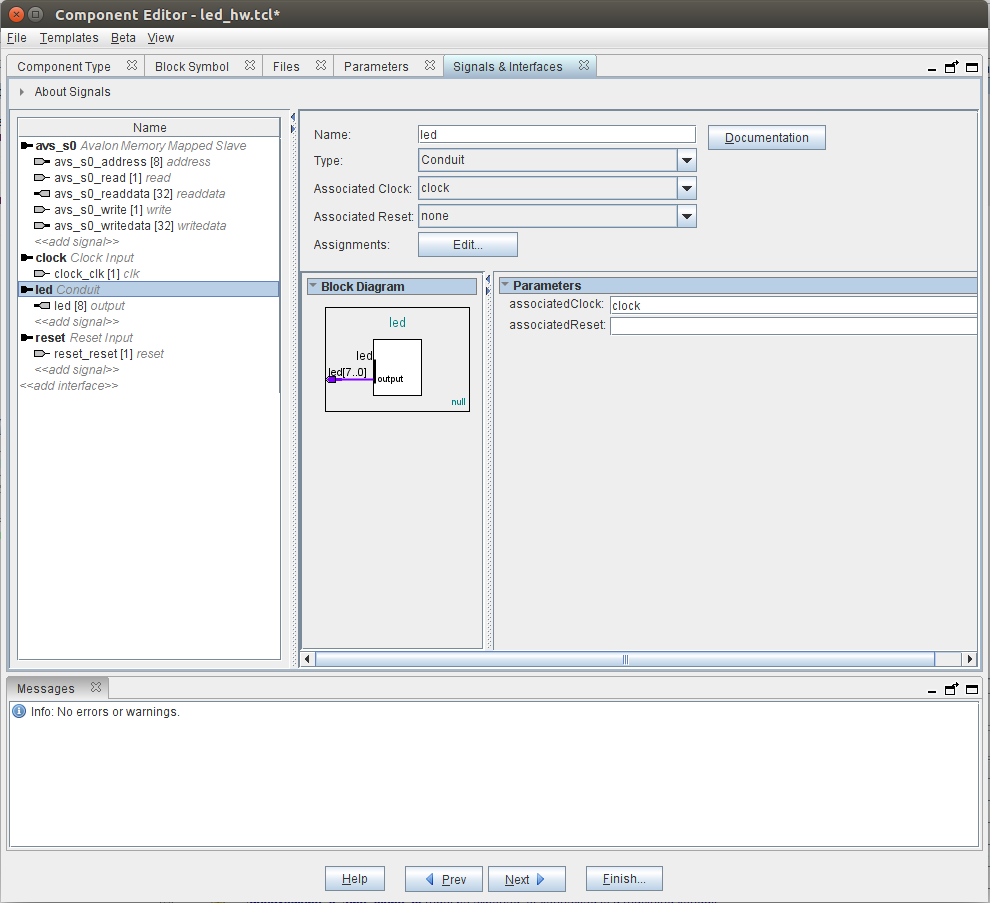

カスタムコンポーネントの作成

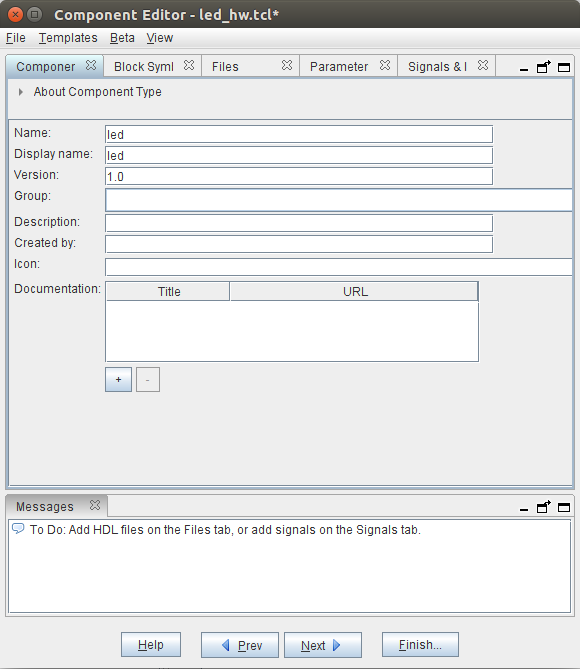

LEDを制御するカスタムコンポーネントを作成する。これもテンプレートを利用する。IP CatalogからProject-New Component..をクリックする。

コンポーネント名は簡単にledとした

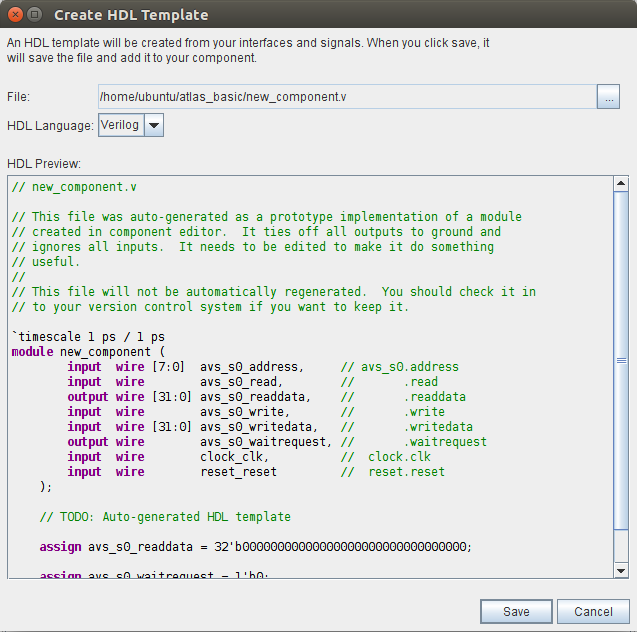

FilesタブをクリックするCreate Synthesis File from Signalsがグレーアウトされているのでメニューから

Templates - Add Avalon-MM Simple Slave

を実行する。(何もかわらないとおもって2回実行してはいけない)

するとCreate Synthesis File from Signalsが押せるようになるので押す。

Saveを押すとnew_component.vができる。ファイル名は変えれないみたい。Synthesis Filesリストに追加されるが、ファイル名を変えたいのでいったんRemove Fileを押して削除しておく。

テンプレートの内容は以下のようになっていた。

// new_component.v

// This file was auto-generated as a prototype implementation of a module

// created in component editor. It ties off all outputs to ground and

// ignores all inputs. It needs to be edited to make it do something

// useful.

//

// This file will not be automatically regenerated. You should check it in

// to your version control system if you want to keep it.

`timescale 1 ps / 1 ps

module new_component (

input wire [7:0] avs_s0_address, // avs_s0.address

input wire avs_s0_read, // .read

output wire [31:0] avs_s0_readdata, // .readdata

input wire avs_s0_write, // .write

input wire [31:0] avs_s0_writedata, // .writedata

output wire avs_s0_waitrequest, // .waitrequest

input wire clock_clk, // clock.clk

input wire reset_reset // reset.reset

);

// TODO: Auto-generated HDL template

assign avs_s0_readdata = 32'b00000000000000000000000000000000;

assign avs_s0_waitrequest = 1'b0;

endmodule

普通のフォルダを使ってled.vにファイル名を変更。

geditで以下のように変えた。

// new_component.v

// This file was auto-generated as a prototype implementation of a module

// created in component editor. It ties off all outputs to ground and

// ignores all inputs. It needs to be edited to make it do something

// useful.

//

// This file will not be automatically regenerated. You should check it in

// to your version control system if you want to keep it.

`timescale 1 ps / 1 ps

module new_component (

input wire [7:0] avs_s0_address, // avs_s0.address

input wire avs_s0_read, // .read

output reg [31:0] avs_s0_readdata, // .readdata

input wire avs_s0_write, // .write

input wire [31:0] avs_s0_writedata, // .writedata

input wire clock_clk, // clock.clk

input wire reset_reset, // reset.reset

output reg [7:0] led // led output

);

always @(posedge clock_clk)

begin

avs_s0_readdata <= {24'b0, led};

end

always @(posedge clock_clk)

begin

if(reset_reset)

led <= 8'b0;

else if(avs_s0_write)

led <= avs_s0_writedata[7:0];

else

led <= led;

end

endmodule

waitrequestは使わなくてもきそうなので削除した。

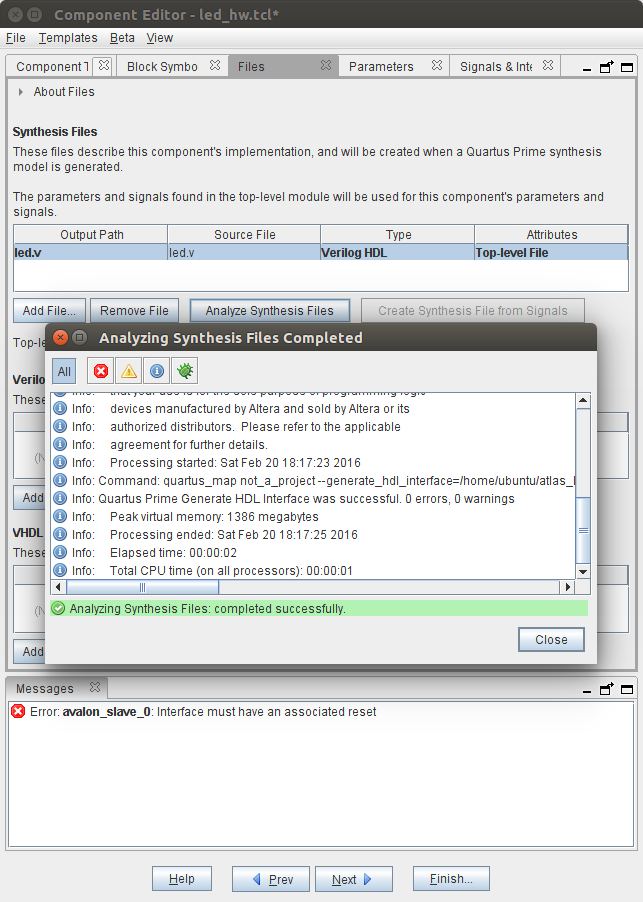

Add File..ボタンを使って作ったled.vを追加する。

Analyze Synthesis Filesを押すと解析が始まる。

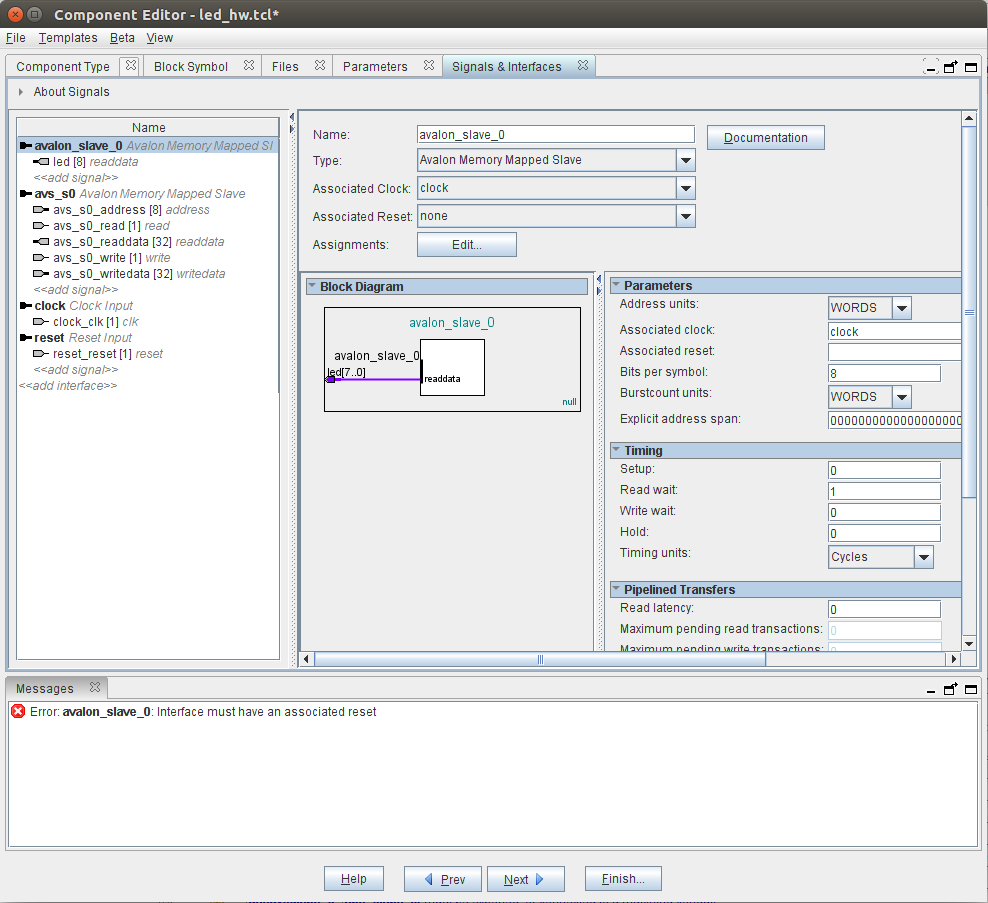

ほとんど解析は当たってるんだけど、ledだけ外れ。

add interfaceをクリックしてconduitを作って、ledをその下にドラッグする。

Finishを押す。

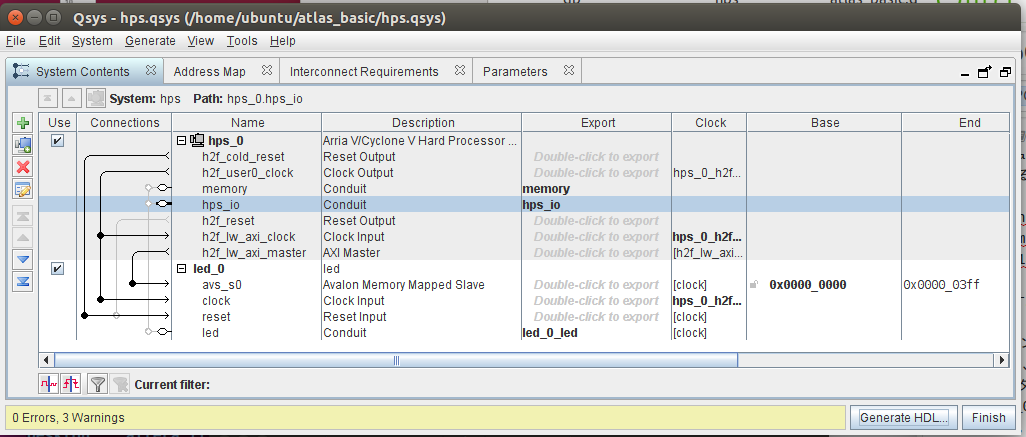

コンポーネントの接続

Qsysに戻って、IP CatalogウィンドウのProjectの下にledができてるのでダブルクリックで追加する。

hps_0とled_0をつなげて、ledはExport Asを使ってモジュールから外に出す。

メニューからSave asでファイル名をつけておこう。hps.qsysとした。

使うコンポーネントははこれだけ。

左下のGenerate HDLボタンを押すと処理が始まる。

メニューから

Generate - Show Instantiation Template

を実行するとインスタンスのテンプレートが出てくる。TOPに書くサンプル。

hps u0 (

.led_0_led_output (<connected-to-led_0_led_output>), // led_0_led.output

.memory_mem_a (<connected-to-memory_mem_a>), // memory.mem_a

.memory_mem_ba (<connected-to-memory_mem_ba>), // .mem_ba

.memory_mem_ck (<connected-to-memory_mem_ck>), // .mem_ck

.memory_mem_ck_n (<connected-to-memory_mem_ck_n>), // .mem_ck_n

.memory_mem_cke (<connected-to-memory_mem_cke>), // .mem_cke

.memory_mem_cs_n (<connected-to-memory_mem_cs_n>), // .mem_cs_n

.memory_mem_ras_n (<connected-to-memory_mem_ras_n>), // .mem_ras_n

.memory_mem_cas_n (<connected-to-memory_mem_cas_n>), // .mem_cas_n

.memory_mem_we_n (<connected-to-memory_mem_we_n>), // .mem_we_n

.memory_mem_reset_n (<connected-to-memory_mem_reset_n>), // .mem_reset_n

.memory_mem_dq (<connected-to-memory_mem_dq>), // .mem_dq

.memory_mem_dqs (<connected-to-memory_mem_dqs>), // .mem_dqs

.memory_mem_dqs_n (<connected-to-memory_mem_dqs_n>), // .mem_dqs_n

.memory_mem_odt (<connected-to-memory_mem_odt>), // .mem_odt

.memory_mem_dm (<connected-to-memory_mem_dm>), // .mem_dm

.memory_oct_rzqin (<connected-to-memory_oct_rzqin>), // .oct_rzqin

.hps_io_hps_io_emac1_inst_TX_CLK (<connected-to-hps_io_hps_io_emac1_inst_TX_CLK>), // hps_io.hps_io_emac1_inst_TX_CLK

.hps_io_hps_io_emac1_inst_TXD0 (<connected-to-hps_io_hps_io_emac1_inst_TXD0>), // .hps_io_emac1_inst_TXD0

.hps_io_hps_io_emac1_inst_TXD1 (<connected-to-hps_io_hps_io_emac1_inst_TXD1>), // .hps_io_emac1_inst_TXD1

.hps_io_hps_io_emac1_inst_TXD2 (<connected-to-hps_io_hps_io_emac1_inst_TXD2>), // .hps_io_emac1_inst_TXD2

.hps_io_hps_io_emac1_inst_TXD3 (<connected-to-hps_io_hps_io_emac1_inst_TXD3>), // .hps_io_emac1_inst_TXD3

.hps_io_hps_io_emac1_inst_RXD0 (<connected-to-hps_io_hps_io_emac1_inst_RXD0>), // .hps_io_emac1_inst_RXD0

.hps_io_hps_io_emac1_inst_MDIO (<connected-to-hps_io_hps_io_emac1_inst_MDIO>), // .hps_io_emac1_inst_MDIO

.hps_io_hps_io_emac1_inst_MDC (<connected-to-hps_io_hps_io_emac1_inst_MDC>), // .hps_io_emac1_inst_MDC

.hps_io_hps_io_emac1_inst_RX_CTL (<connected-to-hps_io_hps_io_emac1_inst_RX_CTL>), // .hps_io_emac1_inst_RX_CTL

.hps_io_hps_io_emac1_inst_TX_CTL (<connected-to-hps_io_hps_io_emac1_inst_TX_CTL>), // .hps_io_emac1_inst_TX_CTL

.hps_io_hps_io_emac1_inst_RX_CLK (<connected-to-hps_io_hps_io_emac1_inst_RX_CLK>), // .hps_io_emac1_inst_RX_CLK

.hps_io_hps_io_emac1_inst_RXD1 (<connected-to-hps_io_hps_io_emac1_inst_RXD1>), // .hps_io_emac1_inst_RXD1

.hps_io_hps_io_emac1_inst_RXD2 (<connected-to-hps_io_hps_io_emac1_inst_RXD2>), // .hps_io_emac1_inst_RXD2

.hps_io_hps_io_emac1_inst_RXD3 (<connected-to-hps_io_hps_io_emac1_inst_RXD3>), // .hps_io_emac1_inst_RXD3

.hps_io_hps_io_sdio_inst_CMD (<connected-to-hps_io_hps_io_sdio_inst_CMD>), // .hps_io_sdio_inst_CMD

.hps_io_hps_io_sdio_inst_D0 (<connected-to-hps_io_hps_io_sdio_inst_D0>), // .hps_io_sdio_inst_D0

.hps_io_hps_io_sdio_inst_D1 (<connected-to-hps_io_hps_io_sdio_inst_D1>), // .hps_io_sdio_inst_D1

.hps_io_hps_io_sdio_inst_CLK (<connected-to-hps_io_hps_io_sdio_inst_CLK>), // .hps_io_sdio_inst_CLK

.hps_io_hps_io_sdio_inst_D2 (<connected-to-hps_io_hps_io_sdio_inst_D2>), // .hps_io_sdio_inst_D2

.hps_io_hps_io_sdio_inst_D3 (<connected-to-hps_io_hps_io_sdio_inst_D3>), // .hps_io_sdio_inst_D3

.hps_io_hps_io_usb1_inst_D0 (<connected-to-hps_io_hps_io_usb1_inst_D0>), // .hps_io_usb1_inst_D0

.hps_io_hps_io_usb1_inst_D1 (<connected-to-hps_io_hps_io_usb1_inst_D1>), // .hps_io_usb1_inst_D1

.hps_io_hps_io_usb1_inst_D2 (<connected-to-hps_io_hps_io_usb1_inst_D2>), // .hps_io_usb1_inst_D2

.hps_io_hps_io_usb1_inst_D3 (<connected-to-hps_io_hps_io_usb1_inst_D3>), // .hps_io_usb1_inst_D3

.hps_io_hps_io_usb1_inst_D4 (<connected-to-hps_io_hps_io_usb1_inst_D4>), // .hps_io_usb1_inst_D4

.hps_io_hps_io_usb1_inst_D5 (<connected-to-hps_io_hps_io_usb1_inst_D5>), // .hps_io_usb1_inst_D5

.hps_io_hps_io_usb1_inst_D6 (<connected-to-hps_io_hps_io_usb1_inst_D6>), // .hps_io_usb1_inst_D6

.hps_io_hps_io_usb1_inst_D7 (<connected-to-hps_io_hps_io_usb1_inst_D7>), // .hps_io_usb1_inst_D7

.hps_io_hps_io_usb1_inst_CLK (<connected-to-hps_io_hps_io_usb1_inst_CLK>), // .hps_io_usb1_inst_CLK

.hps_io_hps_io_usb1_inst_STP (<connected-to-hps_io_hps_io_usb1_inst_STP>), // .hps_io_usb1_inst_STP

.hps_io_hps_io_usb1_inst_DIR (<connected-to-hps_io_hps_io_usb1_inst_DIR>), // .hps_io_usb1_inst_DIR

.hps_io_hps_io_usb1_inst_NXT (<connected-to-hps_io_hps_io_usb1_inst_NXT>), // .hps_io_usb1_inst_NXT

.hps_io_hps_io_spim1_inst_CLK (<connected-to-hps_io_hps_io_spim1_inst_CLK>), // .hps_io_spim1_inst_CLK

.hps_io_hps_io_spim1_inst_MOSI (<connected-to-hps_io_hps_io_spim1_inst_MOSI>), // .hps_io_spim1_inst_MOSI

.hps_io_hps_io_spim1_inst_MISO (<connected-to-hps_io_hps_io_spim1_inst_MISO>), // .hps_io_spim1_inst_MISO

.hps_io_hps_io_spim1_inst_SS0 (<connected-to-hps_io_hps_io_spim1_inst_SS0>), // .hps_io_spim1_inst_SS0

.hps_io_hps_io_uart0_inst_RX (<connected-to-hps_io_hps_io_uart0_inst_RX>), // .hps_io_uart0_inst_RX

.hps_io_hps_io_uart0_inst_TX (<connected-to-hps_io_hps_io_uart0_inst_TX>), // .hps_io_uart0_inst_TX

.hps_io_hps_io_i2c0_inst_SDA (<connected-to-hps_io_hps_io_i2c0_inst_SDA>), // .hps_io_i2c0_inst_SDA

.hps_io_hps_io_i2c0_inst_SCL (<connected-to-hps_io_hps_io_i2c0_inst_SCL>), // .hps_io_i2c0_inst_SCL

.hps_io_hps_io_i2c1_inst_SDA (<connected-to-hps_io_hps_io_i2c1_inst_SDA>), // .hps_io_i2c1_inst_SDA

.hps_io_hps_io_i2c1_inst_SCL (<connected-to-hps_io_hps_io_i2c1_inst_SCL>) // .hps_io_i2c1_inst_SCL

);

コピーしておく。

TOPの変更

Quartusに戻ってTOPを編集する。

先ほどコピーしたサンプルを張り付けてピン定義と似ているものを探して接続する。ピンが結構多いので大変。

//--------------------------------------------------------------------------//

// Title: de0_nano_soc_baseline.v //

// Rev: Rev 0.1 //

// Last Revised: 09/14/2015 //

//--------------------------------------------------------------------------//

// Description: Baseline design file contains DE0 Nano SoC //

// Board pins and I/O Standards. //

//--------------------------------------------------------------------------//

//Copyright 2015 Altera Corporation. All rights reserved. Altera products

//are protected under numerous U.S. and foreign patents, maskwork rights,

//copyrights and other intellectual property laws.

//

//This reference design file, and your use thereof, is subject to and

//governed by the terms and conditions of the applicable Altera Reference

//Design License Agreement. By using this reference design file, you

//indicate your acceptance of such terms and conditions between you and

//Altera Corporation. In the event that you do not agree with such terms and

//conditions, you may not use the reference design file. Please promptly

//destroy any copies you have made.

//

//This reference design file being provided on an "as-is" basis and as an

//accommodation and therefore all warranties, representations or guarantees

//of any kind (whether express, implied or statutory) including, without

//limitation, warranties of merchantability, non-infringement, or fitness for

//a particular purpose, are specifically disclaimed. By making this

//reference design file available, Altera expressly does not recommend,

//suggest or require that this reference design file be used in combination

//with any other product not provided by Altera

//----------------------------------------------------------------------------

//Group Enable Definitions

//This lists every pinout group

//Users can enable any group by uncommenting the corresponding line below:

//`define enable_ADC

//`define enable_ARDUINO

//`define enable_GPIO0

//`define enable_GPIO1

`define enable_HPS

module de0_nano_soc_baseline(

//////////// CLOCK //////////

input FPGA_CLK_50,

input FPGA_CLK2_50,

input FPGA_CLK3_50,

`ifdef enable_ADC

//////////// ADC //////////

/* 3.3-V LVTTL */

output ADC_CONVST,

output ADC_SCLK,

output ADC_SDI,

input ADC_SDO,

`endif

`ifdef enable_ARDUINO

//////////// ARDUINO ////////////

/* 3.3-V LVTTL */

inout [15:0] ARDUINO_IO,

inout ARDUINO_RESET_N,

`endif

`ifdef enable_GPIO0

//////////// GPIO 0 ////////////

/* 3.3-V LVTTL */

inout [35:0] GPIO_0,

`endif

`ifdef enable_GPIO1

//////////// GPIO 1 ////////////

/* 3.3-V LVTTL */

inout [35:0] GPIO_1,

`endif

`ifdef enable_HPS

//////////// HPS //////////

/* 3.3-V LVTTL */

inout HPS_CONV_USB_N,

/* SSTL-15 Class I */

output [14:0] HPS_DDR3_ADDR,

output [2:0] HPS_DDR3_BA,

output HPS_DDR3_CAS_N,

output HPS_DDR3_CKE,

output HPS_DDR3_CS_N,

output [3:0] HPS_DDR3_DM,

inout [31:0] HPS_DDR3_DQ,

output HPS_DDR3_ODT,

output HPS_DDR3_RAS_N,

output HPS_DDR3_RESET_N,

input HPS_DDR3_RZQ,

output HPS_DDR3_WE_N,

/* DIFFERENTIAL 1.5-V SSTL CLASS I */

output HPS_DDR3_CK_N,

output HPS_DDR3_CK_P,

inout [3:0] HPS_DDR3_DQS_N,

inout [3:0] HPS_DDR3_DQS_P,

/* 3.3-V LVTTL */

output HPS_ENET_GTX_CLK,

inout HPS_ENET_INT_N,

output HPS_ENET_MDC,

inout HPS_ENET_MDIO,

input HPS_ENET_RX_CLK,

input [3:0] HPS_ENET_RX_DATA,

input HPS_ENET_RX_DV,

output [3:0] HPS_ENET_TX_DATA,

output HPS_ENET_TX_EN,

inout HPS_GSENSOR_INT,

inout HPS_I2C0_SCLK,

inout HPS_I2C0_SDAT,

inout HPS_I2C1_SCLK,

inout HPS_I2C1_SDAT,

inout HPS_KEY,

inout HPS_LED,

inout HPS_LTC_GPIO,

output HPS_SD_CLK,

inout HPS_SD_CMD,

inout [3:0] HPS_SD_DATA,

output HPS_SPIM_CLK,

input HPS_SPIM_MISO,

output HPS_SPIM_MOSI,

inout HPS_SPIM_SS,

input HPS_UART_RX,

output HPS_UART_TX,

input HPS_USB_CLKOUT,

inout [7:0] HPS_USB_DATA,

input HPS_USB_DIR,

input HPS_USB_NXT,

output HPS_USB_STP,

`endif

//////////// KEY ////////////

/* 3.3-V LVTTL */

input [1:0] KEY,

//////////// LED ////////////

/* 3.3-V LVTTL */

output [7:0] LED,

//////////// SW ////////////

/* 3.3-V LVTTL */

input [3:0] SW

);

hps u0 (

.led_0_led_output (LED), // led_0_led.output

.hps_io_hps_io_emac1_inst_TX_CLK (HPS_ENET_GTX_CLK), // hps_io.hps_io_emac1_inst_TX_CLK

.hps_io_hps_io_emac1_inst_TXD0 (HPS_ENET_TX_DATA[0]), // .hps_io_emac1_inst_TXD0

.hps_io_hps_io_emac1_inst_TXD1 (HPS_ENET_TX_DATA[1]), // .hps_io_emac1_inst_TXD1

.hps_io_hps_io_emac1_inst_TXD2 (HPS_ENET_TX_DATA[2]), // .hps_io_emac1_inst_TXD2

.hps_io_hps_io_emac1_inst_TXD3 (HPS_ENET_TX_DATA[3]), // .hps_io_emac1_inst_TXD3

.hps_io_hps_io_emac1_inst_RXD0 (HPS_ENET_RX_DATA[0]), // .hps_io_emac1_inst_RXD0

.hps_io_hps_io_emac1_inst_MDIO (HPS_ENET_MDIO), // .hps_io_emac1_inst_MDIO

.hps_io_hps_io_emac1_inst_MDC (HPS_ENET_MDC), // .hps_io_emac1_inst_MDC

.hps_io_hps_io_emac1_inst_RX_CTL (HPS_ENET_RX_DV), // .hps_io_emac1_inst_RX_CTL

.hps_io_hps_io_emac1_inst_TX_CTL (HPS_ENET_TX_EN), // .hps_io_emac1_inst_TX_CTL

.hps_io_hps_io_emac1_inst_RX_CLK (HPS_ENET_RX_CLK), // .hps_io_emac1_inst_RX_CLK

.hps_io_hps_io_emac1_inst_RXD1 (HPS_ENET_RX_DATA[1]), // .hps_io_emac1_inst_RXD1

.hps_io_hps_io_emac1_inst_RXD2 (HPS_ENET_RX_DATA[2]), // .hps_io_emac1_inst_RXD2

.hps_io_hps_io_emac1_inst_RXD3 (HPS_ENET_RX_DATA[3]), // .hps_io_emac1_inst_RXD3

.hps_io_hps_io_sdio_inst_CMD (HPS_SD_CMD), // .hps_io_sdio_inst_CMD

.hps_io_hps_io_sdio_inst_D0 (HPS_SD_DATA[0]), // .hps_io_sdio_inst_D0

.hps_io_hps_io_sdio_inst_D1 (HPS_SD_DATA[1]), // .hps_io_sdio_inst_D1

.hps_io_hps_io_sdio_inst_CLK (HPS_SD_CLK), // .hps_io_sdio_inst_CLK

.hps_io_hps_io_sdio_inst_D2 (HPS_SD_DATA[2]), // .hps_io_sdio_inst_D2

.hps_io_hps_io_sdio_inst_D3 (HPS_SD_DATA[3]), // .hps_io_sdio_inst_D3

.hps_io_hps_io_usb1_inst_D0 (HPS_USB_DATA[0]), // .hps_io_usb1_inst_D0

.hps_io_hps_io_usb1_inst_D1 (HPS_USB_DATA[1]), // .hps_io_usb1_inst_D1

.hps_io_hps_io_usb1_inst_D2 (HPS_USB_DATA[2]), // .hps_io_usb1_inst_D2

.hps_io_hps_io_usb1_inst_D3 (HPS_USB_DATA[3]), // .hps_io_usb1_inst_D3

.hps_io_hps_io_usb1_inst_D4 (HPS_USB_DATA[4]), // .hps_io_usb1_inst_D4

.hps_io_hps_io_usb1_inst_D5 (HPS_USB_DATA[5]), // .hps_io_usb1_inst_D5

.hps_io_hps_io_usb1_inst_D6 (HPS_USB_DATA[6]), // .hps_io_usb1_inst_D6

.hps_io_hps_io_usb1_inst_D7 (HPS_USB_DATA[7]), // .hps_io_usb1_inst_D7

.hps_io_hps_io_usb1_inst_CLK (HPS_USB_CLKOUT), // .hps_io_usb1_inst_CLK

.hps_io_hps_io_usb1_inst_STP (HPS_USB_STP), // .hps_io_usb1_inst_STP

.hps_io_hps_io_usb1_inst_DIR (HPS_USB_DIR), // .hps_io_usb1_inst_DIR

.hps_io_hps_io_usb1_inst_NXT (HPS_USB_NXT), // .hps_io_usb1_inst_NXT

.hps_io_hps_io_spim1_inst_CLK (HPS_SPIM_CLK), // .hps_io_spim1_inst_CLK

.hps_io_hps_io_spim1_inst_MOSI (HPS_SPIM_MOSI), // .hps_io_spim1_inst_MOSI

.hps_io_hps_io_spim1_inst_MISO (HPS_SPIM_MISO), // .hps_io_spim1_inst_MISO

.hps_io_hps_io_spim1_inst_SS0 (HPS_SPIM_SS), // .hps_io_spim1_inst_SS0

.hps_io_hps_io_uart0_inst_RX (HPS_UART_RX), // .hps_io_uart0_inst_RX

.hps_io_hps_io_uart0_inst_TX (HPS_UART_TX), // .hps_io_uart0_inst_TX

.hps_io_hps_io_i2c0_inst_SDA (HPS_I2C0_SDAT), // .hps_io_i2c0_inst_SDA

.hps_io_hps_io_i2c0_inst_SCL (HPS_I2C0_SCLK), // .hps_io_i2c0_inst_SCL

.hps_io_hps_io_i2c1_inst_SDA (HPS_I2C1_SDAT), // .hps_io_i2c1_inst_SDA

.hps_io_hps_io_i2c1_inst_SCL (HPS_I2C1_SCLK), // .hps_io_i2c1_inst_SCL

.memory_mem_a (HPS_DDR3_ADDR), // memory.mem_a

.memory_mem_ba (HPS_DDR3_BA), // .mem_ba

.memory_mem_ck (HPS_DDR3_CK_P), // .mem_ck

.memory_mem_ck_n (HPS_DDR3_CK_N), // .mem_ck_n

.memory_mem_cke (HPS_DDR3_CKE), // .mem_cke

.memory_mem_cs_n (HPS_DDR3_CS_N), // .mem_cs_n

.memory_mem_ras_n (HPS_DDR3_RAS_N), // .mem_ras_n

.memory_mem_cas_n (HPS_DDR3_CAS_N), // .mem_cas_n

.memory_mem_we_n (HPS_DDR3_WE_N), // .mem_we_n

.memory_mem_reset_n (HPS_DDR3_RESET_N), // .mem_reset_n

.memory_mem_dq (HPS_DDR3_DQ), // .mem_dq

.memory_mem_dqs (HPS_DDR3_DQS_P), // .mem_dqs

.memory_mem_dqs_n (HPS_DDR3_DQS_N), // .mem_dqs_n

.memory_mem_odt (HPS_DDR3_ODT), // .mem_odt

.memory_mem_dm (HPS_DDR3_DM), // .mem_dm

.memory_oct_rzqin (HPS_DDR3_RZQ), // .oct_rzqin

);

endmodule

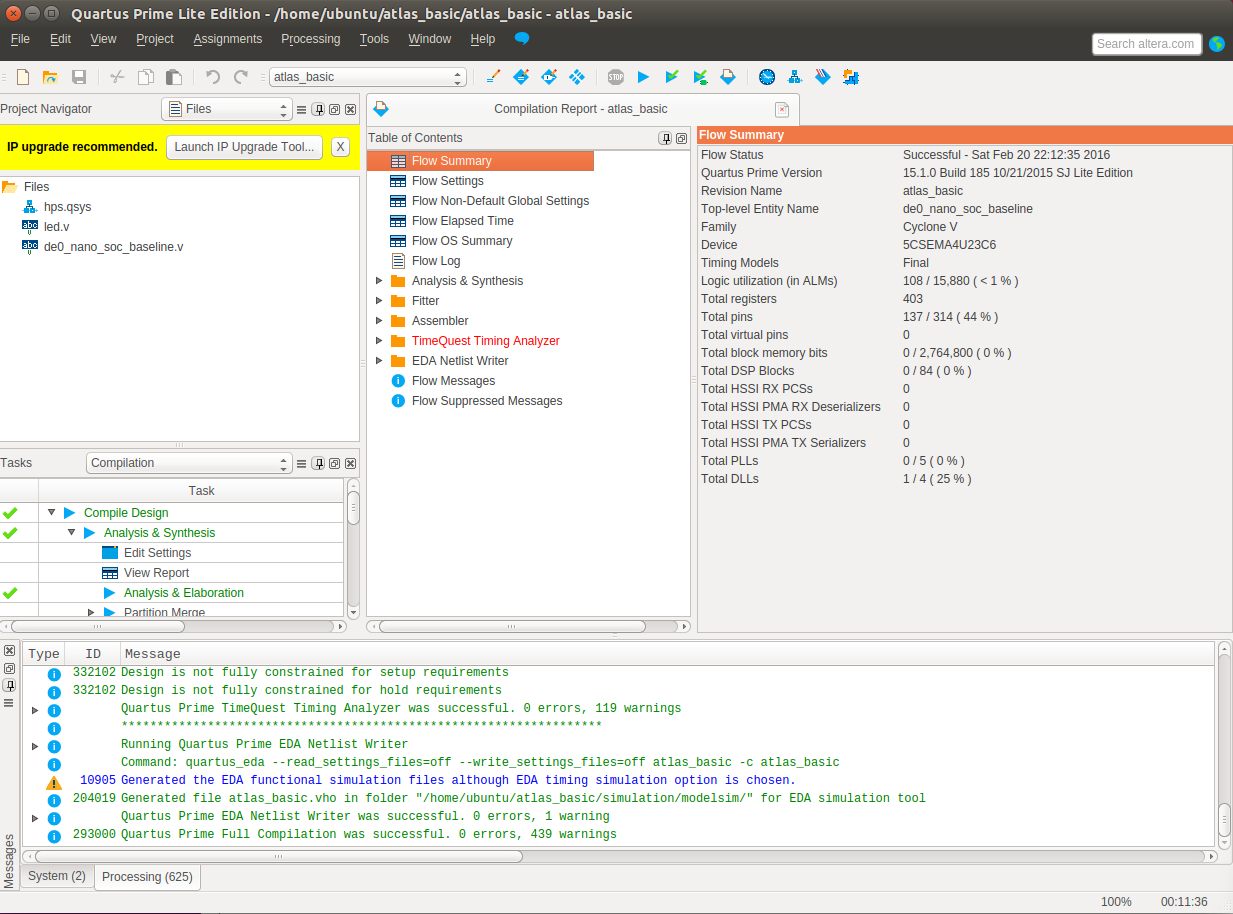

合成

メニューから

Processing - Start Compilation

を実行する。

なんか赤いところがあるけどよく分からず。

メニューの

File - Convert Programming Files

を開いて

Raw Binary File(.rbf)

Passive Parallel x16, Compression

にして

ATLAS_SOC_GHRD.rbf

を生成する。

ハードはこれで完成。