基板の改訂をしていると、eeschema で回路図のシンボルを変更したい時があります。

しかしながら、既に pcbnew でフットプリントを配置済みだと、eeschema での回路図上のシンボルと pcbnew での基板デザイン上のフットプリントの整合性が取れなくなります。

この2つの対応は、リファレンスNo. などではなく、ネットリスト上での tstamp で管理されます。

ここでは、 tstamp の挙動について調べてみます。

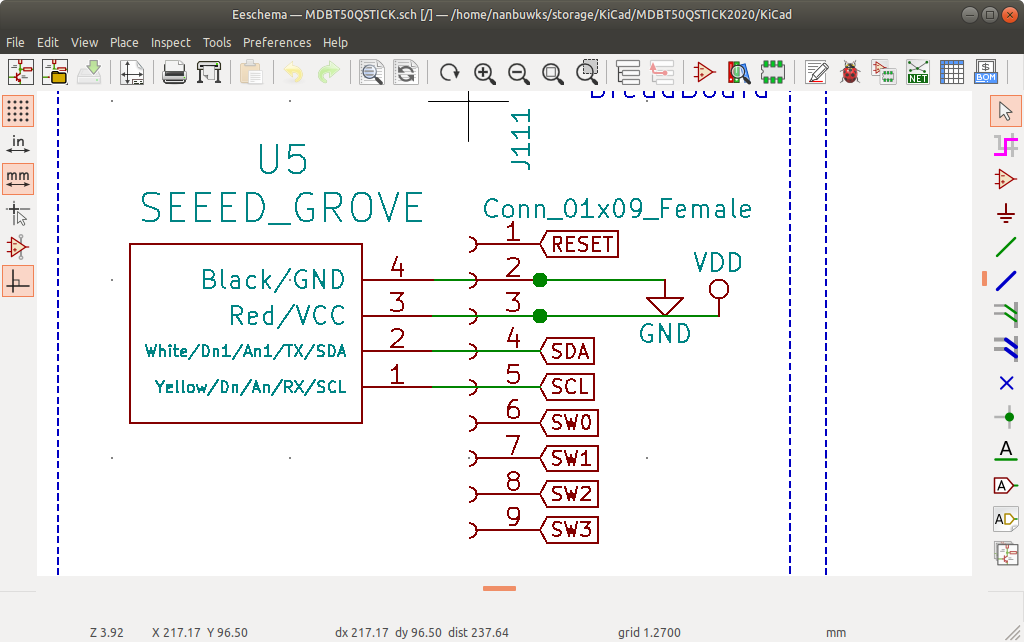

ここの、J1 について操作をしていきます。

まず、NETファイルを開きます。

該当のJ1の項目は以下のようになっています。

(comp (ref J1)

(value Conn_01x09_Female)

(footprint Connector_PinHeader_2.54mm:PinHeader_1x08_P2.54mm_Vertical)

(datasheet ~)

(libsource (lib Connector) (part Conn_01x09_Female) (description "Generic connector, single row, 01x09, script generated (kicad-library-utils/schlib/autogen/connector/)"))

(sheetpath (names /) (tstamps /))

(tstamp 5EFDC3D3))

ここで、 ref J1 というのは論理的な意味を持っていません。

例えば、eeschema で J1 を J111に変更します。

それでも Parts Assign 画面でも pcbnew でも、今まで J1 において行った設定は J111 に引き継がれます。

NETファイルは以下のようになっていて、tstamp は変化していないことが確認できます。

(comp (ref J111)

(value Conn_01x09_Female)

(footprint Connector_PinHeader_2.54mm:PinHeader_1x08_P2.54mm_Vertical)

(datasheet ~)

(libsource (lib Connector) (part Conn_01x09_Female) (description "Generic connector, single row, 01x09, script generated (kicad-library-utils/schlib/autogen/connector/)"))

(sheetpath (names /) (tstamps /))

(tstamp 5EFDC3D3))

次に、シンボルの割当も変更してみます。回路図上でJ1のプロパティから Library reference から操作をします。

9pin male D-SUB connector に変更しましたが Value Fieldは Conn_01x09_Female のままになっています。

NETファイルにおいても、tstamp は変更はしていません。

(comp (ref J111)

(value Conn_01x09_Female)

(footprint Connector_PinHeader_2.54mm:PinHeader_1x08_P2.54mm_Vertical)

(datasheet ~)

(libsource (lib Connector) (part DB9_Male) (description "9-pin male D-SUB connector"))

(sheetpath (names /) (tstamps /))

(tstamp 5EFDC3D3))

次に、J111をJ1に戻し、その上で J1を一旦削除して同じシンボルを登録しました。リファレンスは旧来と同じJ1です。

一見最初と同じ状態になったように見えますが・・・

(comp (ref J1)

(value Conn_01x09_Female)

(footprint Connector_PinHeader_2.54mm:PinHeader_1x09_P2.54mm_Vertical)

(datasheet ~)

(libsource (lib Connector) (part Conn_01x09_Female) (description "Generic connector, single row, 01x09, script generated (kicad-library-utils/schlib/autogen/connector/)"))

(sheetpath (names /) (tstamps /))

(tstamp 5F172C6F))

NETファイルの tstamp の値が変わっています。

この状態だと、Parts assing や pcbnew の既存の設定と整合性が取れなくなります。単に新しいフットプリントをアサインし、pcbnew で旧来のフットプリントを削除→NETファイいるの再読込をすればいいのですが・・・

pcbnew 上でフットプリントにカスタマイズを加えている場合はカスタマイズがリセットされるので面倒です。

この例では、シルク印刷の枠線を削除し、パッドごとに微妙に縦サイズを変更しています。このフットプリントは P2 となっていますが、今回の例では eeschema で P2 → J1 と変更をしていたため、表示も異なっています。

先に tstamp が変更された NET ファイルを読み込んだ状態では、P2-Pad1,P2-Pad2,・・・ が J1-Pad1,J1-Pad2・・・と認識しておらず本当それぞれからラッツネットが伸びていないとけないのですがそれも出現していません。

これに対応するには、pcbnew の kicad_pcb 形式ファイルを操作して tstamp の整合性を取る必要があります。

kicad_pcb ファイルの該当部分は以下の通りです。

(module library:SolderWirePad_Circle_8xInline_0-85mmDrill (layer F.Cu) (tedit 5C778018) (tstamp 5C85A987)

(at 80.0506 87.5948)

(descr SolderWirePad_Circle_8xInline_0-85mmDrill)

(tags SolderWirePad_Circle_8xInline_0-85mmDrill)

(path /5CAAA8A0)

(fp_text reference P4 (at 0 -3.175) (layer F.SilkS) hide

(effects (font (size 1 1) (thickness 0.15)))

)

(fp_text value CONN_01X08 (at -0.635 3.175) (layer F.Fab) hide

(effects (font (size 1 1) (thickness 0.15)))

)

(pad 8 thru_hole oval (at 8.89 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 22 "Net-(P2-Pad8)"))

(pad 6 thru_hole oval (at 3.81 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 23 "Net-(P2-Pad6)"))

(pad 7 thru_hole oval (at 6.35 0) (size 1.7 1.4) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 24 "Net-(P2-Pad7)"))

(pad 5 thru_hole oval (at 1.27 0) (size 1.5 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 11 "Net-(P2-Pad5)"))

(pad 3 thru_hole oval (at -3.81 0) (size 1.7 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 2 "Net-(P2-Pad3)"))

(pad 4 thru_hole oval (at -1.27 0) (size 1.6 1.2) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 10 "Net-(P2-Pad4)"))

(pad 2 thru_hole oval (at -6.35 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 57 "Net-(P2-Pad2)"))

(pad 1 thru_hole rect (at -8.89 0) (size 1.5 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 9 "Net-(P2-Pad1)"))

)

うーん、refence が P4 になっていてヘンテコですね。これはいろいろ試行錯誤した名残です。先に

この2つの対応は、リファレンスNo. などではなく、ネットリスト上での tstamp で管理されます。

と書きましたがこの値は本当に変更しても影響はありませんでした。

さて、この該当部分のうち、

(tstamp 5C85A987)

とありますが NETファイルの tstamp に対応するのはここではありません。

(path /5CAAA8A0)

実はコレです(!!)。

あれ? 5EFDC3D3 ではなかったのかな? 実は今まで述べて来た 5EFDC3D3 は既に eeschema 上の P2 シンボルを一旦削除し改めて J1 を配置した状態の値でした。説明時の最初の状態で既に整合性が取れていなかったのです。

これを整合性を取るためには

(path /5F172C6F)

とする必要があります。

これを変更し、pcbnew を実行、NETファイルを再読込すると以下のように Net 情報もラッツネットも正常に認識するようになりました。

ちなみに、kicad_pcb ファイルには

(pad 8 thru_hole oval (at 8.89 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 22 "Net-(P2-Pad8)"))

(pad 6 thru_hole oval (at 3.81 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 23 "Net-(P2-Pad6)"))

(pad 7 thru_hole oval (at 6.35 0) (size 1.7 1.4) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 24 "Net-(P2-Pad7)"))

(pad 5 thru_hole oval (at 1.27 0) (size 1.5 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 11 "Net-(P2-Pad5)"))

(pad 3 thru_hole oval (at -3.81 0) (size 1.7 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 2 "Net-(P2-Pad3)"))

(pad 4 thru_hole oval (at -1.27 0) (size 1.6 1.2) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 10 "Net-(P2-Pad4)"))

(pad 2 thru_hole oval (at -6.35 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 57 "Net-(P2-Pad2)"))

(pad 1 thru_hole rect (at -8.89 0) (size 1.5 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 9 "Net-(P2-Pad1)"))

とありました。このような記述はそのまま変更せずに処理しましたが、それも含めて pcbnew の起動後の保存時には、以下のように自動で修正されていました。

(module library:SolderWirePad_Circle_8xInline_0-85mmDrill (layer F.Cu) (tedit 5C778018) (tstamp 5C85A987)

(at 80.0506 87.5948)

(descr SolderWirePad_Circle_8xInline_0-85mmDrill)

(tags SolderWirePad_Circle_8xInline_0-85mmDrill)

(path /5EFDC3D3)

(fp_text reference J1 (at 0 -3.175) (layer F.SilkS) hide

(effects (font (size 1 1) (thickness 0.15)))

)

(fp_text value Conn_01x09_Female (at -0.635 3.175) (layer F.Fab) hide

(effects (font (size 1 1) (thickness 0.15)))

)

(pad 8 thru_hole oval (at 8.89 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 171 SW2))

(pad 6 thru_hole oval (at 3.81 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 168 SW0))

(pad 7 thru_hole oval (at 6.35 0) (size 1.7 1.4) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 191 SW1))

(pad 5 thru_hole oval (at 1.27 0) (size 1.5 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 193 SCL))

(pad 3 thru_hole oval (at -3.81 0) (size 1.7 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 15 VDD))

(pad 4 thru_hole oval (at -1.27 0) (size 1.6 1.2) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 190 SDA))

(pad 2 thru_hole oval (at -6.35 0) (size 1.7 1.5) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 1 GND))

(pad 1 thru_hole rect (at -8.89 0) (size 1.5 1.3) (drill 0.85) (layers *.Cu *.Mask F.SilkS)

(net 169 RESET))

)

付記 本当に行った作業

実際は最後の kicad_pcb ファイルの 書き換えは

(path /5EFDC3D3)

としています。説明が複雑になってしまいますが今回は一旦 5CAAA8A0 から 5EFDC3D3 に変更した後、説明のためのデータ取りのために 5EFDC3D3 から 5F172C6F に2回変更しました。今回は 5CAAA8A0 から 5EFDC3D3 の変更が実際に行った作業になるので、eeschema で 5F172C6F の状態から 5EFDC3D3 に復元し、pcbnew で 5EFDC3D3 への対応をすることにしました。