Windowsのリモートデスクトップを使って会社のPCにログインできれば、Vivado経由でFPGAの論理合成や書き込みはできると思います。しかし、組み込み開発の世界では「基板」という実機がないとデバッグがやりづらいのが現状です。

会社が基板の持ち帰りを許可してくれればいいのですが、そうでなければ基板の様子が確認できないので、ちょっとやりづらいことになるかもしれません。

そんなとき、JTAGを活用すればリモート実機デバッグの効率を圧倒的に上げることができるかもしれません。筆者は実は10年以上、JTAGを使ってリモートデバッグでリモートワークをしてきました。

今までのリモートデバッグ

FPGAの場合

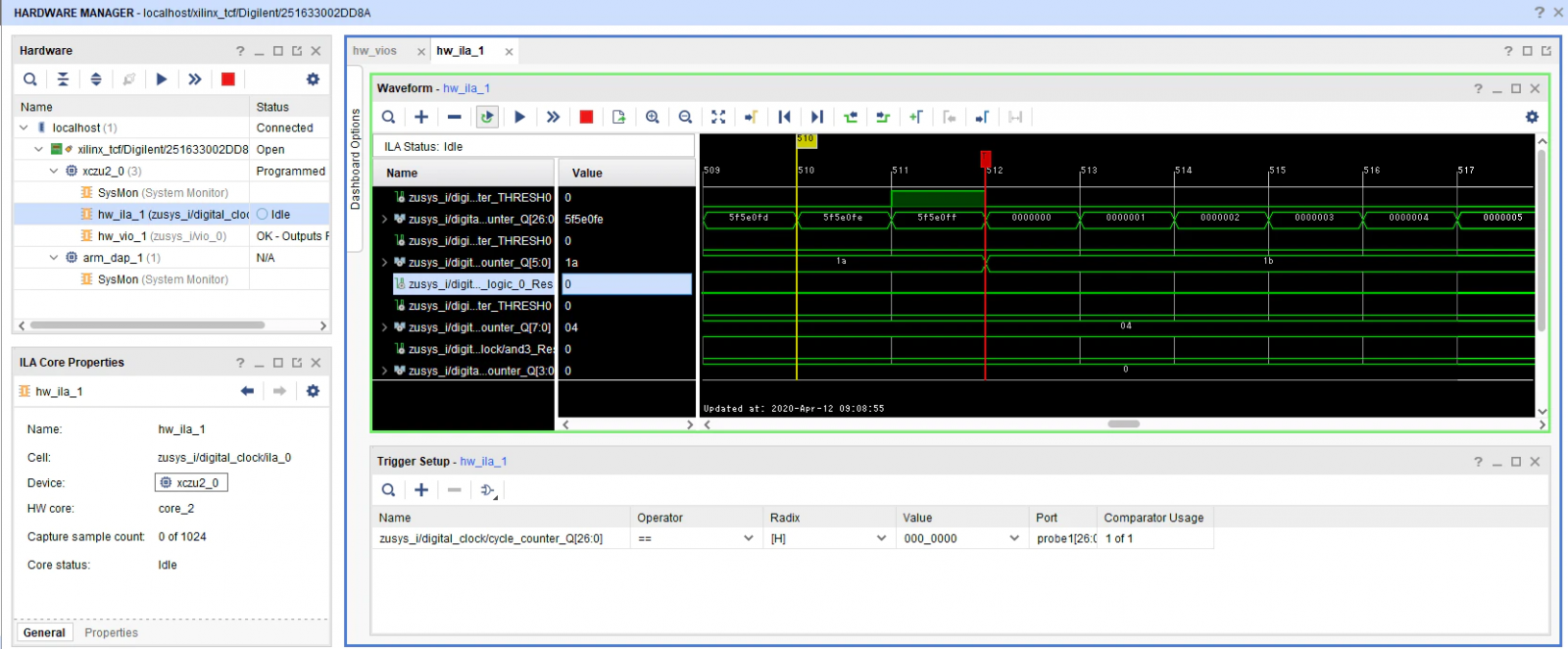

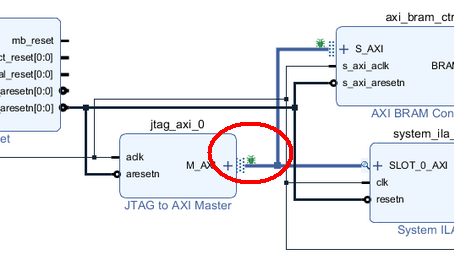

XILINXのFPGAではJTAGを使ったデバッグ方法ではILAや(古くはChipScope)というツールが用意されています。Intel (ALTERA)にもSignalTapというのが用意されています。

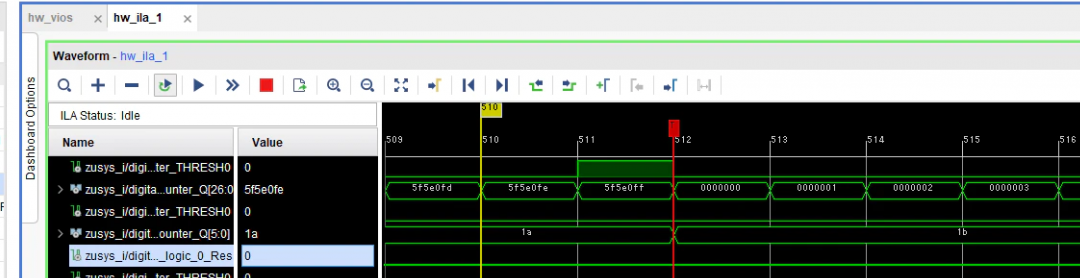

おそらくほとんどの人がILAやSignalTAPを使ってデバッグしていると思います。これらのツールは、FPGA内部のBlockRAMに波形をため込んで、それをJTAGからアクセスして吸い出してVivadoの中で波形として表示するというものです。

ILAを使ってデバッグしていると、

- あらかじめプローブを設定した信号しか見ることができない(別の信号を見たいときには、つなぎ変えて論理合成をして書き込まなければならない)

- FPGAが起動していない(コンフィグに失敗した状態)だと、ILAは認識しない

- 絶対時間が分からない

- 秒単位での動作はわからない

という問題に気が付きます。

プローブした信号しか見えない問題

ILAを使うには、Block Designで「見たい」とマーキングするか、ILAというIPを埋め込むか、HDLのソースでILAを直接インプリメントします。

これで論理合成をすれば新しいILAが埋め込まれたデザインが出来上がり、FPGAに書き込んで動作テストをする・・というわけなのですが、FPGAの動作が全体的におかしいという場合、全部の入出力信号を見ることはできません。

FPGAが起動していないとILAを認識しない問題

ILAといっても、FPGAにとってはLUTやBRAMを使うただの回路ですから、FPGA自体が起動していないと動きません。

例えば、コンフィグROMのM2,M1,M0を間違えたとか、コンフィグROMが空だったとか、boot.binが壊れていたりとか、SDカードが刺さっていないとか、そのような状態ではILAやSignalTAPは手も足も出ません。

絶対時間が分からない問題

ILAは素晴らしいツールなのですが、時間軸の単位が「クロック数」なのです。

1クロックが何秒かがわかれば絶対時間がわかるかもしれませんが、そもそもクロックの周波数が正しいということはだれが保証するのでしょうか?FPGAの中には様々なPLL(MCMM)が入っていて、100MHzだと思って設計していた回路のクロックが実は66.6MHzだったなんていうこともあります。

会社に行って実機があれば、テストポイントに信号を出してオシロでちょっと見てみればわかるのに、リモートで周波数を測定することは簡単ではないのです。

秒単位の動作がわからない問題

ILAはBlockRAMに波形をため込むものなので、せいぜい数百キロバイトです。BRAMの容量の問題で何秒とか何十秒といった変化を見ることはできません。

CPUの場合

CPUも同じようにJTAG-ICEといったデバッガや、シリアルのコンソールでデバッグすることになりますが、JTAG-ICEがやれることはプログラムのステップ実行とメモリの読み書きです。I/Oの端子の状態がどうなっているかを直接知ることはできません。

また、CPUの品種にもよりますが、絶対時間がわからない問題や正常にCPUが起動しないとJTAG-ICEも動かないことなどは変わりません。

これらの問題により、リモートなFPGAデバッグは大変もどかしい作業になります。

リモートデバッグにこそ、JTAGバウンダリスキャンを活用しよう!

JTAGにはバウンダリスキャンという、I/Oを見たり操作したりする機能があります。バウンダリスキャンはJTAGの標準機能なので、ほぼすべてのFPGAや、大規模なCPUに搭載されています。

JTAGとは何か、バウンダリスキャンとは何かということを説明すると長くなるので今回は解説しません。

詳しく知りたい方はJTAG技術情報のページをご覧ください。

バウンダリスキャンを活用すれば、

- プローブを埋め込まなくても、全I/Oが見える

- FPGAやCPUが起動していなくても使える

- 絶対時間が分かる

- 秒単位での動作がわかる

と、ILAやSignalTAPではできなかった部分がデバッグできるようになり、リモートワークが一層捗ることになります。

JTAGバウンダリスキャンというと「基板の検査を行うための工場の出荷検査ツール」というのをイメージされる方もいらっしゃるかもしれませんが、何百万円もする基板検査ツールを使っても開発中の回路のデバッグはできません。

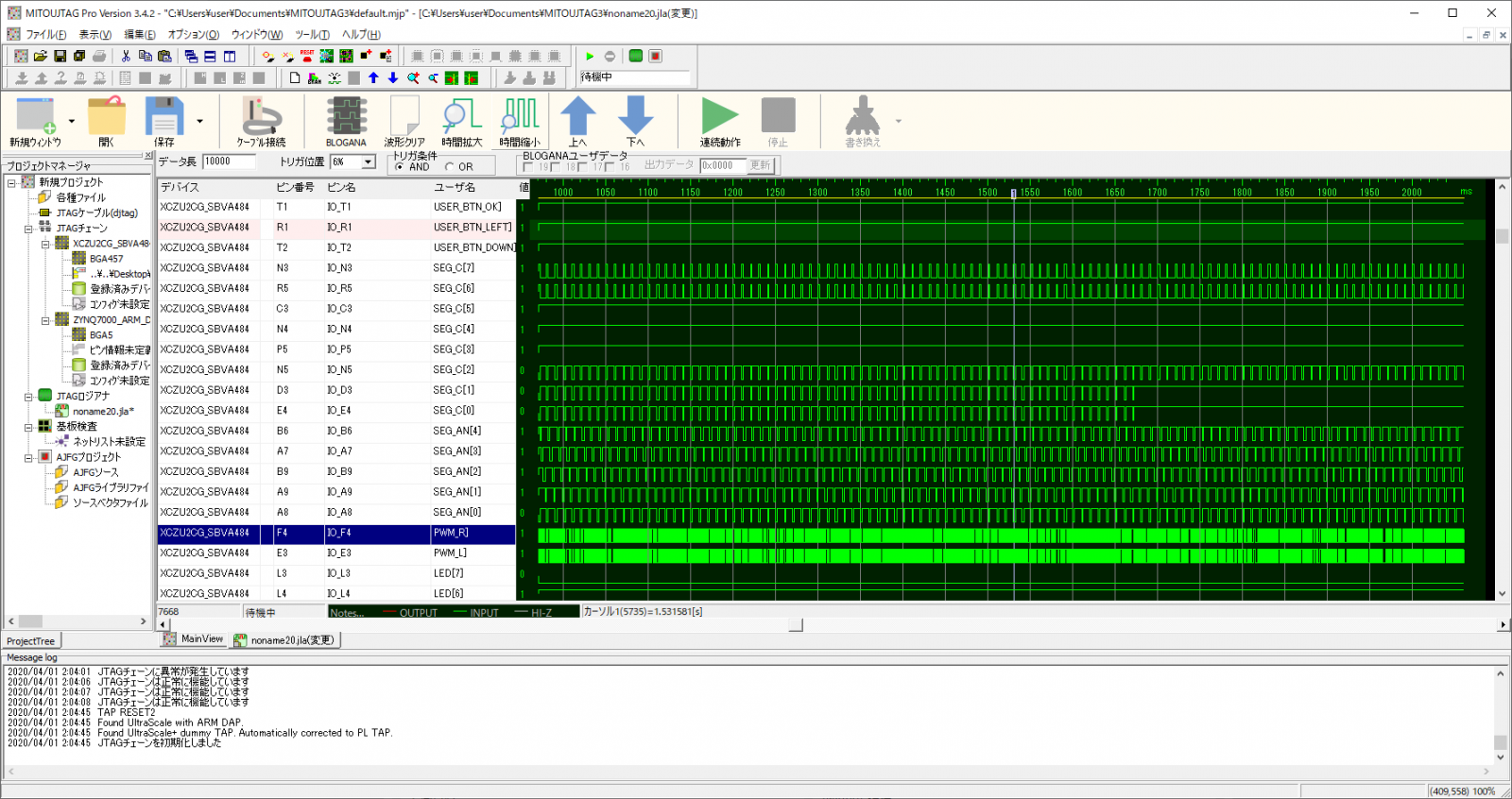

筆者は組み込みのデバッグ用に、MITOUJTAG (みとうジェイタグ) というソフトウェアを開発しました。

みとうジェイタグというのは、その名前のとおり未踏ソフトウェアで開発されたソフトウェアで2003年度に採択されたものです。それから16年コツコツとアップデートを続けて最新のFPGAに対応させつづけてきました。

MITOUJTAGを使ったデバッグの例を具体的に見ていきたいと思います。

プローブを埋め込まなくても、全I/Oが見える

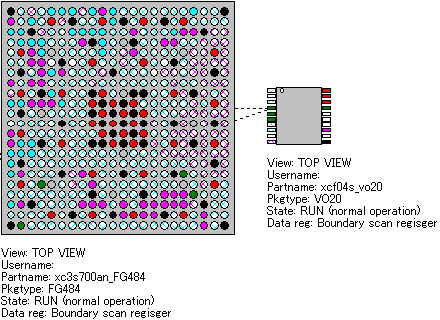

MITOUJTAGを使うと、FPGAのI/Oの状態(H/L、入力/出力)が可視化されます。

下の図はあるBGAのデバイスと、SOPパッケージのコンフィグROMの端子を可視化したもので、裏側に生えているBGAの足の1本1本が見えています。ピンクはHレベル、水色はLレベル、塗りつぶしは出力、網掛けは入力端子を表しています。赤と黒は電源です。

このような絵が毎秒数十~数百回更新されます。

FPGAの端子にはもともと名前が付いていないのでXDCファイルやUCF,QSFなどピン定義に使用したファイルを読み込むことで、1本1本の名前を付けることができます。そうすると、FPGAがどのように動作しているかを波形として表示することができるようになります。

下の図は、UltraScale+のボードの外部の端子の波形です。

FPGAやCPUが起動していなくても使える

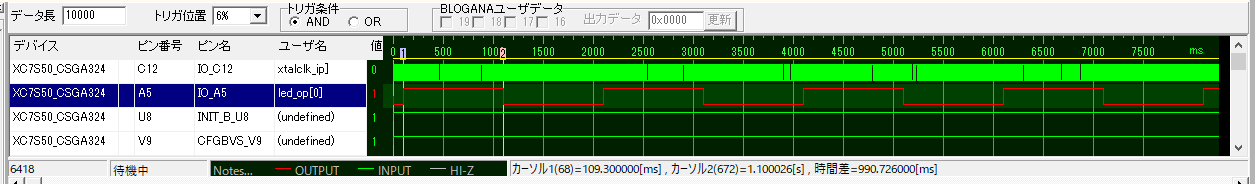

下の図は、Spartan-7のFPGAボードが起動するまでのI/Oの状態です。

開始後1秒のところでINIT_Bという信号がL→Hに遷移して、コンフィグが開始します。コンフィグ期間中、CCLKが出力され、K18番ピン(MOSI)にコンフィグデータが入力されます。開始後6.8秒ほど経ったところでDONEピンがHに上がり、コンフィグが完了したことを示しています。

コンフィグが完了すると、LEDが点滅をはじめ、DDR3メモリの信号が激しく動いています。

このように、コンフィグ前のFPGAが起動していない状態でもI/Oの状態を見ることができ、プローブを埋め込むことなく、秒単位でのサンプリングが可能であることがわかります。

クロックの絶対周波数がわからない問題

ILAではクロックの絶対周波数がわからないため出社してオシロで見る必要がありましたが、MITOUJTAGを使えば出社しなくてもわかります。

以下のような簡単なLEDチカチカのHDLを書きます。このHDLは、入力されたクロックを50M回数えて、LEDの出力を反転させるというものです。

つまり、入力クロックが50MHzならばLEDは1秒で点灯と消灯を繰り返すでしょう。

entity main is

Port (xtalclk_ip : in std_logic;

led_op : out std_logic);

end main;

architecture Behavioral of main is

signal clk : std_logic;

signal led : std_logic;

signal count : integer range 0 to 50000000-1;

begin

clk <= xtalclk_ip;

process(clk) begin

if(clk'event and clk ='1') then

if(count = 50000000-1) then

count <= 0;

led <= not led;

else

count <= count + 1;

end if;

end if;

end process;

led_op <= led;

end Behavioral;

もし、実際のクロックが125MHzや200MHzになっていれば、分周した周波数もそれに比例して変わるはずです。

MITOUJTAGでは秒単位でのサンプリングができるため、このような周波数測定も可能になります。

データバスが欠けている場合

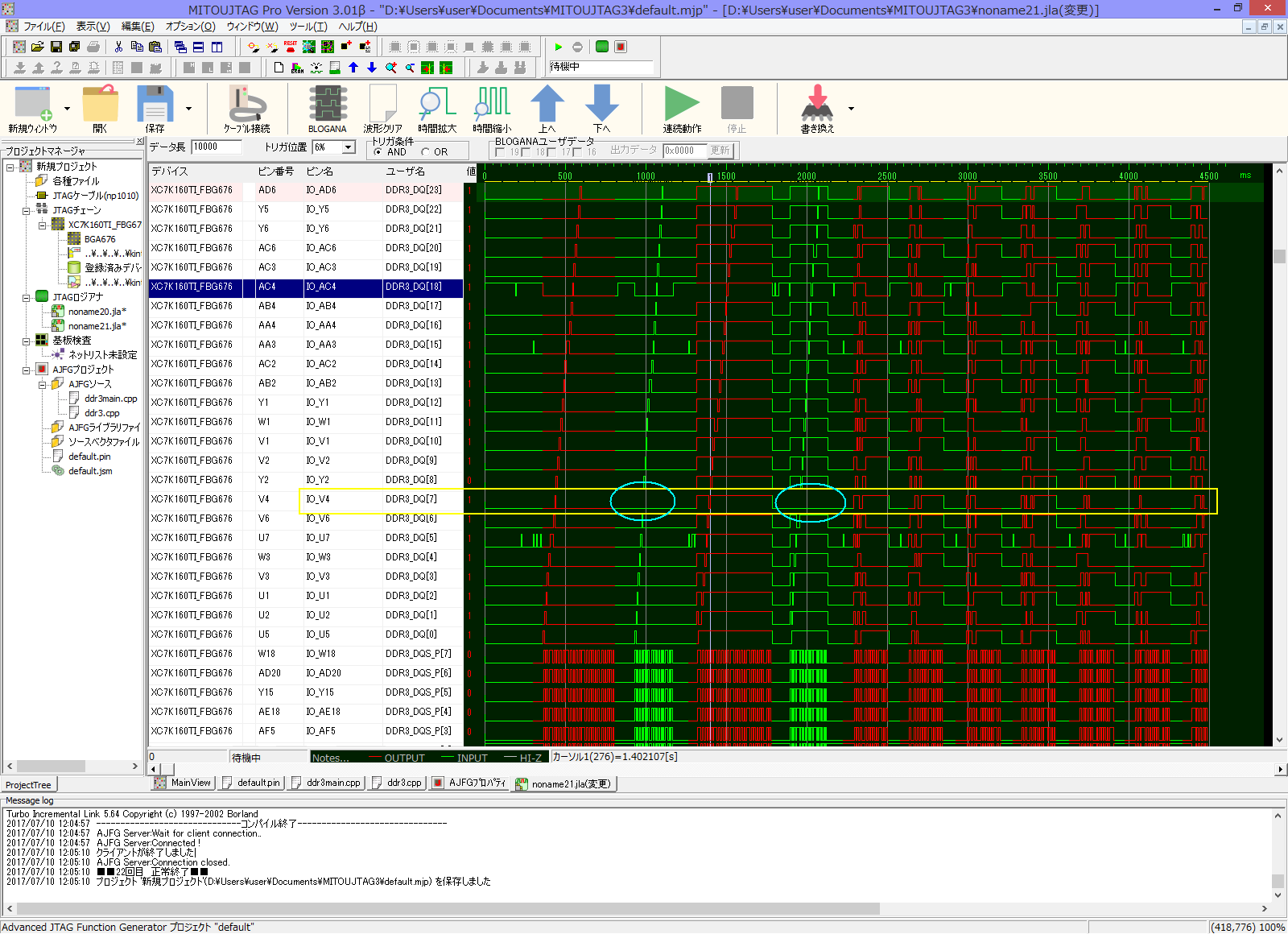

コネクタに接触不良が起きて、データバスの1本だけが欠けている場合や、DIMMモジュールの接触が不良している場合などがあります。下の波形は、ある基板におけるDDR3メモリのテストをMITOUJTAGで行ったものです。DDR3_DQ[7]だけが他のデータバスとは異なり、明らかに信号が来ていません。ILAで見つけるのは困難でしょう。

このような、基板レベルでの不具合もバウンダリスキャンでなら発見できるのです。

まとめ

いかがでしたでしょうか。

JTAGバウンダリスキャンを活用すると、FPGAやCPUのI/Oの波形が見えるので、オシロが手元になくても基板レベルでのデバッグが可能になります。私は10年以上前から、自宅から会社に置いてきた機器をずぼらに操作したりデバッグするためにMITOUJTAGを発展させてきたのです。寝て起きて、まだ動いているかの確認とか。

それが今、社会の役に立つときがきたと実感しています。

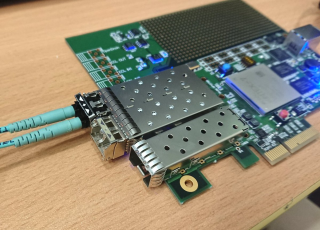

MITOUJTAGにはXILINX FPGAの書き込み機能や、BLOGANAというILAのシンプルなものみたいなのも入っているので、Vivadoを使わなくても書き込みやFPGA内部のデバッグもできます。できることはI/O端子の観察だけではありません。

それに、DigilentのUSB-JTAGや、XILINXのPlatformCableUSB、ALTERAのUSB-Blaster、VivadoとMITOUJTAGを切り替えて使うこともできます。(※PlatformCable USBを使うのはISE14のLabToolsが必要になる)

FTDIのMPSSEに対応させるライブラリも作成しましたので、さらにいろんなボードで使えるようになったと思います。

これまでハードウェアの実機に触らなければデバッグがしづらかったと思う方や、基板の持ち出しを許してくれない会社にお勤めの場合など、リモートデスクトップでMITOUJTAGを使ってデバッグしてみてはいかがでしょうか。

きっと、手元に実機があるような感じで「見える」ようになると思います。

MITOUJTAGについて詳しくはこちらのページをご覧ください