RTLで書いた小規模な回路はIPにするのではなくRTLモジュールとして配置するほうが便利でしょう。

モジュールは、IPとは異なり、インタフェースの仕様をGUIで設定できないので、想定しているのとは異なるブロックデザインのシンボルが作られる場合があります。

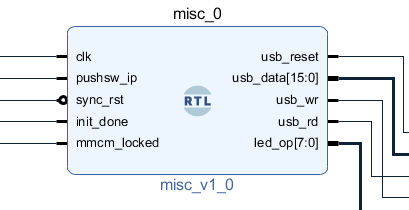

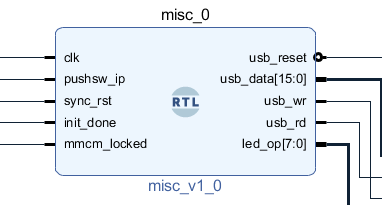

例えば、下の図のusb_resetというポートは正論理の信号なのですが丸が付いてしまっています。

単に表示上の問題だけではなく、Vivadoはどこかでリセットの論理が逆だとWarningを出してくるかもしれません。

設計したとおりのリセット極性をVivadoに認識させるためには、モジュールのVHDLのarchtecture ~ beginの間にattributeを書くとうまくいきます。

architecture Behavioral of misc is

・・・(中略)・・・

ATTRIBUTE X_INTERFACE_INFO : STRING;

ATTRIBUTE X_INTERFACE_PARAMETER : STRING;

ATTRIBUTE X_INTERFACE_PARAMETER OF usb_reset: SIGNAL IS "XIL_INTERFACENAME usb_reset, POLARITY ACTIVE_HIGH, INSERT_VIP 0";

ATTRIBUTE X_INTERFACE_INFO OF usb_reset: SIGNAL IS "xilinx.com:signal:reset:1.0 usb_reset RST";begin