はじめに

過去に以下の記事を書きました。

これに対して「ソースは公開しないのですか」というお問い合わせがあったため、ここに公開することにしました。この記事では、verilogソースを合成・配置配線し、FPGAへプログラムする方法をガイドします。

基本的にはUltra96ボードが対象ですが、同様の手法でUltraZedボード及びArty7ボードでの動作を確認しています。

1. 準備

1.1 ツール

対象となるVivadoはVivado 2021.1です。tclスクリプトに版数依存があるため、他の版数では動作しないかもしれません。

1.2 公開リポジトリ

以下の場所から、ROMデータ、ソース、ブロックデザイン、合成制約の4つのフォルダ及びファイルを入手してください。

https://github.com/mocapapa/SpaceInvaders_BSV_Ultra96v2

1.3 ローカルフォルダ

以下のように仮定します。

C:/Users/<ユーザ名>/Vivado/<プロジェクト名>

1.4 機材

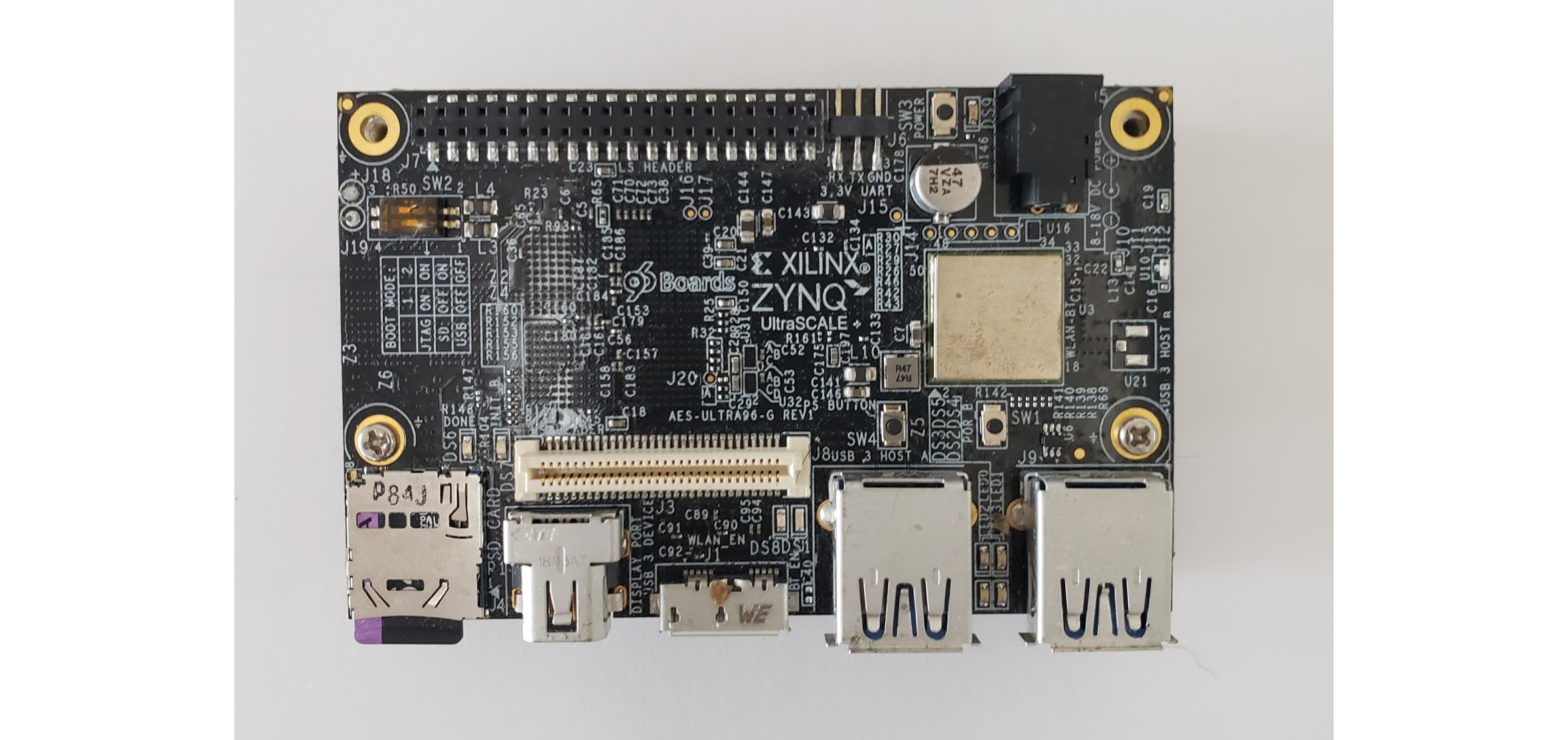

1.4.1 Avnet製Ultra96 V2

Xilinx Zynq UltraScale+ ™ MPSoCを搭載した評価ボードで、価格は約3万円です。

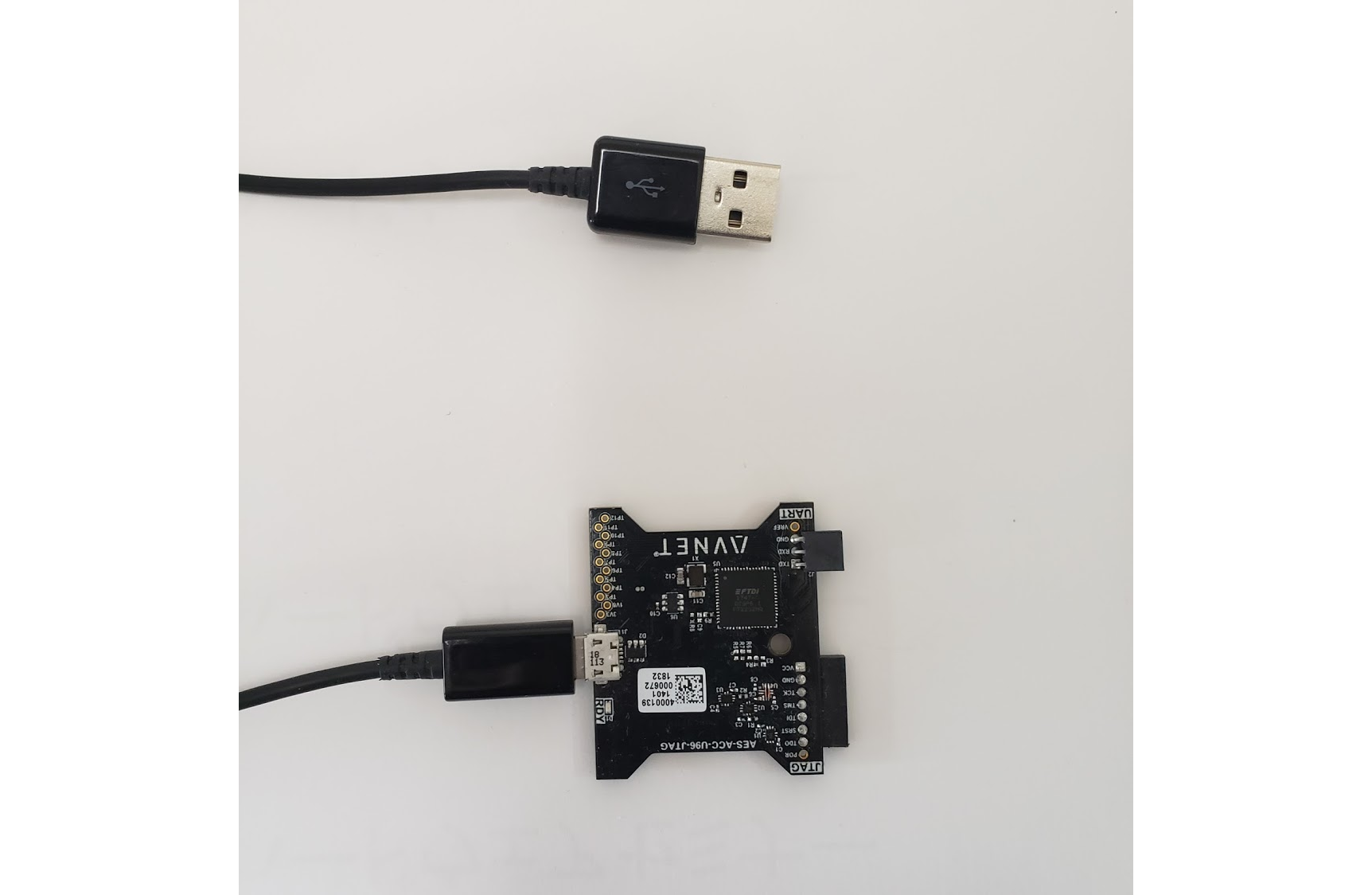

1.4.2 USB JTAGボード、ケーブル

PCからビットストリームをダウンロードする際に使うUSBからJTAGへのインタフェースボードです。これ用のUSBケーブルも必要です。ボード価格は5,000円です。

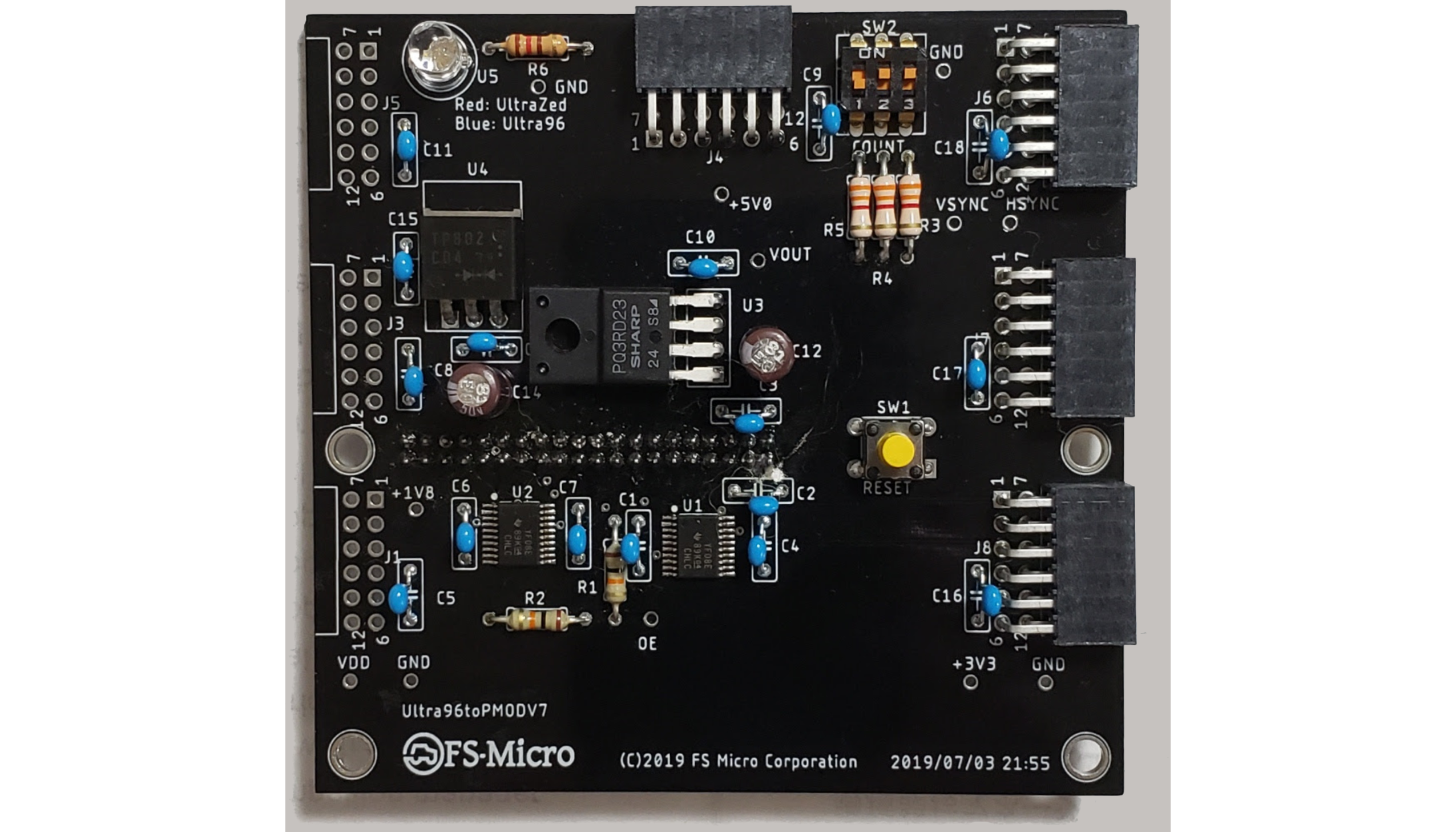

1.4.3 FSマイクロ製Ultra96toPMODボード

Ultra96からオーディオやビデオ(VGA)、ジョイスティック、スイッチとインタフェースするためのPMOD変換ボードです。作成枚数にもよりますが、Seeed Fusion PCBで10枚製造して送料込みで7.9USDでした。ただし、部品代は別で、基板だけの価格です。

本SpaceInvadersゲームをUltra96ボードではなく、ArtyボードやUltraZedボードに移植する際には本ボードは不要です。

UltraZedボードインタフェースを削除した最新版を作成しました。データは以下の場所に置いてあります。

https://github.com/mocapapa/Ultra96toPMODV10

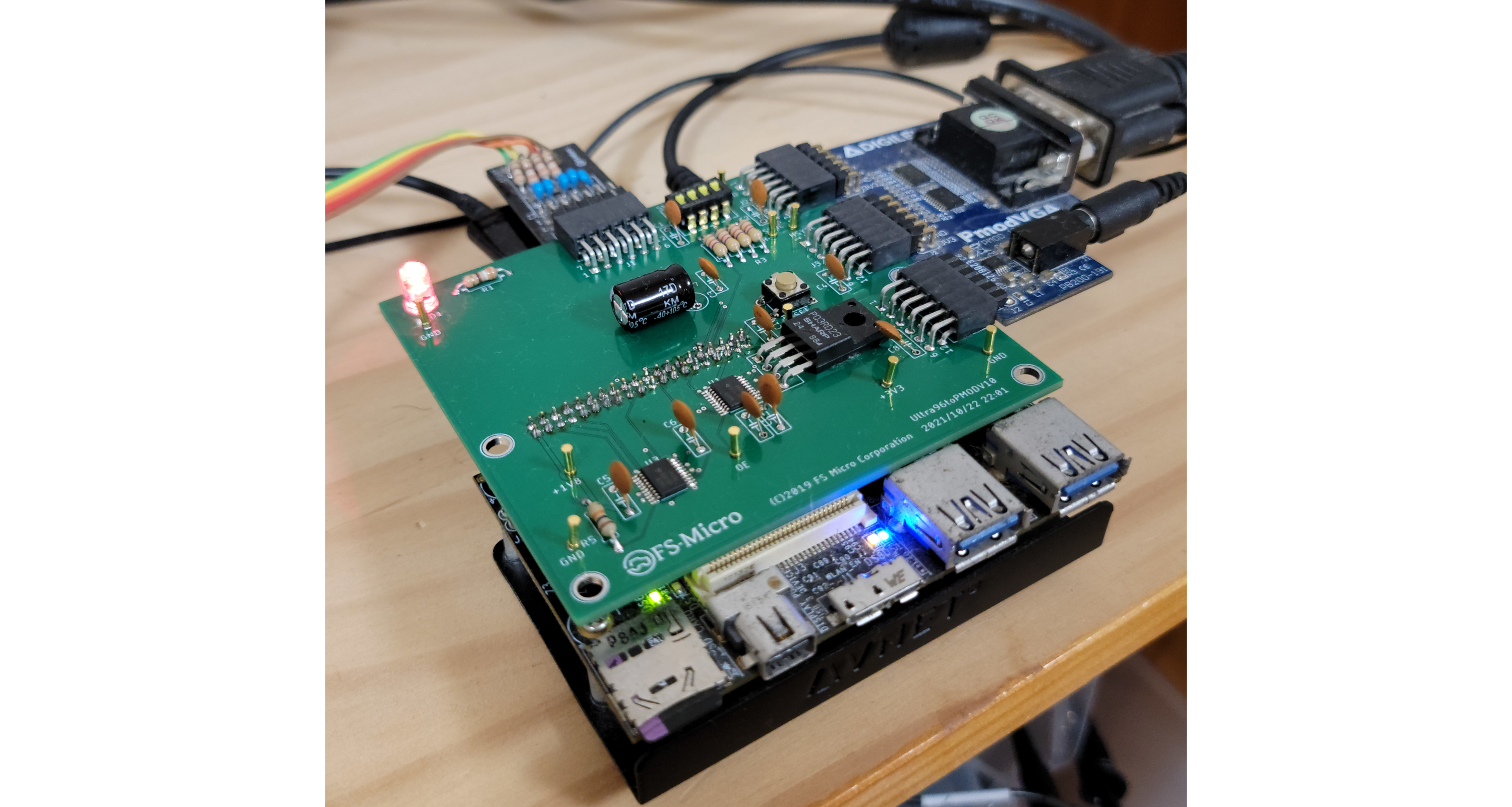

以下は、最新版(V10)ボードで実際に動作させているところです。

1.4.4 PMOD VGAボード

Digilent製PMOD仕様のVGAインタフェースボードで8.99 USDです。ただしVGAモニタが最近は見当たらなくなっているため、写真のようにVGAからHDMIへの変換ケーブルを通して、その先にHDMIケーブルとHDMIモニタを接続しています。

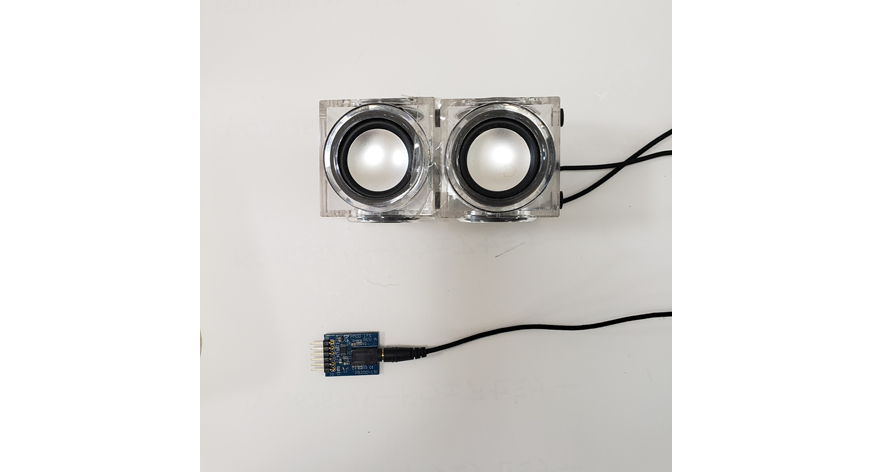

1.4.5 PMOD I2Sボード

Digilent製PMOD仕様のオーディオインタフェースボードです。I2Sシリアルインタフェースを持ち、シリアルDACが搭載されているものです。オーディオケーブルで、アンプ搭載のマイクロスピーカを接続します。

1.4.6 スイッチ

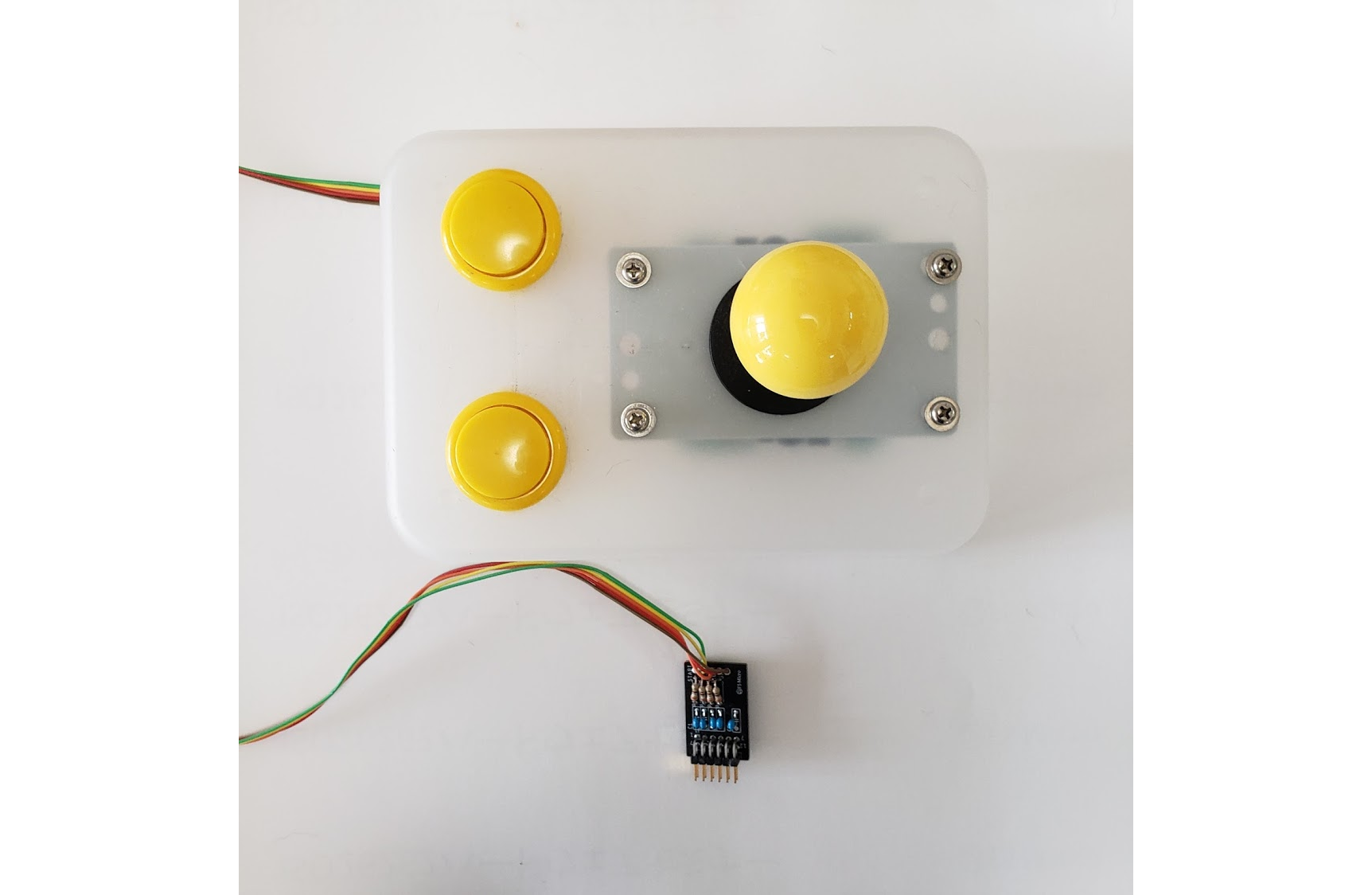

インベーダでおなじみの、自機左右移動スイッチと、スタートボタン、弾発射ボタンです。国内では少々高いため、中国から輸入しました。が、送料は結構かかります。写真は100均ショップで購入したケースに取り付けた完成形で、費用は1,000円くらいです。

ケーブルの先のボードも今回作成したもので、ジョイスティックとスイッチをPMODとインタフェースするためのボードです。

ボードのデータは以下に置いています。

https://github.com/mocapapa/JoySw

2. 手順

2.1 ソース・データダウンロード

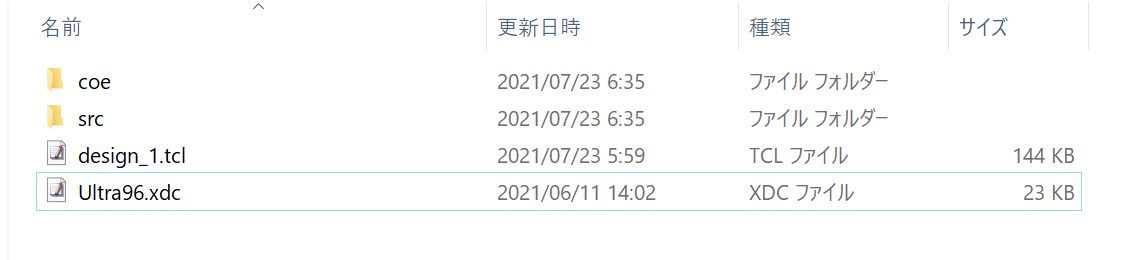

公開リポジトリから1.3に示すローカルフォルダに、下図で示す4つのフォルダ及びファイルをダウンロードします。

- coe: ROMデータ

- src: verilogソース

- design_1.tcl: ブロックデザインの記述

- Ultra96.xdc: 合成制約

2.2 ソフトブロック解説

以下のブログ記事に詳細を載せているため、ここでは割愛します。

2.3 Vivado立ち上げ

Vivadoを立ち上げ、Quick Start⇒Create Projectを実行します。

-

Project Nameに<プロジェクト名>

-

Project locationにc:/Users/<ユーザ名>/Vivado

-

Nextをクリック、RTL Project、Nextをクリック、Add Sourcesにおいて、Add Directoriesをクリック、Directoryにc:/Users/<ユーザ名>/Vivado/<プロジェクト名>/src

-

Nextをクリック、Add Constraints⇒Add Filesにおいて、c:/Users/<ユーザ名>/Vivado/<プロジェクト名>/Ultra96.xdc、Nextをクリック

-Default Part⇒Boards⇒Ultra96-V2 Single Board Computerをクリック、Next、Finish

注意点

- <プロジェクト名>にはスペースや記号を避けてalphabet大文字小文字のみにした方がいいようです。また、長さも重要で、16文字程度ではOKでしたが、付加情報をつけて26文字にしたらスクリプトの最後でエラーになりました。フォルダ名の長さも関係がありそうです。あまり深いパス名だとNGのようです。

- Ultra96V2が見つからない場合は、board_filesが不足しているので、GithubからUltra96V2のboard_filesを探してきて、C:Xilinx\Vivado<版数>\data\boards\board_files\の下に配置してください。

2.4 ブロックデザインの作成

Flow Navigator⇒IP INTEGRATOR⇒Create BLock Designを実行し、空のブロックデザインを作成します。

2.5 トップデザインの作成と設定

- BLOCK DESIGN⇒Sources⇒design_1を右クリックし、Create HDL Wrapper⇒Let Vivado manage wrapper and auto-updateを選択、OK

しばらく待ちます。

- design_1_wrapperを右クリックし、Set As Topをクリックします。

2.6 ブロックデザインの作成

- Diagram⇒Reduced Jogsを選択

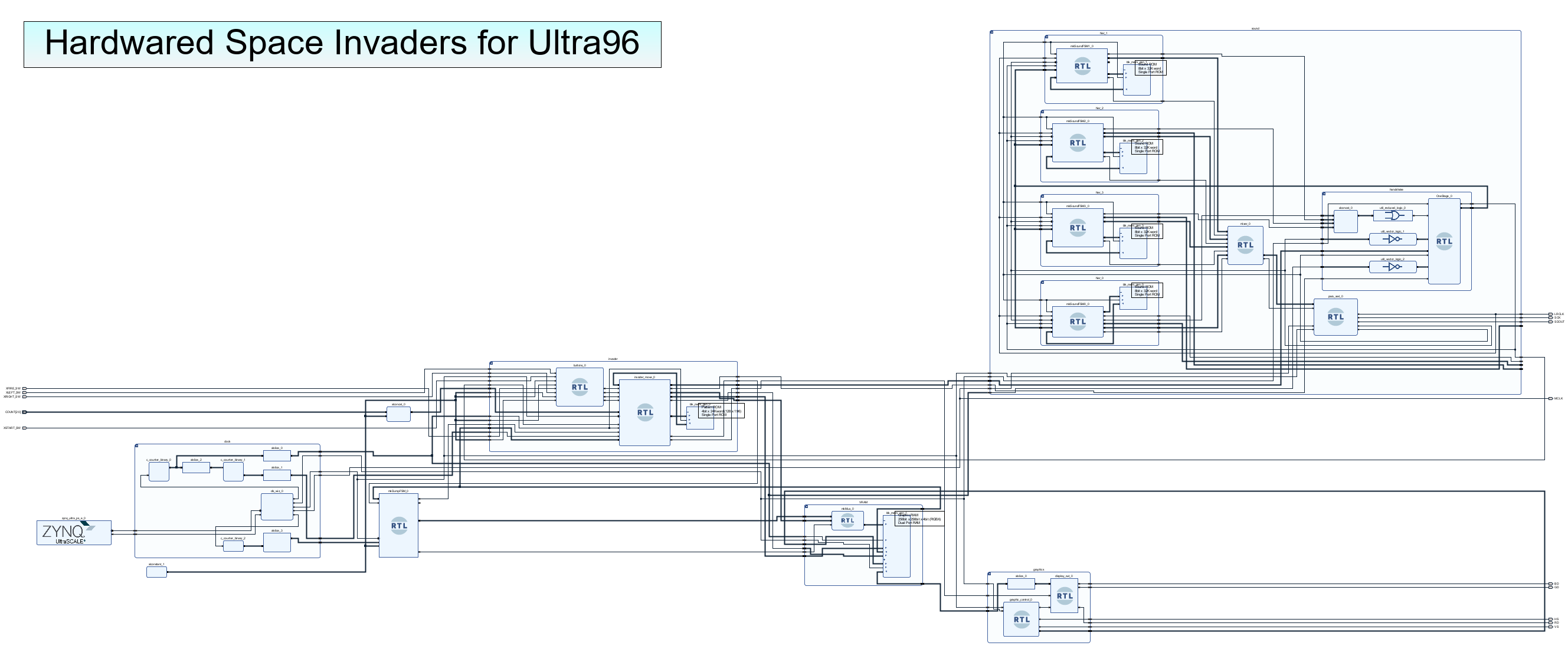

- Tools⇒Run TCL Script⇒design_1.tclを選択し、OK

2.7 ダイアグラムレイアウトを整える

- Diagramの何もない場所で右クリックし、Expand/Collapse⇒Expand All

- 再度何もない場所で右クリックし、Regenerate Layout

- タイトルコメントを右クリックし、Format Comment⇒Text sizeに64、Box fill colorに204,255,255とし、OK

2.8 合成、配置配線、ビットストリーム生成

- Flow Navigator⇒PROGRAM AND DEBUG⇒Generate Bitstreamをクリック

2.9 FPGAへのダウンロード

Ultra96 FPGAボードはフラッシュに焼きこむためにはFSBLが必要なようで、ノーソフトウエアを標榜するためには避けたいところです。従って、毎回ダウンロードすることになるので、その手順を示します。

- Flow Navigator⇒PROGRAM AND DEBUG⇒Open Hardware Manager⇒Open Targetをクリックし、Auto Connectを選択。

- Program Device⇒xczu3_0をクリック

これにより、FPGAに対してシリアルでビットストリームがダウンロードされ、実行されます。

さらに、Artyボードでは搭載Flashにビットストリームを焼くことができ、パワーオンでゲームを開始することができます。