概要

PynqをあくまでもFPGAとして利用する方向けに、Vivado上でプロジェクトを作成しPynqに乗っている4つのLEDを光らせる手順を説明します。

学校のFPGAの実験を終えたあとPYNQを買った後輩が多くいたので、PYNQでもFPGA開発を続けられるようにまとめました。

環境

Windows 10 Pro 1709

PYNQ-Z1

VivadHL 2017.4 Web Pack

ボードファイルの追加

https://github.com/cathalmccabe/pynq-z1_board_files

こちらのリポジトリをクローンし pynq-z1フォルダーを

Vivadoのインストール先\data\boards\board_files

例:C:\FPGA\Xilinx\Vivado\2017.4\data\boards\board_files

このボードファイルはPSのプリセットや周辺回路のピン設定などを含んでいます。

プロジェクトの作成

Vivadoを立ち上げ「File」から「New Project」を選択します。

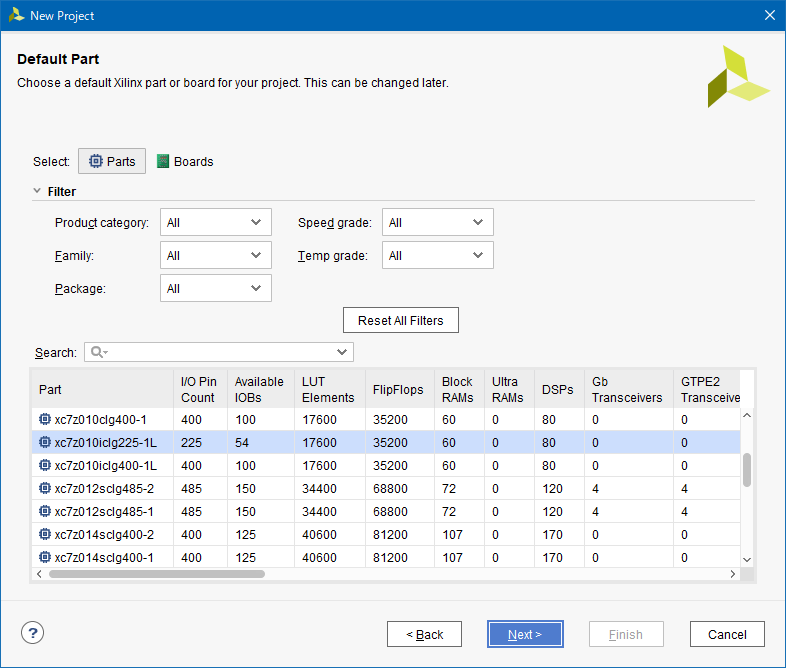

とりあえずプロジェクトの保存先などを適当に埋めファイルを追加せずに「Default Part」画面まで進めます。

「Select」の「Boards」を選択するとPYNQ-Z1という項目が追加されていると思うのでこちらを選択しNextを押します。

確認画面が出るので内容を確認し「Finish」を選択します。

Lチカ回路を作成

左側「Flow Navigator」から「PROJECT MANAGER」内の「ADD Source」を選択します。

「Add or create design sources」にチェックが入っていることを確認し次へ

「Create File」を選択しVerilogファイルを作成します。

名前は適当に入力し「OK」を押します。

最後に「Finish」を押してダイアログを閉じます。

モジュールの定義を入力される画面が表示されるのでクロック、リセット(負論理)、LED用出力(4bit)を追加します。

内容を確認して「OK」を押します。

なぜか、後述する方法でVerilogモジュールを直接ブロックデザインにいれると正論理rstが負論理として扱われるのでrstnとし、負論理リセットとしています。

作成されたverilogファイルを開き適当に作成します。

今回はカウンターを用意しそれを元にLEDを光らせます。

module led(

input clk,

input rstn,

output [3:0] led

);

reg [25:0] count;

always @(posedge clk) begin

if (~rstn) count <= 26'd0;

else count <= count + 26'd1;

end

assign led[0] = count[25];

assign led[1] = count[24];

assign led[2] = count[21];

assign led[3] = count[15];

endmodule

ブロックデザインの作成

左側「Flow Navigator」から「IP INTEGRATOR」内の「Create Block Design」を選択し、表示されるダイアログに名前などを入力して「OK」を押します。

まずはPS(Processing System)を追加します。

右クリックして「AddIP」を選択し、「ZYNQ7 Processing System」を選択してPSを追加します。

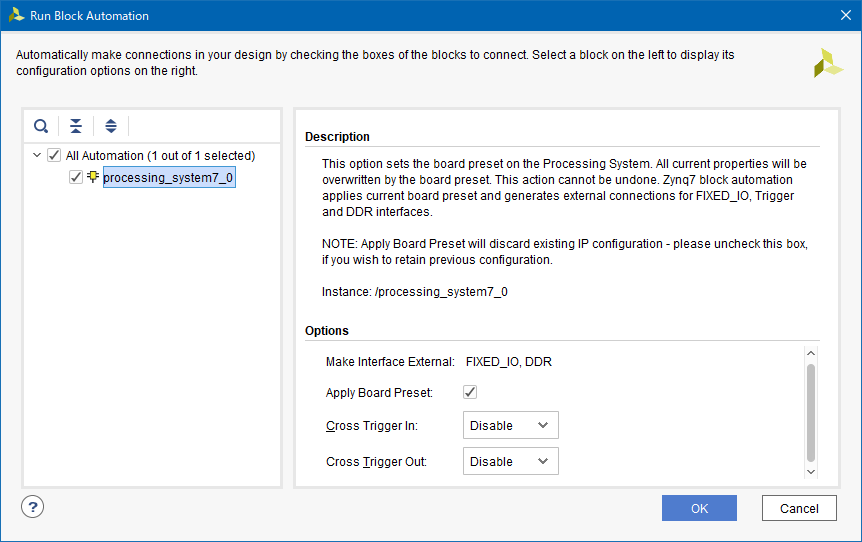

次に上部に表示されている「Run Block Automation」を選択します。

表示されるダイアログはデフォルトのまま「OK」を選択します。

続けて先ほど作成したLチカ回路を追加します。

Diaglam上で右クリックし「Add Module」を選択します。

先ほど作成した回路が認識されていると思うので選択し「OK」を押します。

ブロック図がこのようになると思います。

クロックやリセットを自動で接続するため、上部に表示されている「Run Connection Automation」を選択します。

デフォルトのまま「OK」を選択します。

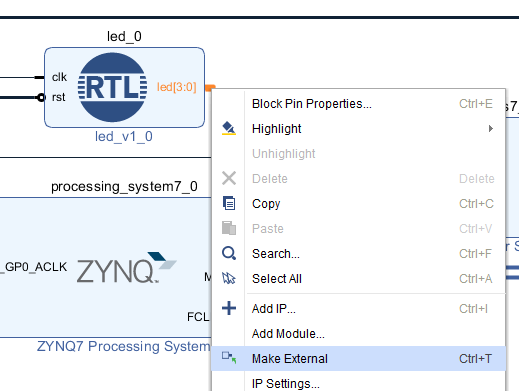

Lチカ回路の「led[3:0]」を外部に接続するため「led[3:0]」を右クリックし「Make External」を選択します。

PSの「M_AXI_GP0_ACLK」が自動配線されていない場合(上図)は、「M_AXI_GP0_ACLK」と「FCLK_CLK0」を接続してください。

これでブロック図は完成です。

「Source」タブのブロックデザインを右クリックし「Create HDL Wrapper」を選択し、ラッパーを作成します。

論理合成

「Flow Navigator」から「SYNTHESIS」内の「Run Synthesis」を選択し、論理合成します。

IOピンの設定

論理合成が終わったら「Flow Navigator」から「SYNTHESIS」内の「Open Synthesiszed Design」を選択し、右上のレイアウト選択を「I/O Planning」にします。

LEDピンの設定をする必要があるので下部「I/O Ports」内の「led_0」を開きます。

この表のPackagePinで足のピンを指定します。

PynqのLEDは回路図から以下のように対応しています。

| LED番号 | ピン番号 |

|---|---|

| 0 | R14 |

| 1 | P14 |

| 2 | N16 |

| 3 | M14 |

その為、「led_0[0]~[3]」のPackagePinは上のピン番号を選択します。

また、「I/O Std」(入出力規格)がデフォルトのままなので3.3Vである「LVCMOS33」を選択します。

最終的にIOの設定は図のようになると思います。

配置配線&ビットストリームの作成

「Flow Navigator」から「IMPLEMENTATION」内の「Run Implementation」を選択し、配置配線を行います。

デザイン制約ファイル(XDC)がない場合は作成する画面が表示されるので適当に名前を入れて「OK」を選択します。

作成されたXDCファイルを開くと先ほど入力したIOの設定が反映されていると思います。

set_property PACKAGE_PIN R14 [get_ports {led_0[0]}]

set_property PACKAGE_PIN P14 [get_ports {led_0[1]}]

set_property PACKAGE_PIN N16 [get_ports {led_0[2]}]

set_property PACKAGE_PIN M14 [get_ports {led_0[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_0[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_0[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_0[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_0[0]}]

配置配線が終わったら、「Flow Navigator」から「PROGRAM AND DEBUG」内の「Generate Bitstream」を選択し、ビットストリームを作成します。

動作確認

今回はPSからクロックを取り出しているため、PSを起動する必要があります。

「File」から「Export」を選択し「ExportHardware」でビットストリームをエクスポートし「Launch SDK」でSDKを立ち上げます。

適当なCプログラムを作成し、ビットストリームをFPGAに書き込みCプログラムを実行してください。

SDK周りは気が向いたらまとめます。

うまく動けばこんな感じで動作するはずです。

Lチカ pic.twitter.com/eIjBWtwiJY

— mmitti (青ペンギン) (@mi_mmitti) 2018年2月11日

資料

pynqの回路図

https://reference.digilentinc.com/_media/reference/programmable-logic/pynq-z1/pynq-z1_sch.pdf