情報(と頭の)整理を兼ねて、先日、3月21日から行われたGTC22で発表された、NVIDIA Hopperアーキテクチャについて纏めていこうと思います。

なお、本投稿はNVIDIA H100 のWhitepaperの内容をすべて完璧に網羅するというよりは、そこからエッセンスを抽出し個人的な備忘録として纏めたものになります。typo等はご容赦下さい。

はじめに

本ブログの元情報は以下にありますので、この簡易まとめをみてご興味持たれた方はぜひ本家をご確認下さい。

(注:2と3のリンクはGTCに登録された方のみ閲覧可能です。暫くするとどなたでも見れるようになるようです)

- NVIDIA Hopper Architecture In-Depth

- GTC S41489 Optimizing CUDA Applications for NVIDIA Hopper Architecture

- GTC S42663 Inside the NVIDIA Hopper Architecture

NVIDIA H100 GPU 概要

AIとHPCの為の次世代GPU

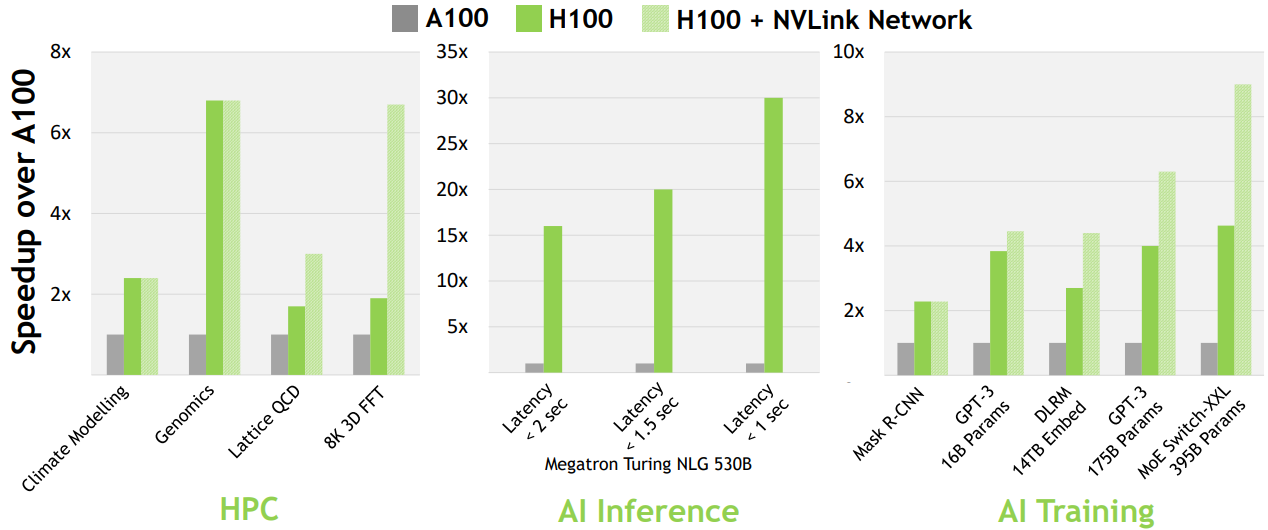

NVIDIA H100は、大規模AIおよびHPCの為の前世代のA100と比較し飛躍的な性能向上を遂げた第9世代のデータセンターGPUです。NVIDIA Hopper Architecture In-Depthブログでは、現在主流のAIやHPCワークロードにおいて、Infinibandインターコネクトを搭載したH100は1つ前の世代のA100と比較した際に最大30倍の性能が出る。また後述のNVLink Swichインターコネクトを組み合わせた場合、更に3倍性能が向上する可能性があると述べられています。

図1: H100 enables next-generation AI and HPC breakthroughs

※NVIDIA Hopper Architecture In-Depthより引用

GTC S42663 Inside the NVIDIA Hopper Architectureのセッション冒頭でMichael Andersch氏は以下のようにコメントしています。(聞き取りミスはご容赦下さい)

Modern accelerated computing is rarely about one individual GPU anymore. Instead, the most demanding applications today require 100s, sometimes 1000s of GPUs to execute. And each of those GPUs in turn may contain hundreds of individual processors. So designing these hierarchical systems and enabling programmers to harness thesir performance requires a fundamental shift in how we build these machines and express our programs.

図3: Features for outstanding performance, scalability and data center security

※GTC S42663 Inside the NVIDIA Hopper Architectureより引用

現在主流のAIやHPCワークロードでは、数100場合によっては数1000のGPUが必要であり、それらのGPUには個別に多数のプロセッサが搭載されている。このような階層システムでプログラマがパフォーマンスを引き出す為には、マシンの構築方法、およびプログラミングモデルそのものを根本的に変える必要があると述べており、「Hopper SM」「Hierarchy」「Asynchrony」「SuperPods」「Cloud Computing」と大きく5つに分けて説明していく事が最初に言及されています。

NVIDIA H100はGPU単体の性能は勿論の事、数1000ものGPUを必要とするワークロードでのスケーリングについても意識して設計されています。

まず5つの項目を細かく見る前に、NVIDIA H100 GPUの全体像・概要を確認していこうと思います。

NVIDIA H100 GPU の主要機能

H100の主要機能を以下に列挙します。前節で説明した通り、GPU単体の性能に関係する機能は勿論の事、マルチノードマルチGPU環境でのスケーリングに関係する機能やコンフィデンシャルコンピューティングに関係する機能追加もありますね。

- SMの性能・効率性の向上

-

Transformer Engineの搭載

- 新しくTransformerモデルの学習と推論を高速化する機構が追加されました

-

HBM3メモリの採用

- 前世代に比べ約2倍の帯域幅を実現。3TB/秒のメモリバンド幅を実現できます。

-

50MBのL2キャッシュを搭載

- L2キャッシュサイズが前世代(A100)から更に大きくなりました。

-

第2世代のMIGテクノロジー

- 第1世代のMIGと比較して、GPUインスタンスあたり約3倍の計算能力と約2倍のメモリ帯域幅を提供します。MIGレベルのTEE(trusted execution environment)の機能が初めて提供されます。

-

コンフィデンシャル・コンピューティングのサポート

- ユーザーデータの保護、ハードウェアおよびソフトウェア攻撃からの防御、仮想化およびMIG環境における仮想マシン(VM)の相互分離と保護がより強化されます。

-

第4世代のNVLink

- 900 GB/秒の総バンド幅。

-

第3世代のNVSwitch

- 前世代の7.2 Tbits/secから13.6 Tbits/secに向上。

- NVLINK Switchインターコネクトテクノロジー

-

PCIe gen5の採用

- gen4と比べて、2倍の帯域を実現。総帯域幅が128GB/秒(各方向64GB/秒)になります。

図2: HOPPER H100 TENSOR CORE GPU

※GTC S42663 Inside the NVIDIA Hopper Architectureより引用

- gen4と比べて、2倍の帯域を実現。総帯域幅が128GB/秒(各方向64GB/秒)になります。

NVIDIA H100 GPU アーキテクチャ

TSMC 4Nプロセスを採用したH100は、TSMC 7nm N7 プロセスを採用した前世代の GA100 GPU と比較して、GPU コア周波数の向上、ワット当たりの性能向上、GPC、TPC、SM の搭載を実現しました。

図 3 は、144 個の SM を搭載した「完全版GH100 GPU」を示しています。

図3: GH100 Full GPU with 144 SMs

※NVIDIA Hopper Architecture In-Depthより引用

H100は「完全版GH100 GPU」以外に「NVIDIA H100 SXM5 GPU」と「NVIDIA H100 PCIgen5 GPU」が存在し、それぞれSM数やメモリなどのスペックが若干異なるとの事です。

NVIDIA A100発表時にも、「full implementation of the GA100 GPU」と「A100 Tensor Core GPU implementation of the GA100 GPU」が存在し、スペックは異なるという説明がありましたが、NVIDIA H100も同じのようです。

| full implementation of the GH100 GPU | NVIDIA H100 GPU with SXM5 | NVIDIA H100 GPU with a PCIe Gen 5 | |

|---|---|---|---|

| GPC数 | 8 | 8 | 7 or 8 |

| TPC数 | 72 | 66 | 57 |

| SM数 | 144 | 132 | 114 |

| FP32 CUDA Cores per SM | 128 | 128 | 128 |

| FP32 CUDA Cores per GPU | 18432 | 16896 | 14592 |

| TensorCore per GPU | 576 | 528 | 456 |

| メモリ | 6 HBM3 or HBM2e stacks, 12 512-bit memory controllers | 80 GB HBM3, 5 HBM3 stacks, 10 512-bit memory controllers | 80 GB HBM2e, 5 HBM2e stacks, 10 512-bit memory controllers |

| L2キャッシュ | 60 MB | 50 MB | 50 MB |

表1: GH100 Full GPU/NVIDIA H100 SXM5 GPU/NVIDIA H100 PCIe Gen5 GPUの比較

※NVIDIA Hopper Architecture In-Depthより引用

Compute Capability (別の世代との比較)

性能比較

次に異なるCompute CapabilityのGPUと比較しながら、NVIDIA H100の理論性能をを見てみます。

NVIDIA H100のTensorCoreはTF32、FP16に加えて、新しくFP8がサポートされています。(FP8の詳細については別途触れようと思います)

また倍精度、単精度共に前世代のA100に比べて性能が大幅に向上しています。

| NVIDIA A100 | NVIDIA H100 SXM5 | NVIDIA H100 PCIe | |

|---|---|---|---|

| Peak FP641 | 9.7 TFLOPS2 | 30 TFLOPS | 24 TFLOPS |

| Peak FP64 Tensor Core1 | 19.5 TFLOPS2 | 60 TFLOPS | 48 TFLOPS |

| Peak FP321 | 19.5 TFLOPS2 | 60 TFLOPS | 48 TFLOPS |

| Peak FP161 | 78 TFLOPS2 | 120 TFLOPS | 96 TFLOPS |

| Peak BF161 | 39 TFLOPS2 | 120 TFLOPS | 96 TFLOPS |

| Peak TF32 Tensor Core1 | 156 TFLOPS/312 TFLOPS2 | 500 TFLOPS/1000 TFLOPS3 | 400 TFLOPS/800 TFLOPS3 |

| Peak FP16 Tensor Core1 | 312 TFLOPS/624 TFLOPS2 | 1000 TFLOPS/2000 TFLOPS3 | 800 TFLOPS/1600 TFLOPS3 |

| Peak BF16 Tensor Core1 | 312 TFLOPS/624 TFLOPS2 | 1000 TFLOPS/2000 TFLOPS3 | 800 TFLOPS/1600 TFLOPS3 |

| Peak FP8 Tensor Core1 | - | 2000 TFLOPS/4000 TFLOPS3 | 1600 TFLOPS/3200 TFLOPS3 |

| Peak INT8 Tensor Core1 | 624 TOPS/1,248 TOPS2 | 2000 TOPS/4000 TOPS3 | 1600 TOPS/3200 TOPS3 |

表2: GPU preliminary performance specs: V100 vs. A100 vs. H100

※NVIDIA Hopper Architecture In-Depthより引用

スペックの比較

次に異なるCompute CapabilityのGPUと比較しながら、NVIDIA H100のスペックを見てみます。

NVIDIA H100のCompute Capabilityは9.0です。SMあたりの最大スレッド数は2048であり、A100やV100と同じです。SM辺りのレジスタ数も65536で前世代と変わりません。

数字を眺めていて変化があるのは、SM辺りのFP32コア数です。V100, A100が、64 FP32コア/SM だったのに対して、H100は128 FP32コア/SM とSMあたりのFP32コアの数が2倍に増えています。SM辺りのレジスタ数は変わっていない為、必然的に1 FP32コアあたり使用可能なレジスタ数は1/2になっている所にご注意下さい。

またSMあたりのシェアードメモリのサイズはH100で228KBになり、約1.4倍に増加しています。

表3: Compute capability: V100 vs. A100 vs. H100

※NVIDIA Hopper Architecture In-Depthより引用

長くなったので、この辺りで一度記事を切りたいと思います。

-

Preliminary performance estimates for H100 based on current expectations and subject to change in the shipping products ↩ ↩2 ↩3 ↩4 ↩5 ↩6 ↩7 ↩8 ↩9 ↩10

-

A100 Tensor Core GPU's peak rates are based on the GPU boost clock. ↩ ↩2 ↩3 ↩4 ↩5 ↩6 ↩7 ↩8 ↩9

-

Effective TFLOPS / TOPS using the Sparsity feature ↩ ↩2 ↩3 ↩4 ↩5 ↩6 ↩7 ↩8 ↩9 ↩10