この記事について

Zynqのプログラミングを行うとき、ユーザーガイドを見たり、Googleで検索する。

でも実際に必要な情報はあまり見つからない。

さらにXILINX公式のフォーラムも、解決に至っていない投稿ばかり…

そこで、私の知識をメモ代わりに投稿する。また、シリーズで紹介しようと思う。

(私はプログラミング初心者のため、初心者向けの記事になると思う。)

まず、Zynqって何?

これは、Qiitaでもよく記事にされているのでさらっと紹介。

-

Zynq

-

XILINX社がリリースしている、PS(Processing System)部とばれるCPUと、PL(Programmable Logic)部と呼ばれるFPGAがセットになったSoC(System on Chip)デバイスのこと。

-

この記事では、開発の方針としてPS部はC言語、PL部はVHDLを使用。

-

Vivado

XILINXが提供しているZynq開発用ツール(無償ライセンス有)。

開発環境

開発用PC

- Windows10 64bit

- メモリ:32GB

- SSD:512GB

使用する評価ボード

ZYBO Z7-20

参考サイト:XILINX公式 ZYBO Z7-20

ツールのインストール

-

Vivado(私は2018.2を使用)

XILINXの開発環境であるVivadoとSDKをインストールする。

こちらも、よく記事にされているのでそちらを参照。

参考サイト:ZYBO (Zynq) 初心者ガイド (1) 開発環境の準備

※ZYBO Z7-20のボードファイルのコピペを忘れないようにすること! -

TeraTerm(私はver4.90を使用)

フリーのターミナルソフト。シリアル通信によるデバッグに使用する。

Hello Worldを画面表示

HelloWorldの表示は、(上記サイトなど)多くのサイトで取り上げられているが、最初のため細かく説明する。

1. プロジェクトの作成

Vivadoでプロジェクトを作成する。Vivadoを開いて「Create Project」を選択。

開かれたウィンドウを順番に設定していく。

「Project name」と「Project location」を設定する。

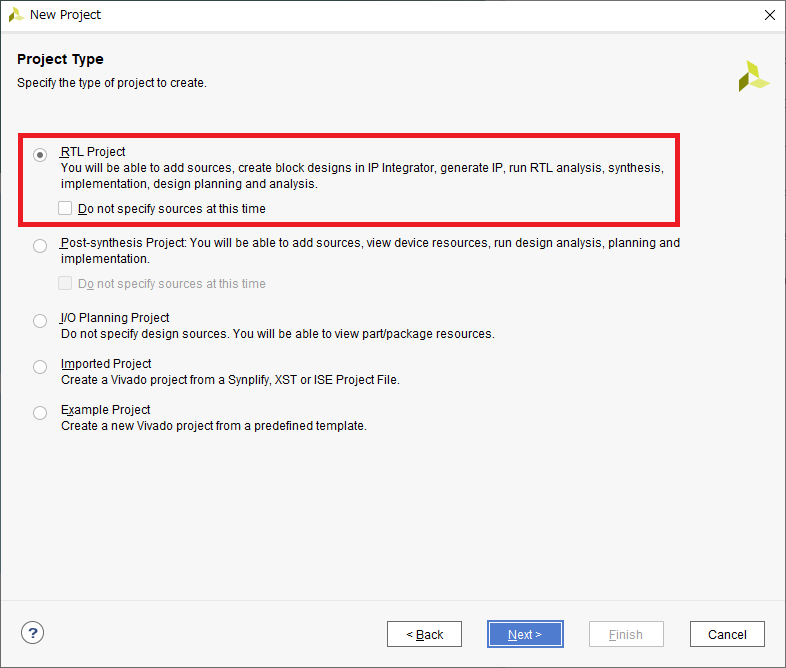

「RTL Project」を選択する。

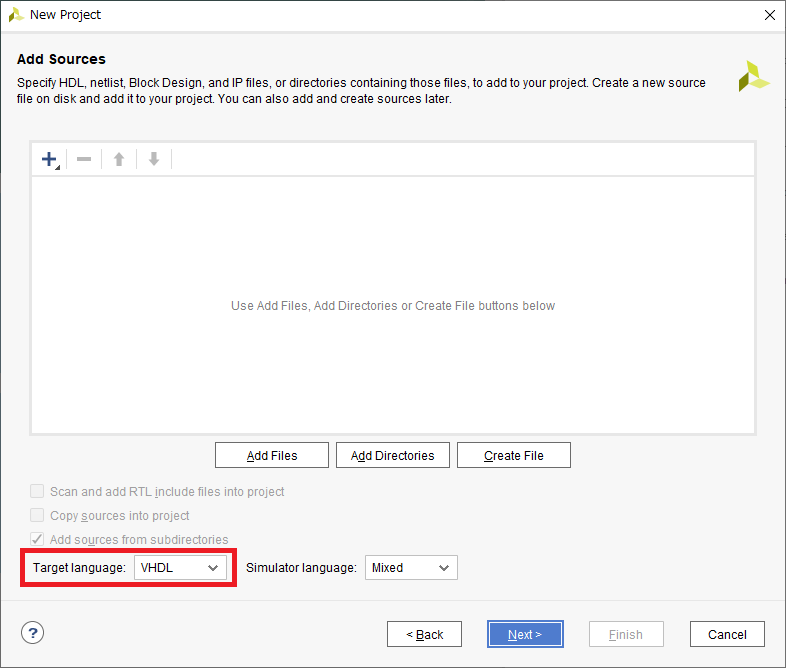

「Target Language」は「VHDL」とする。

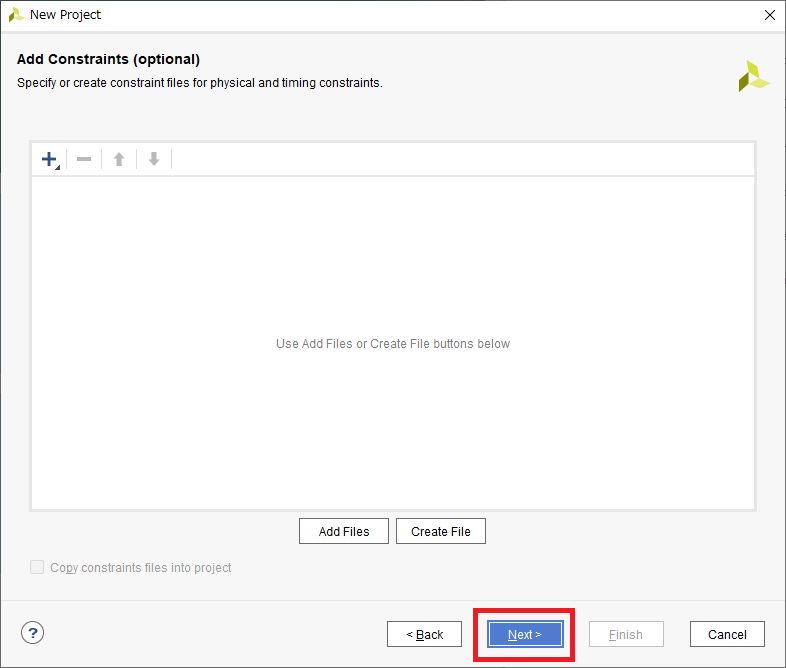

「Add Constraints」は特に設定しなくてよい。

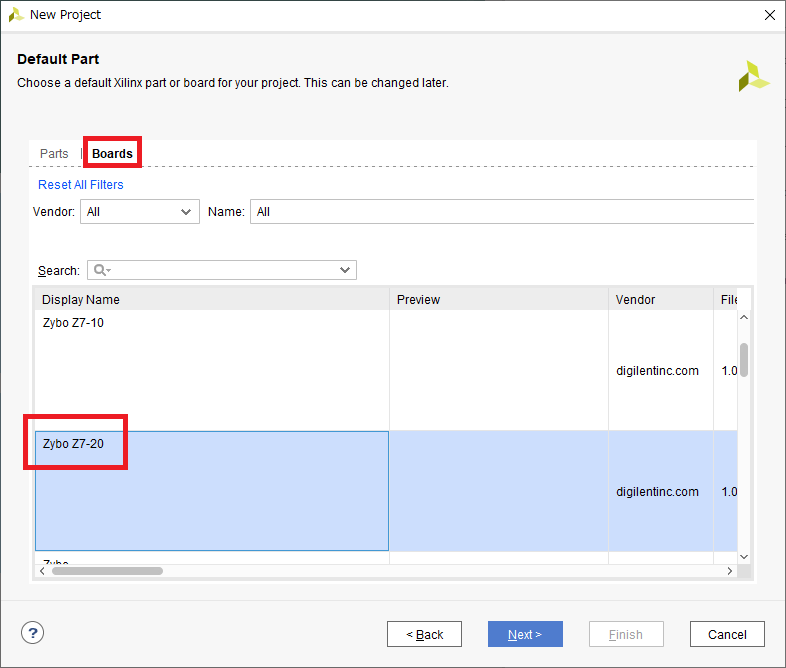

「Board」タブで「Zybo Z7-20」を選択する。

内容を確認し、問題なければ「Finish」。

2. ブロックデザインの作成

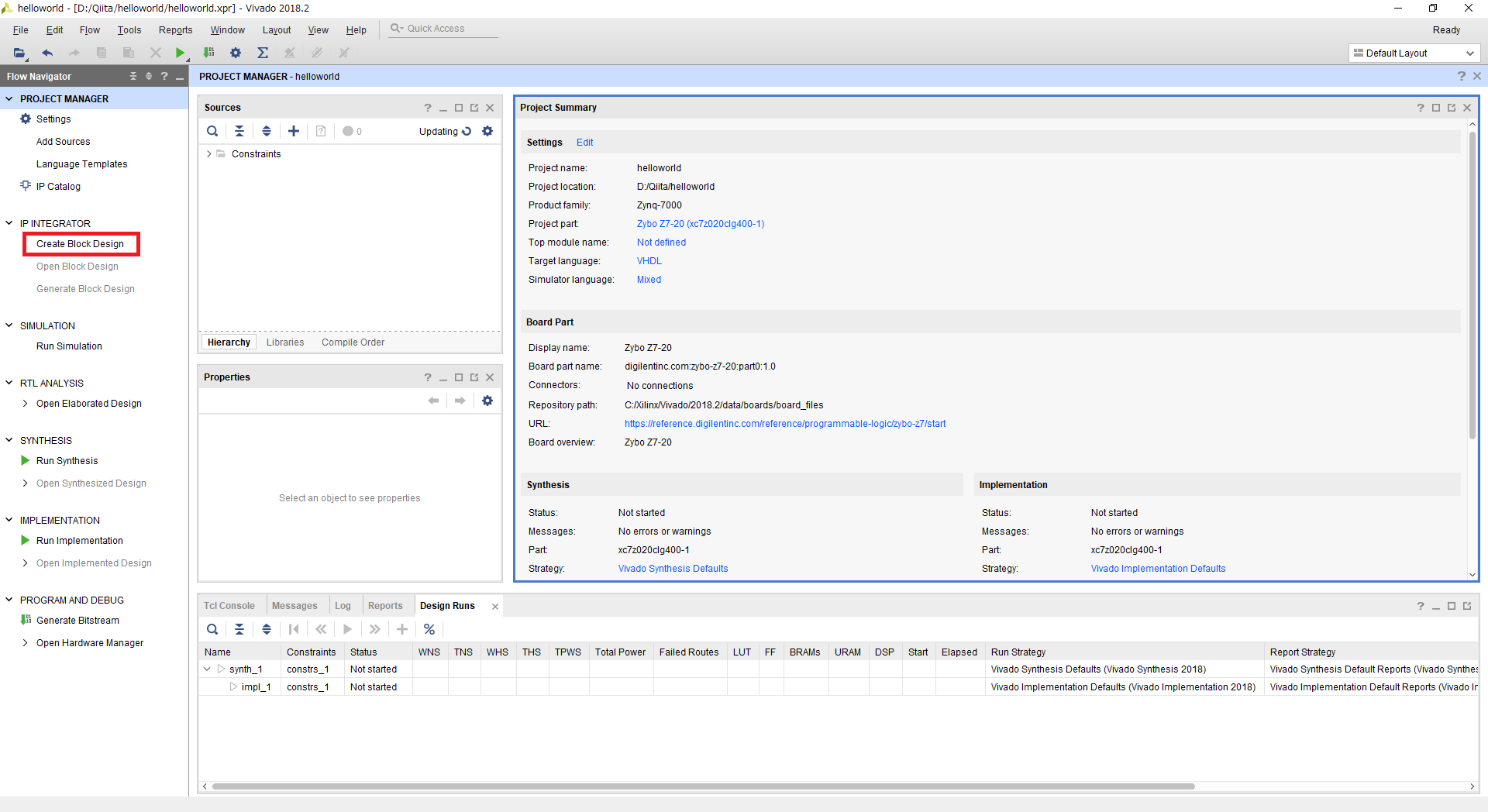

プロジェクトが作成されると、↓のような画面が出てくる。「Create Block Design」を選択してブロックデザインを作成する。

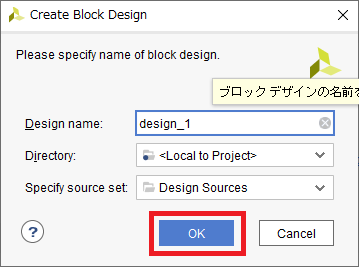

ウィンドウが開かれるため、「Design name」を設定して「OK」。(ここでは「design_1」(デフォルトのまま)とした。)

「Diagram」タブで右クリックし、「Add IP」を選択することでIPコアを追加する。

「ZYNQ7 Processing System」を選択する。これがPS部のIPコア。「PS部のIP」と呼ぶことにする。

IPコアは、FPGAの機能をひとまとまりにしたもので、ブロックデザインはIPコアをグラフィカルに線で接続して設計する。

今回はPS部の機能しか使わないのでとりあえずこれだけでOK。

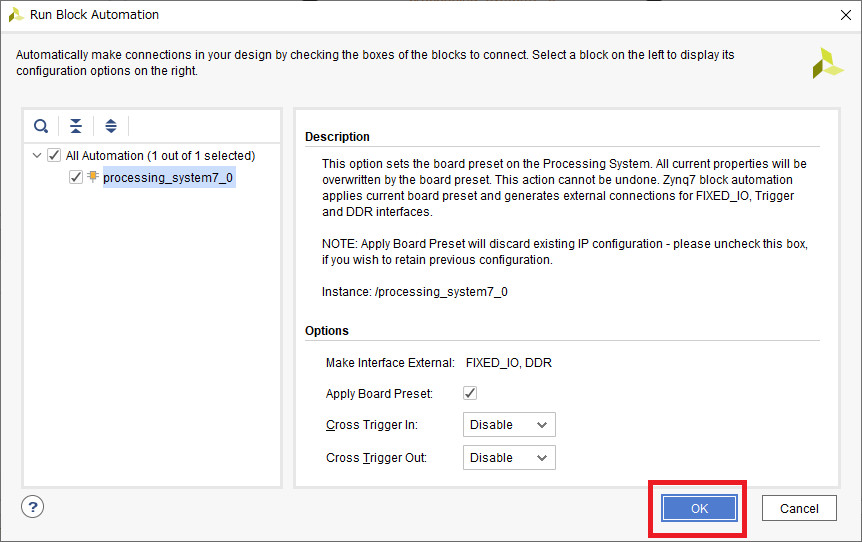

「Run Block Automation」ではPS部のIPをZYBO Z7-20向けに設定を変更してくれる。

特になにもせず、「OK」。

すると、PS部のIPからDDRメモリとIOへのバスが追加された。

「FCLK_CLK0」から線を出して「M_AXL_GPO_ACLK」に接続する。これでブロックデザインは完成。簡単だ。

「Source」タブの「Design Sources」>「design_1(design_1.bd)」を右クリックして「Create HDL Wrapper」を選択し、wrapper(ラッパー)ファイルを作成する。

3. 論理合成~ビットストリーム生成まで

wrapperファイルができたら、論理合成、配置配線、ビットストリームの生成を行う。これらを一気に実行するには、右下の「Generate Bitstream」を選択する。

「No Imolementation Result Available」ウィンドウが表示さるが、「配置配線してないよ!論理合成と配置配線もセットでやるよ?」とのことなので「Yes」を選択する。

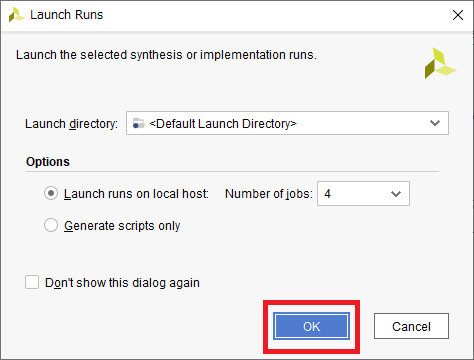

「Launch Runs」ウィンドウが表示されるが、そのまま「OK」でよい。

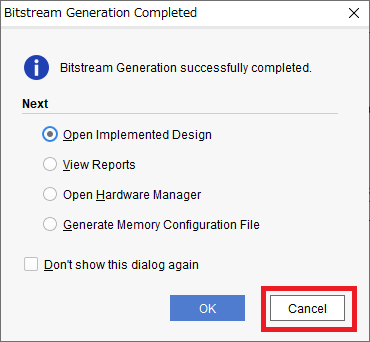

「Bitstream Generation Complete」ウィンドウが表示されれば、論理合成、配置配線、ビットストリームの生成が完了。

このウィンドウは「Cancel」で閉じる。

4. SDKの起動

Vivadoのメニュー「File」>「Export」>「Export Hardware」より、hdf(ハンドオフ)ファイルをSDKのフォルダにエクスポートする。

「Export Hardware」ウィンドウが表示されるので、「Include bitstream」にチェックを入れて「OK」。

これでプロジェクトフォルダに、「helloworld(プロジェクト名).sdk」が作られ、ファルダ内にhdfファイルが作られる。このhdfファイルにはbitファイルが含まれている。

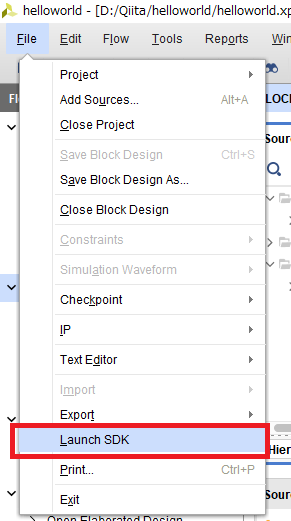

Vivadoのメニュー「File」>「launch SDK」よりSDKを起動する。「launch SDK」ウィンドウも「OK」で良い。

5. アプリケーションの作成

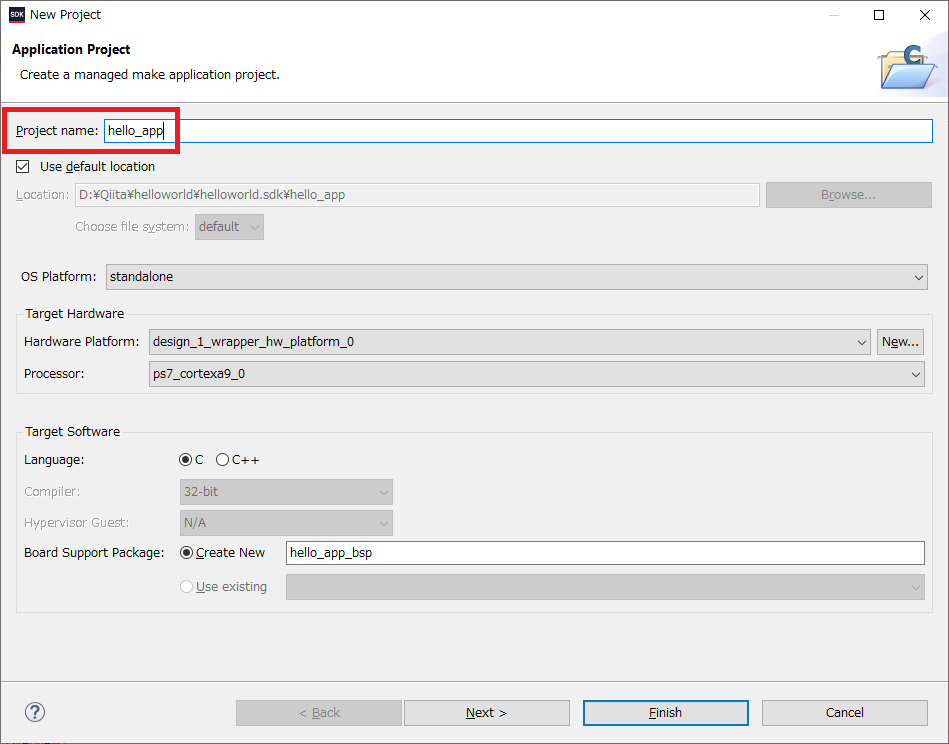

SDKが開いたら、まずアプリケーションプロジェクトを作成する。

SDKのメニュー「File」>「New」>「Application Project」を選択する。

「Project name」を設定する。(ここでは、「hello_app」とした。)それ以外は、デフォルトのまま「Next」。

「Hello World」を選択すると、HelloWorldを表示するソースコードが自動で作られる。

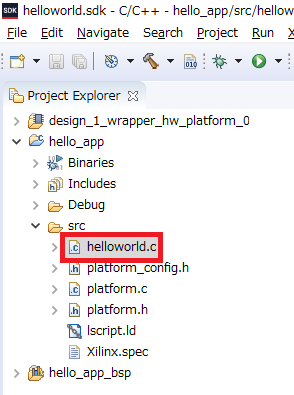

「Project Explorer」の「hello_app」>「src」>「helloworld.c」が、ソースコード。

- hello_app : アプリケーションプロジェクト

- hello_app_bsp : hello_appのBSP(ボードサポートパッケージ)

# include <stdio.h>

# include "platform.h"

# include "xil_printf.h"

int main()

{

init_platform();

print("Hello World\n\r");

cleanup_platform();

return 0;

}

6. アプリケーションの実行

アプリケーションを実行するために、まずZYBO Z7-20をPCに接続しておく。

- ZYBO基板上のジャンパJP5の「JTAG」をショート

- ZYBO基板電源近くのJ12(microUSB)とPCをケーブルで接続

- ZYBOの電源を投入

- TeraTermを起動し、ポート番号(私の場合はCOM9)とボーレート(115200)を合わせ接続

SDKに戻り、「Program FPGA」よりFPGAをZynqに焼きこむ。

「Program FPGA」ウィンドウが表示されるが、そのまま「Program」。

すると、ZYBOのDONE(LD12)緑LEDが点灯する。これでFPGAの焼きこみはOK。

今回はデバッグモードでアプリケーションを実行する。

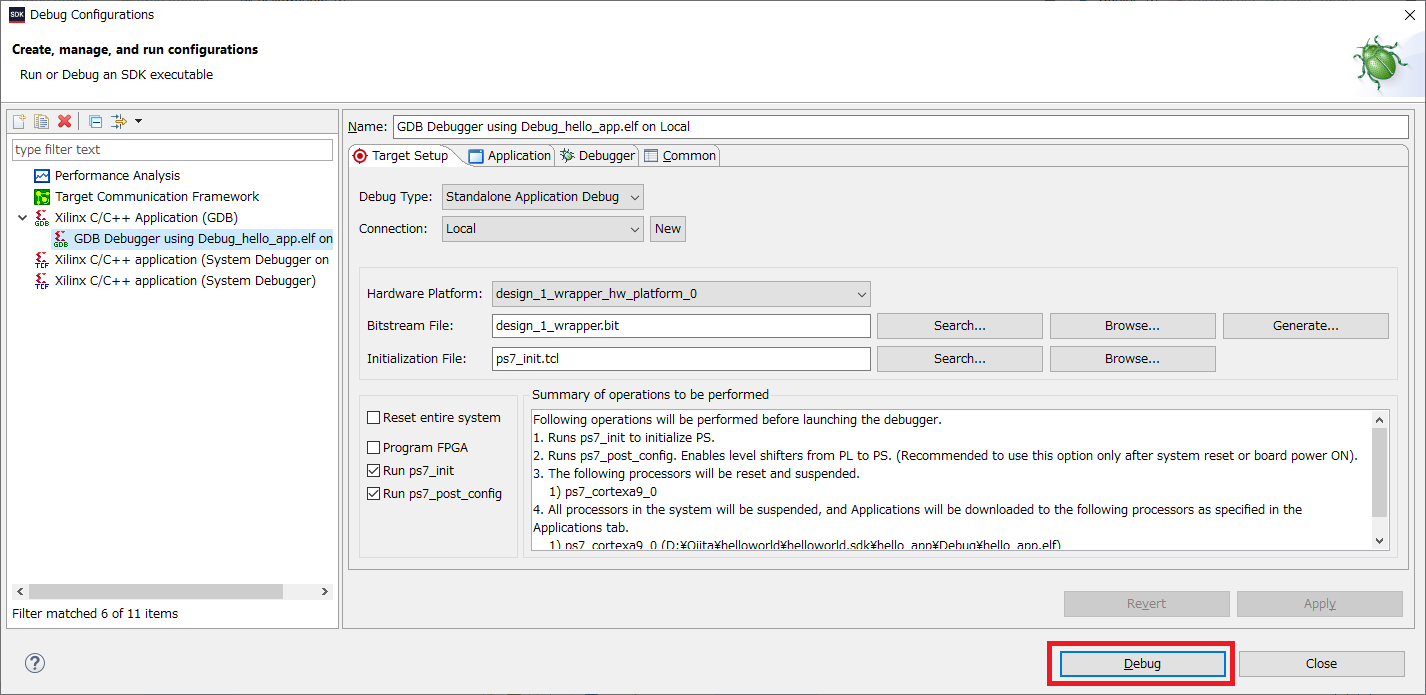

「hello_app」>「Debug As」>「Debug Configurations...」を選択。

「Xilinx C/C++ Apptication(GDB)」を右クリックして、「New」を選択。

ウィンドウが変わり、bit、tclファイル、elfファイル等の確認ができる。これで「Debug」。

すると、↓のようなウィンドウが表示されるが「OK」で良い。

ウィンドウが変わり、Runを選択するとアプリケーションが実行される。

TeraTermを確認すると、「Hello World」が表示されている。これで終了!

プロジェクト作成から、アプリケーション実行までの流れは以上のような感じである。

補足. 2回目以降の実行

2回目以降の実行は、↓のようにSDKウィンドウのRunの右の▼から実行するアプリを選べば、実行できる。

SDKのエラーやbitファイル再生成時は・・・

-

SDKのエラーが突然出た(「ライブラリが参照できない」など)

一度SDKを終了して、Vivadoからもう一度SDKを起動するとエラーがなくなることがある。 -

bitファイルを生成しなおす場合

一度Vivadoプロジェクトの「プロジェクト名.sdk」のフォルダを全て削除してからbitファイルを再生成する。

その後、もう一度SDKをVivadoから起動し、アプリケーションプロジェクトも再生成する。

(本当にこの方法しかないのだろうか・・・かなり面倒・・・) -

Vivado 2019.2

Vivado 2019.2以降は、SDKのツールがなくなり、Vitisというものになったようだ。

(この記事を書く意味とは・・・)