Low Latency Custom FPGA Accelerate

個別アプリケーション、ネットワーク運用に特化したFPGAアクセラレーション

はじめに

一部クラウドとネットワークを接続するために、GREトンネルを運用していますが、このGREトンネルはアプライアンスSwitchで接続しています。

例えばクラウドで仮想マシンを追加した場合、同様に双方向のトンネリングSwitchに対してGREトンネルのコンフィグレーション追加が必要なため管理が煩雑になっているという課題がありました。

このトンネリングネットワークはセキュリティ面で問題のない場所に配置されているので、GREトンネルDecap側をFPGAで置き換え、GREパケットであれば無条件にDecapする処理に変更することができます。そうすることで仮想マシンを追加してもネットワーク スウィッチに追加コンフィグレーションが不要となり、コンフィグ管理の煩雑さを軽減することができます。

このようなネットワークの効率的な管理のためにFPGAアクセラレートを検証・評価しました。

この資料では、特定ケースにおけるネットワーク設計・運用における効率的・実用的なFPGAアクセラレーションソリューションについて説明します。

Timing Chart - Decap

今回評価対象としたFPGAインタフェイスは、1cycleで、256bit(32Byte)パケットを受信できます。1列目は入力パケットを示します。GREパケットはL3トンネルなので2パケットまで受信すれば、decap処理を開始することができます。

Logic Analyzerを追加して確認したところ、GREトンネルの最小サイズ(ethフレーム(64) + 外側ipv4(20) + gre(4) Byte = 88 Byte)ケースで5〜7 cycleで1フレームを受信できます。またDecap 処理で2cycle分の受信データをバッファリングして 3 cycle遅延でパイプライン実装設計することができました。

State Machine

前記のDecap処理を行うために、今回は以下のようなステートマシンにて実装しています。初期状態(INIT)から、受信したパケットが処理対象であるGREであるか否かを判断して状態遷移し、valid信号の有無で待機状態とペイロード部処理状態を行き来します(WAIT↔PAYLOAD)。最後に、EndOfPacketを示すEOP状態へ遷移し、初期状態へ戻ります。

状態遷移図

プラットフォーム比較

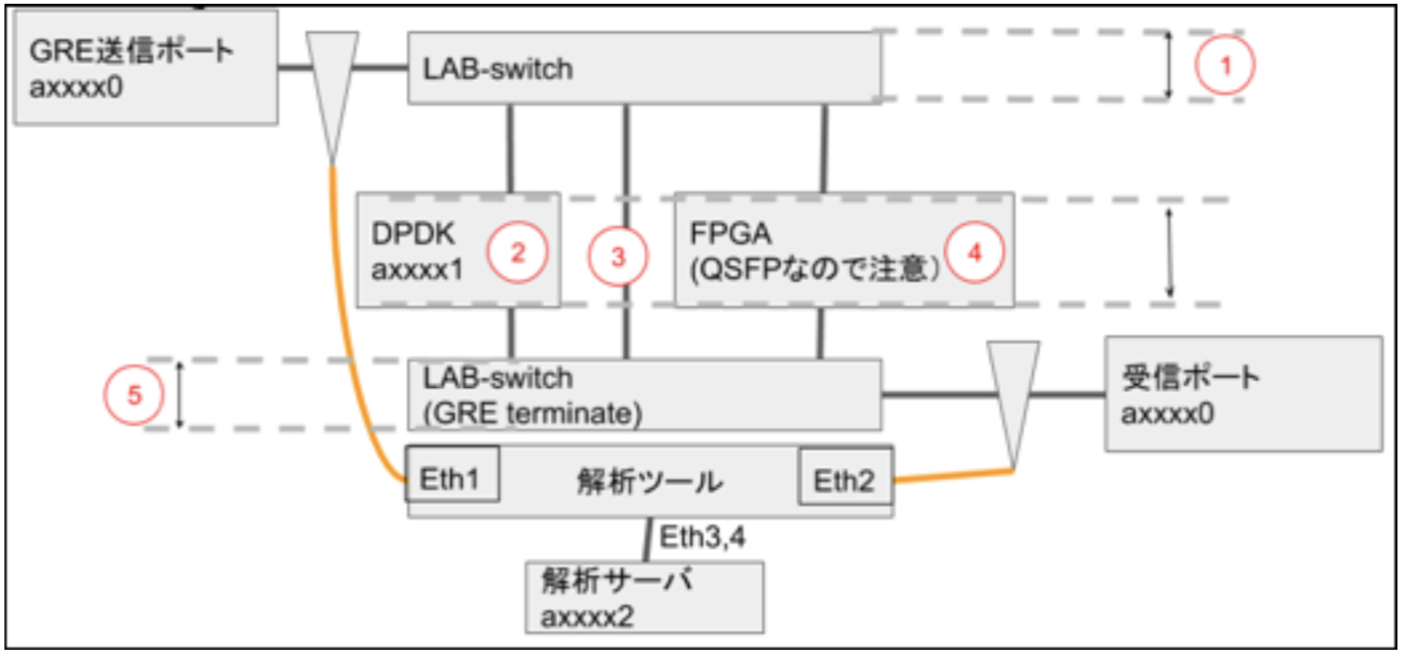

GRE - Decap処理をFPGAアクセラレートし、パフォーマンス(レイテンシ、スループット)をFPGA アクセラレート、DPDK[1]、および アプライアンスSwitch[2]間で比較します。評価トポロジを次図に示します

プラットフォーム比較結果

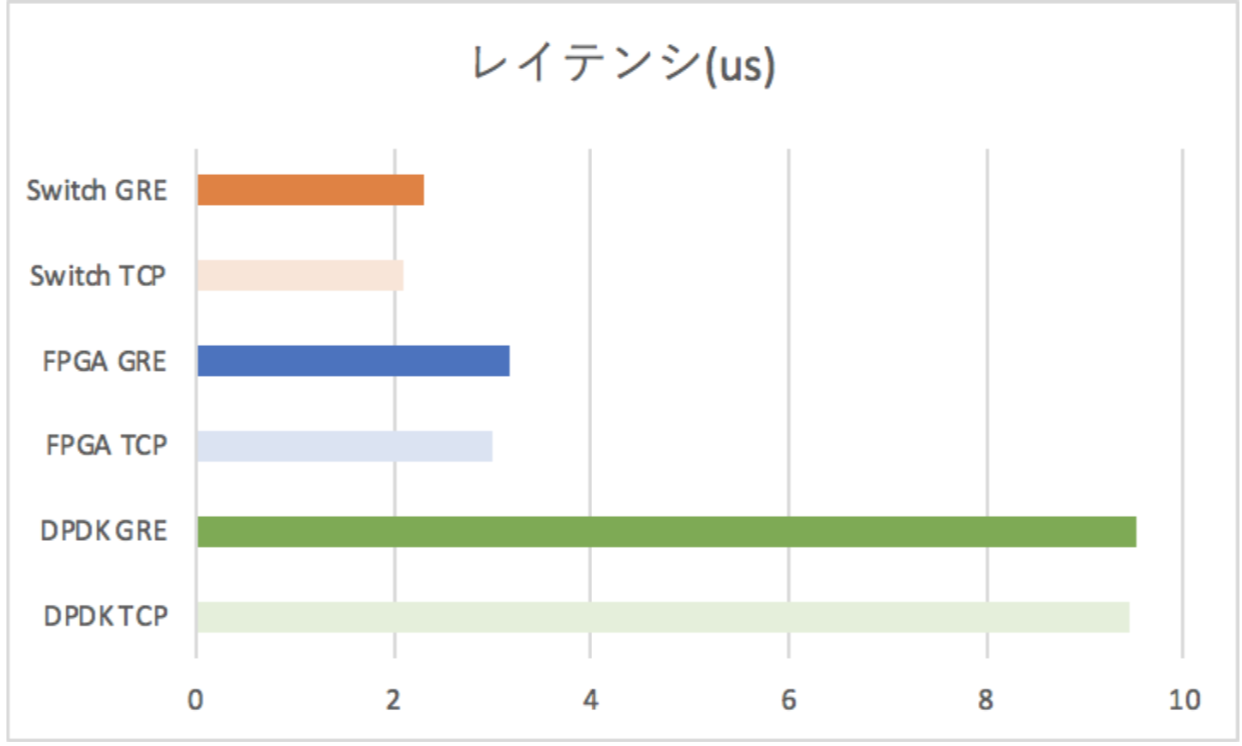

それぞれ1パケットでのレイテンシは次表のようになりました。DPDKはユーザランドソフトウェア処理であり、プールモード+バッチ処理によって高速パケットプロセッシングを実現するプラットフォームですので1パケットでレイテンシが高いのは想定通りです。そして電力消費においても、DPDK実装では、CPUをBusyLoopで占有しますのでFPGAと比較すると大幅に高くなります。

decap rateは、decap処理によるpass through(TCP)処理からのパフォーマンス悪化率((GRE - TCP)/TCP = decap rate)

プラットフォーム比較考察

消費電力、パフォーマンスの両面からFPGAによるDecap処理がもっとも効率が良いと言えます。また、DPDKによるDecap処理は消費電力さえ考えなければ、非常にコストパフォーマンスが良いと言えます。とはいえ、ソリューションには、常にメリットとデメリットの両面があり、自社チームの状況に応じたソリューションを選択することがもっとも重要だと思います。

Switch

・メリット :安定性と人的リソースの配置しやすさ

・デメリット:コンフィグ管理が煩雑(このケースでは)

FPGA

・メリット :消費電力、パフォーマンス効率

・デメリット:人的リソース配置難、開発環境等

DPDK

・メリット :人的リソース配置しやすい

・デメリット:開発環境の追随、消費電力、レイテンシ

Switchモジュール論理構成

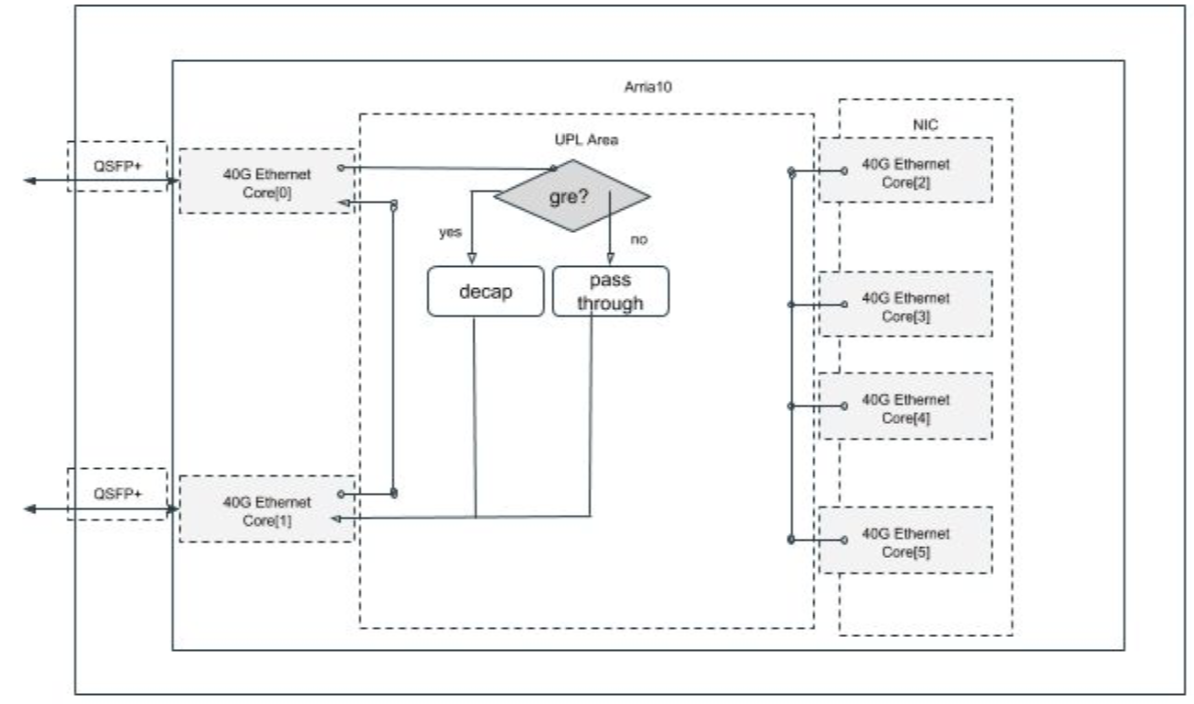

FPGAモジュール論理構成

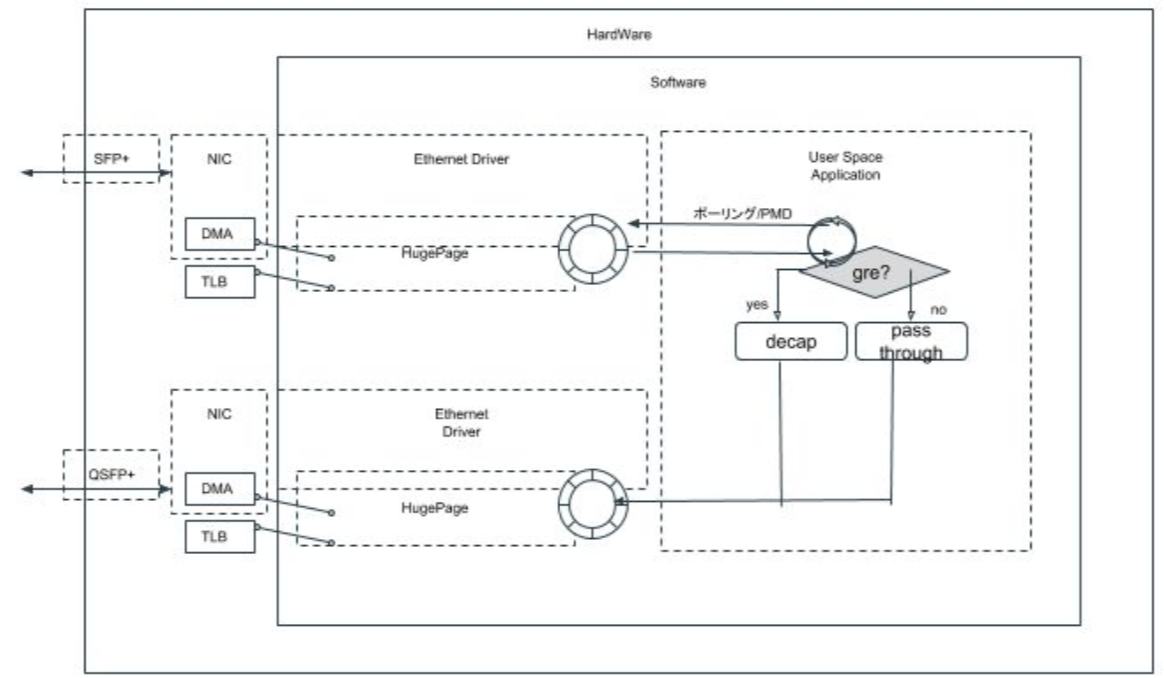

DPDKモジュール論理構成

まとめ

昨今サービスのクラウド化・集中化に、ネットワーク機器の拡張は追いついていないと言われており、そこにはSDNやNFV[4]のソリューションがあります。しかし本ケースでアプライアンスSwitch、FPGA、DPDKを比較検証し示した通り、狭義のSDNやNFV[4]では最適なソリューションとならないケースがあることを説明しました。

別々のネットワーク機器が必要だった多様なネットワーク機能の一部をFPGAや、DPDKアプリケーションによってアクセラレートすることができます、本ケースのように自社ネットワーク要件によっては、独自にFPGAで一部のネットワーク機能を代替する方が効率が良いケースもあります、このようなケースでFPGA(プログラマブル)が選択肢になるのは、広義のSDNとNFVだとも言えます。

参考資料

[1] https://www.dpdk.org/

[2] https://www.juniper.net/jp/jp/products-services/switching/qfx-series/qfx5100/

[3] https://www.altera.co.jp/solutions/acceleration-hub/overview.html

[4] https://www.nic.ad.jp/ja/newsletter/No58/0800.html