試しに Linux(HPS/ARM) からオンボード NIC として見えている Ethernet RJ-45 の口を追いかけてみる。

まず terasic のサイト の "Atlas-SoC User Manual" によると Gigabit Ethernet の端子がある。これは Micrel KSZ9031RN のコントローラを経由している。コントローラは RJ-45 端子から RGMII の信号に変換している。RGMII の信号は FPGA 側の Pin では PIN_A12 などを使って受け取っていると記載されている。ここまでは半田付けされて決まっている。

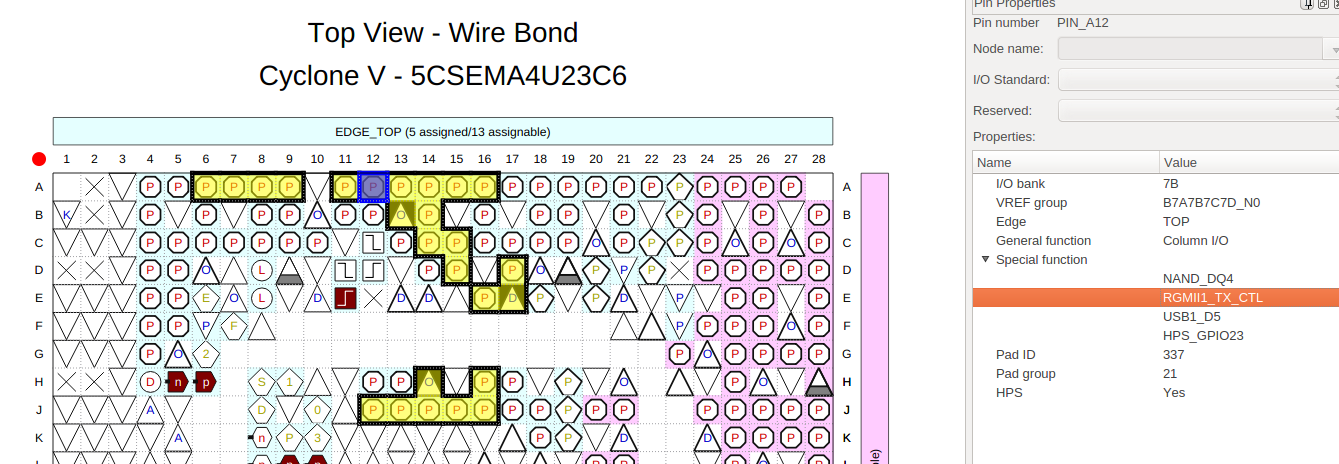

次に Intel/Altera のサイトで FPGA デバイス用ピンアウトファイルを眺める。Atlas-SoC は 5CSEMA4U23C6N を使っているので、5CSEMA4 のファイルが目的のファイルになる。先ほど見た PIN_A12 は A12 で探して、Bank Number 7B のピンだと見つかる。ちなみに A12 は A 行 12 列という物理的なピンの位置をあらわしている。このピンは NAND_DQ4, RGMII1_TX_CTL, USB1_D5, HPS_GPIO23 といった用途に使えるようになっていると書かれている。multiplexer で実行時に選べるようにしているようだ。ここで見るべきは RGMII1 を使いたいというところ。

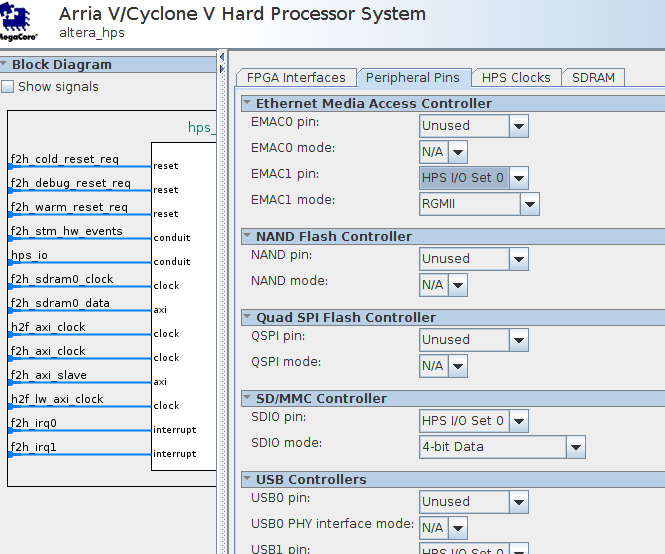

QSYS で system_soc の hps_0 の編集画面を開くと、Block Diagram の横に FPGA Interfaces, Peripheral Pins, HPS Clocks, SDRM とタブが並んでいる。Peripheral Pins が目的のタブ。EMAC1 pin が RGMII1 と対応する。GHRD Makefile 的には scripts/create_ghrd_qsys_ATLAS_SOC_GHRD.tcl で set_instance_parameter_value hps_0 {EMAC1_PinMuxing} {HPS I/O Set 0} とされている部分が対応する。こうしておくと、QSYS は PIN_A12 を EMAC1 に使うように計画する、ということのようだ。

ちなみに、ピンアウトファイルの代わりに、QSYS から soc_system のピン配置を Pin Planner で眺めてみても、A12 がどこにあるのか直感的でわかりやすい。

GHRD をコンパイルすると device tree file が生成される。DTS ファイルの中身には hps_0_gmac1 というエントリができていて、reg アドレスは 0xff702000 だそうだ。compatible には synopsys,dwmac-15.1, altr,socfpga-stmmac, snps,dwmac-3.70a, snps,dwmac と書かれている。

Linux kernel source tree によると、drivers/net/ethernet/stmicro/stmmac/dwmac-socfpga.c が altr,socfpga-stmmac を識別するようだ。つまり stmmac kernel module によって netdev が構成される。