はじめに

Digilentが公開しているArty Z7のHDMIデモが動作したので記事にしました。

その際に少しハマるポイントがあったのでまとめます。

基本的にはここに書いてある通りに進めれば大丈夫です。

以下にサイトでは分かりにくいハマりポイントのみを記載しているので基本的にはサイトを見てください。

環境

Vivado関連

- 環境はサイト通りVivado2016.4を使用します。

インストールの際Devicesのチェックが足りないとエラーになる可能性があるので注意してください。

- arty-z7-20のボードファイルをサイト通り指定のフォルダに入れたか確認してください。(ここで入手)

インストール時に何も指定しなかった人はC:\Xilinx\Vivado\2016.4\data\boards\にboard_filesのフォルダがあると思います。

プロジェクト入手

- Example ProjectsはZIPじゃなくgit cloneのコマンドで入手してください。

ZIPで入手するとプロジェクトファイルの一部が欠損するらしいです。(ここに記載あり)

GitHubでforkして自分のリポジトリに追加してからcloneすると確実です。(普通にcloneすると失敗する?)

作成

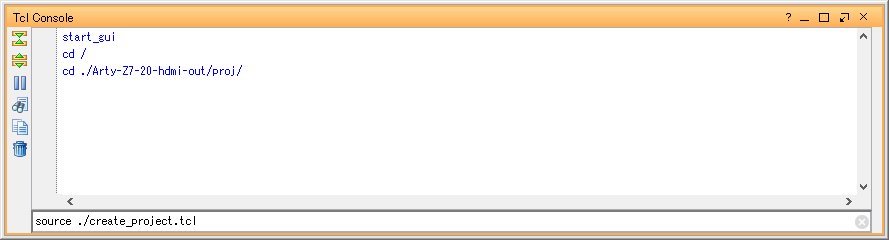

- tclを走らせる時はprojのディレクトリで実行してください。

- ジャンパPinがQSPI-JTAGになってるか確認してください。

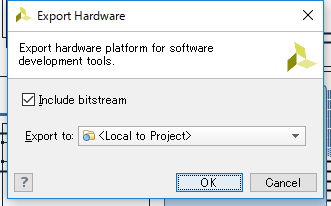

- Export Hardwareする際にチェックを入れてください。

- SDKは以下のように実行します。

- Run Asが表示されてなかったりおかしい時はClean Projectしてみてください。

動作確認

- Tera Termの設定は確認して接続してください。(ポートは環境で異なる可能性あり)

以上に気をつけてサイト通り実行すればこんな感じでうまく行くと思います。

上の画像はHDMI_Outのデモ画像ですが、Inのデモもちゃんと動作しました。

その他

Verilogベースでプロジェクト作成

create_project.tclのtarget_languageをVHDLからVerilogへ変更した状態でtclを走らせるとVerilogベースでプロジェクトが立ち上がります。

# Set project properties

set obj [get_projects $proj_name]

set_property "default_lib" "xil_defaultlib" $obj

set_property "part" $part $obj

set_property "board_part" $brd_part $obj

set_property "simulator_language" "Mixed" $obj

set_property "target_language" "Verilog" $obj

おわりに

今回、Arty Z7が秋月で買えるようになったのでユーザー増えると考えてハマらないために記事を書きました。

個人的にはFPGAの画像処理をしている研究室の学生に積極的に使ってもらいたいボードだと思っています。

理由としては

- Xilinx(Vivado)の資料が充実してる(FPGAプログラミング大全 Xilinx編やFPGAマガジンなど...)

- 2万5000円とリーズナブルな価格

- HDMIのデモプロジェクトを理解することで画像処理システム設計の勉強になる

- HDMI_INのデモをベースに画像処理システムが容易に組める(デジカメのHDMI OUT1280x720 60FPSで確認済)

-

PYNQボードと同等のことが出来る(一部異なるらしい...)

ぜひ研究室の先生に宣伝して買って貰いましょう。