はじめに

Vivado HLSの環境でSystemCをはじめる手順を記載します。

環境

- Vivado HLS 2016.2(他のバージョンでも可)

- Model Sim 10.5b(他のバージョンでも可)

Vivado HLSは当然ながらSystemCで高位合成する環境です。

Model Simは.vcd波形を出力するのに使用します。

高位合成手順

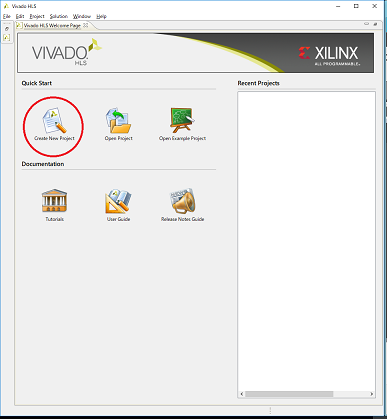

Vivado HLSを起動してCreate New Projectlを選択します。

プロジェクト名とディレクトリを入力します。

次とその次は任意なのでNEXTで飛ばします。

周期とFPGAの型番を設定します。

※FPGAの型番は自分のターゲットデバイスから決めてください(特にない人は適当にZYBOのxz7z010clg400-1を選択してください)。

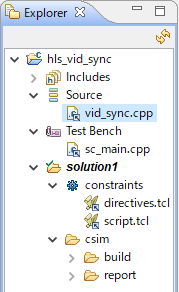

ExplorerのSourceにモジュールの.cppを追加記述し、Test Benchにはsc_mainの.cppを追加し記述します。

モジュールの**.hは.cppと同階層**にファイルを置くことで勝手に読み込まれるのでExplorerのSourceに追加しなくてもいいです。

※追記Vivado HLSのサンプルプロジェクトを見るとお作法的にはTest Benchに.hを追加するみたいです。

以下にサンプルでビデオ信号っぽい物を出力するコード記載します。

# ifndef VID_SYNC_H

# define VID_SYNC_H

# include <systemc.h>

SC_MODULE(vid_sync)

{

//Ports

sc_in <bool> clock;

sc_in <bool> reset;

sc_out <bool> vsync;

sc_out <bool> hsync;

sc_out <bool> valid;

sc_out <sc_uint<10> > data;

//Variables

//Process Declaration

void Prc1();

//Constructor

SC_CTOR(vid_sync)

{

//Process Registration

SC_CTHREAD(Prc1,clock.pos());

reset_signal_is(reset,true);

}

};

# endif

# include "vid_sync.h"

# define hf_blank 2

# define hb_blank 3

void vid_sync::Prc1()

{

//Initialization

vsync.write(0);

hsync.write(0);

valid.write(0);

data.write(0);

wait();

while(true)

{

wait();

vsync.write(1);

for(int v=0; v<480; v++)

{

hsync.write(1);

wait();

vsync.write(0);

hsync.write(0);

wait(hf_blank);

for(int h=0; h<640; h++)

{

data.write(h);

valid.write(1);

wait();

}

data.write(0);

valid.write(0);

wait(hb_blank);

}

} //end of while(true)

}

# include <systemc.h>

# include "vid_sync.h"

int sc_main (int argc , char *argv[])

{

sc_clock clock("clock",10,SC_NS); // Create a 10ns period clock signal

sc_signal <bool> reset;

sc_signal <bool> vsync;

sc_signal <bool> hsync;

sc_signal <bool> valid;

sc_signal <sc_uint<10> > data;

vid_sync U_vid_sync("U_vid_sync");

// Generate a clock and reset to drive the sim

U_vid_sync.clock(clock);

U_vid_sync.reset(reset);

U_vid_sync.vsync(vsync);

U_vid_sync.hsync(hsync);

U_vid_sync.valid(valid);

U_vid_sync.data(data);

sc_trace_file *trace_f;

trace_f = sc_create_vcd_trace_file("wave");

sc_trace( trace_f, clock, "clock");

sc_trace( trace_f, reset, "reset");

sc_trace( trace_f, vsync, "vsync");

sc_trace( trace_f, hsync, "hsync");

sc_trace( trace_f, valid, "valid");

sc_trace( trace_f, data, "data");

// start simulation

sc_start(20, SC_NS);

reset = 1;

sc_start(20, SC_NS);

reset = 0;

sc_start(20*640*480*2, SC_NS);

return 0;

};

コードが完成したらRun C Simulationを実行してください。

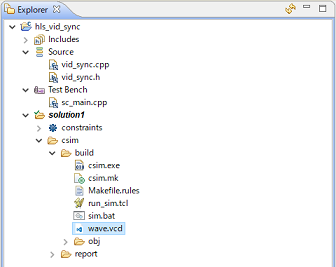

Explorer->ProjectName->solution1->csim->buildの中に**.vcd**ファイルが出力されていると思います。

SIM手順

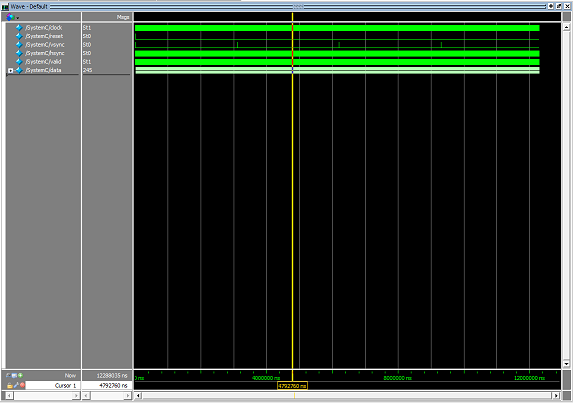

Model Simで波形を見る場合**.vcdを.wlf**に変換するコマンドがあるので変換してから波形を見ます。

参考URL : https://www.altera.co.jp/support/support-resources/knowledge-base/solutions/rd07062010_692.html

ModelSimのコマンドラインから.vcdのファイルがあるディレクトリに移動します。

移動したら以下のコマンドを実行します。

vcd2wlf wave.vcd wave.wlf

すると同ディレクトリにwave.wlfが作成されると思います。

あとはModelSimのOpenFileでwave.wlfを読み込めば波形が確認出来ます。

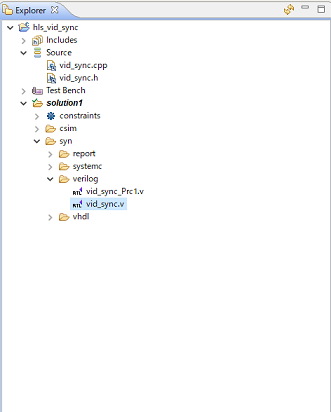

合成データ生成手順

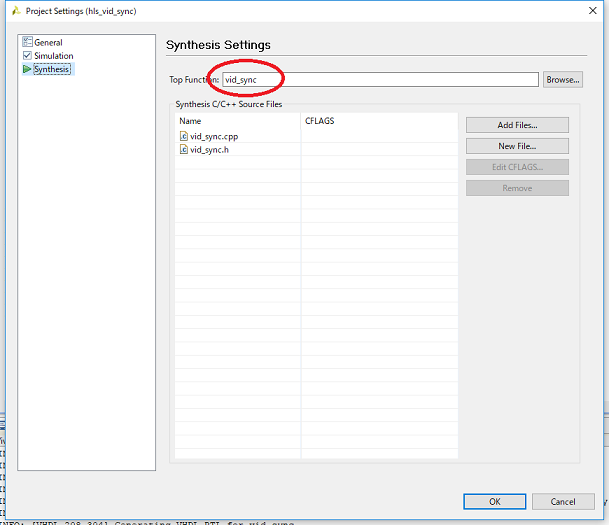

Simで動作確認が出来たら、Projects Settings->SynthesisでTop Function(上のサンプルの場合vid_sync)を設定します。

あとはC Synthesisを実行するとExplorer->ProjectName->solution1->syn以下にRTLが出力されています。

おわりに

Qiitaを見る限りSystemCは流行ってなさそうですが(投稿時のタグ数2)これからたくさん情報が載ればいいなぁと思っています。SystemCの超入門としてSystemCプログラミング基礎講座という本が分かりやすかったです(2006年のものなので古い)。SystemCの公式ドキュメントはaccelleraからDL出来ると思います。

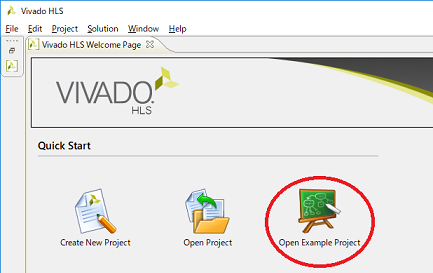

あとVivado HLSのスタートページにあるOpen Example Projectのコードを参考にするのも勉強になると思います。