はじめに

SSDのようなストレージに限らず、コンピューティングシステムにはSilent Data Corruption (SDC)と呼ばれるエラーが存在します(Silent Data Error (SDE)と呼ばれることもあります)。

名称に「サイレント(Silent)」が含まれる理由は、ユーザやシステムが気づかないうちにそれらのエラーが発生し、それらが時には悪化や伝播を起こし、エラーに気づいた時には手遅れで修復不能な状態、ということが起こり得るためです。

このSDCのうち、中性子線によるSRAMなどのソフトエラーはSingle Event Upset (SEU)と呼ばれ1990年台から研究されています[1][2]。その後半導体の微細化により単ビットではなく複数ビットまとめてエラーを起こすことも明らかにされました[3][4]。同様の現象がNANDフラッシュメモリ(当時は2D)で起こり得ることも示されています[5]。

そのようなハードウェア要因のソフトエラーに加え、アルゴリズムのソフトウェア実装方法に起因して起こり得る情報の喪失もSDCのひとつと考えられています[6]。

そこで、今回から2回の記事で、NANDフラッシュメモリをメディアとするSSD(以降単にSSDと記載)にまつわるSDC特にハードウェア起因のソフトエラーとその対策を説明します。

SSDの構成要素は大きくNANDフラッシュメモリとそれ以外に分類できますので、今回の記事ではNANDフラッシュメモリに起きる事象を説明し、次回の記事ではSSDを構成するNANDフラッシュメモリ以外の要素で起きる事象を説明します。

まとめ

- SSDのソフトエラー発生個所は、NANDフラッシュメモリとそれ以外に分類できる

- NANDフラッシュメモリで発生するソフトエラーのうち、データリテンションはパトロールで、リードディスターブはRead回数の監視で対応する

- その他のソフトエラーはNANDフラッシュメモリ向け誤り訂正機能でまとめて対処する

NANDフラッシュメモリのどこでソフトエラーが発生するか

NANDフラッシュメモリは、メモリセルとその周辺回路から構成されます。

しかし、実際にはチップの大部分をメモリセルが占めるため、中性子線が原因のものを含めて、ソフトエラーが発生する箇所は確率的にほぼメモリセルであると言えます。

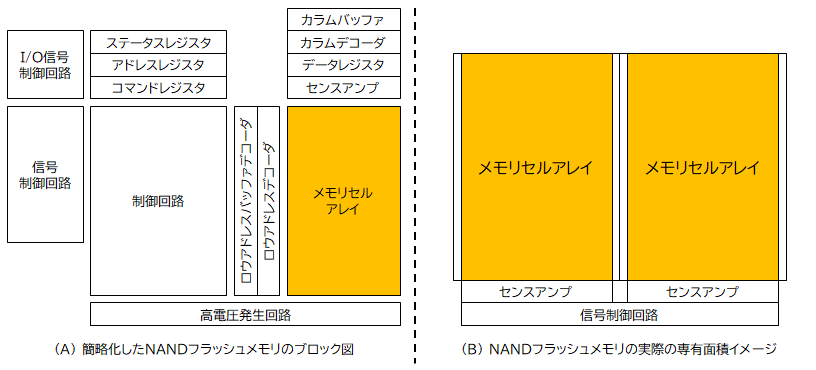

NANDフラッシュメモリチップのブロック図と実際のチップ写真イメージを比較すると図1のようになります。

図1:NANDフラッシュメモリチップのブロック図(A)と実際のチップ写真イメージ(B)

メモリセルアレイはブロック図上ではいち機能ブロックとして描かれます。しかし、NANDフラッシュメモリメーカーが自社Webサイトで公開しているチップ写真や各種学会で発表したチップ写真を見ると、実際にはメモリセルアレイがチップのほとんどを占めていることがわかります。

最近の3D NANDフラッシュメモリでは周辺回路をメモリセルアレイの上や下に配置する構造を採用したものもあります。その場合でもメモリセルアレイの占める体積比率が圧倒的に高いことは変わりません。

このことから、NANDフラッシュメモリチップで発生するソフトエラーとしてまず考慮すべきものはメモリセルで発生するもの、となります。

データリテンション

<リテンションによるエラーにはパトロールで対応>

データリテンションによるエラーは、データを書き込んでからの時間経過に伴い発生(増加)するエラーです。周辺温度などの環境にも影響を受けます。

リテンションによるエラーを起こしたメモリセルは再度消去を行うことで通常通りデータの書き込みと保持が可能です。つまりリテンションエラーはメモリセルの不可逆的なエラーではありません(ただし疲弊の影響は不可逆的)。このためこのエラーはソフトエラーに分類されます。

リテンション起因のエラーに限らず、NANDフラッシュメモリへ記録したデータにエラーが起きているかどうかは、SSDコントローラが行う誤り訂正時に検出可能です。また、存在するエラー数も同じく訂正時にわかることが多いです(「何ビット訂正した」など)。

つまり、ホストがあるデータをReadすればSSDコントローラはそのデータをNANDフラッシュメモリから読み出しますので、その際に行う誤り訂正の結果からNANDフラッシュメモリに記録されているそのデータに発生しているエラーの状態(エラー数)がわかります。

この際もしエラー数が多ければ、訂正して得た当該データを別のメモリセルに書き込むことでリテンションにより生じたエラーをリセットします。

ただこの方法では、ホストから読み出されない限りNANDフラッシュメモリへ記録したデータに蓄積したエラーの状態がわからない、ということになります。

ソフトエラーの怖い点は「いつの間にかエラーが起きていて(増えていて)いつの間にか修復不能になる」ことですので、これは避けなければなりません。

そこでSSDコントローラは、定期的にNANDフラッシュメモリに記録したデータを読み出して蓄積したエラーの状態を確認します。これがパトロールです。 パトロールの結果検出したエラー数が多いデータは別のメモリセルに書き込んで蓄積したエラーをリセットします。

パトロールの間隔は、NANDフラッシュメモリの種類(信頼性仕様)、周辺温度、データを書き込んでから経過した時間、消去回数、などのパラメータから決定します。

エンタープライズ向けSSDでは「1日でSSDに記録されている全データをパトロールする」という仕様の製品もあるくらい、パトロールは重要な機能です。

リードディスターブ

<リードディスターブによるエラーはRead回数をモニタして対応>

リードディスターブによるエラーは、自メモリセルの周辺メモリセルがReadされるたび自メモリセルにエラーが発生しやすくなる現象です。周辺メモリセルのReadされる回数が多くなればなるほど自メモリセルにエラーが発生する確率も高くなります。

リードディスターブによりエラーが発生したメモリセルも、再度消去を行うことで通常通りデータの書き込みと保持が可能です。つまりリードディスターブによるエラーはメモリセルの不可逆的なエラーではありません(ただし疲弊の影響は不可逆的)。このためこのエラーもソフトエラーに分類されます。

リードディスターブによるメモリセルへの影響はRead回数に依存しますので、SSDコントローラは特定のメモリセルの周辺にReadが集中していないかどうかを監視し、必要に応じて当該メモリセルからデータを読み出して誤り訂正を行い発生しているエラー数を確認します。この際もしエラー数が多ければ、訂正して得た当該データを別のメモリセルに書き込むことでリードディスターブにより生じたエラーをリセットします。

リードディスターブで受ける(与える)影響はNANDフラッシュメモリの種類(信頼性仕様)などに依存します。このため、「周辺メモリセルが何回Readされたらチェックするか」などの基準は予めNANDフラッシュメモリを評価した結果に基づいて決めます。

予め評価した際に「あるRead回数付近からエラー数が急激に増加する」などの特性が判明した場合は、エラー数のチェックをせずにRead回数のみを判断基準として強制的にデータをコピーするように実装することもあります。

中性子線などによるソフトエラー

<その他のソフトエラーは誤り訂正符号でまとめて対応>

NANDフラッシュメモリに記録したデータには、データリテンションとリードディスターブ以外にも冒頭で説明した中性子線によるエラーが起こり得ます。

それらのソフトエラーに対しては、NANDフラッシュメモリ用に設計および実装された誤り訂正方式でまとめて対応してしまう、という方針が一般的です。

NANDフラッシュメモリ向けにSSDコントローラが実装する誤り訂正符号(ECC)の能力は、TLC NANDフラッシュメモリ向けであれば、例えば2 KB(16,384ビット)あたり120ビットまで訂正可能[7]、もう少し能力の高いものでは1 KBあたり120ビットまで訂正可能[8]、などです。また最近のSSDは、SSD内部でRAID (Redundant Array of Inexpensive Disks)などを構成して消失訂正能力を持たせるものも多いです。

それらのSSDでは、NANDフラッシュメモリのメモリセルの特性によるエラーに加え中性子線によるエラーが発生しても上記誤り訂正能力で対処できる範囲内であるという判断のもと、後者のエラーに個別に対応する機能を持たせていないことになります。

おわりに

この記事では、SSDにおけるSDC特にハードウェア起因のソフトエラーについて、NANDフラッシュメモリに起きる事象とその対策を説明しました。

NANDフラッシュメモリで発生するソフトエラーは、その構造からメモリセルで発生するものがほとんどと考えられ、例えばデータリテンションやリードディスターブによるエラーなどが挙げられます。そしてそれらのエラーに対して手遅れにならないようにSSDコントローラが対策を施しています。

次回の記事ではSSDを構成するNANDフラッシュメモリ以外の要素で起きる事象とその対策を説明します。

References

[1] A. Taber and E. Normand, "Single event upset in avionics," in IEEE Transactions on Nuclear Science, vol.40, no.2, pp.120-126, April, 1993

[2] F. Wrobel, et al., "Contribution of SiO2 in neutron-induced SEU in SRAMs," in IEEE Transactions on Nuclear Science, vol.50, no.6, pp.2055-2059, December, 2003

[3] N. Seifert, et al., "Radiation-Induced Soft Error Rates of Advanced CMOS Bulk Devices," in Proceedings of IEEE International Reliability Physics Symposium, pp.217-225, March, 2006

[4] David F. Heidel, et al., "Single-Event Upsets and Multiple-Bit Upsets on a 45 nm SOI SRAM," in IEEE Transactions on Nuclear Science, vol.56, no.6, pp.3499-3504, December, 2009

[5] G. Cellere, et al., "Neutron-induced soft errors in advanced flash memories," in Proceedings of IEEE International Electron Devices Meeting (IEDM), December, 2008

[6] Harish Dattatraya Dixit, "Mitigating the effects of silent data corruption at scale," February 23, 2021

[7] "120bits/2kb ECCとEnd-to-Endデータ保護を搭載したNVMe SSD、Apacer「AS2280P4」"、2019年4月8日(2024年5月22日閲覧)

[8] Jeff Yang, “The Efficient LDPC DSP System for SSD,” Flash Memory Summit 2013, Santa Clara, CA, August, 2013

ライセンス表記

この記事はクリエイティブ・コモンズ 表示 - 継承 4.0 国際 ライセンスの下に提供されています。