はじめに

1500円 ZYNQ 基板(EBAZ4205)で、

FPGAプログラミング大全Xilinx編(第2版)の課題6-1

「MicroBlaze システムのハードウェア構築」

と、課題6-2

「MicroBlaze のプログラムを実行」

を実習したいと思います。

IPインテグレータによるシステム構築

いきなりですが、Vivado の IP インテグレータでシステムを構築します。

前記事までで Vivado の使い方にも慣れましたので、サクサク進めます。

p.250 ◎IP インテグレータの起動(参考:図5-9)

p.250 ◎MicroBlaze の配置を設定(図6-4)

大全の手順通り進めます。

p.252 ◎Clocking Wizard の設定(図6-5)

概ね大全の手順通りでよいですが、Digilent 社の基板とは PL に供給されているクロックの周波数が異なりますので、そこだけアレンジします。

clk_in1 の周波数の違いは、下記の通りです。

(1500円ZYNQ基板でFPGAプログラミング大全Xilinx編(第2版)の実習 その1:準備で N18 ピンにジャンパ接続したクロック)

clk_in1

Digilent : 125 MHz のシングルエンドクロック

EBAZ4205 : 33.333 MHz のシングルエンドクロック

出力クロックも、微妙に変わります。

(MMCM/PLL の生成倍率による制限)

p.253 ◎入力ポートの接続とリセットの配線(図6-6、参考:図5-11(f))

p.254 ◎GPIO を接続(参考:図5-11)

p.254 ◎ポート名の修正(図6-7、参考:図5-13)

p.255 ◎PS を追加(図6-8~図6-10、参考:図5-10)

大全の通り進めます。

p.256 ◎ダイアグラムのチェック(参考:図5-14)

p.256 ◎上位階層の作成(参考:図5-16)

大全の手順通りです。

p.256 ◎制約ファイルの読み込みとコンパイル

制約ファイルは、EBAZ4205 用を使います。

## EBAZ4205 constraints file

## chapter: 2

## project: ebaz4205_taizen

# Clock signal

set_property -dict { PACKAGE_PIN N18 IOSTANDARD LVCMOS33 } [get_ports { CLK }];

create_clock -add -name sys_clk_pin -period 30.00 -waveform {0 4} [get_ports { CLK }];

# Reset

set_property -dict { PACKAGE_PIN V13 IOSTANDARD LVCMOS33 } [get_ports { RST }]; # BTN[1]

# RGB LEDs

set_property -dict { PACKAGE_PIN W14 IOSTANDARD LVCMOS33 } [get_ports { LED_RGB[2] }]; # Red

set_property -dict { PACKAGE_PIN W13 IOSTANDARD LVCMOS33 } [get_ports { LED_RGB[1] }]; # Green

set_property -dict { PACKAGE_PIN U12 IOSTANDARD LVCMOS33 } [get_ports { LED_RGB[0] }]; # Blue

# Buttons

set_property -dict { PACKAGE_PIN V15 IOSTANDARD LVCMOS33 } [get_ports { BTN[0] }];

# 25MHz Out

set_property -dict { PACKAGE_PIN U18 IOSTANDARD LVCMOS33 } [get_ports { FCLK_CLK3 }];

# EMIO PHY

set_property IOSTANDARD LVCMOS33 [get_ports ENET0_GMII_RX_CLK_0]

set_property IOSTANDARD LVCMOS33 [get_ports ENET0_GMII_TX_CLK_0]

set_property PACKAGE_PIN U14 [get_ports ENET0_GMII_RX_CLK_0]

set_property PACKAGE_PIN U15 [get_ports ENET0_GMII_TX_CLK_0]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_RXD_0[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_RXD_0[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_RXD_0[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_RXD_0[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_TX_EN_0[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_TXD_0[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_TXD_0[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_TXD_0[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ENET0_GMII_TXD_0[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports ENET0_GMII_RX_DV_0]

set_property IOSTANDARD LVCMOS33 [get_ports MDIO_ETHERNET_0_0_mdc]

set_property IOSTANDARD LVCMOS33 [get_ports MDIO_ETHERNET_0_0_mdio_io]

set_property PACKAGE_PIN Y17 [get_ports {ENET0_GMII_RXD_0[3]}]

set_property PACKAGE_PIN V17 [get_ports {ENET0_GMII_RXD_0[2]}]

set_property PACKAGE_PIN V16 [get_ports {ENET0_GMII_RXD_0[1]}]

set_property PACKAGE_PIN Y16 [get_ports {ENET0_GMII_RXD_0[0]}]

set_property PACKAGE_PIN W19 [get_ports {ENET0_GMII_TX_EN_0[0]}]

set_property PACKAGE_PIN W18 [get_ports {ENET0_GMII_TXD_0[0]}]

set_property PACKAGE_PIN Y18 [get_ports {ENET0_GMII_TXD_0[1]}]

set_property PACKAGE_PIN V18 [get_ports {ENET0_GMII_TXD_0[2]}]

set_property PACKAGE_PIN Y19 [get_ports {ENET0_GMII_TXD_0[3]}]

set_property PACKAGE_PIN W15 [get_ports MDIO_ETHERNET_0_0_mdc]

set_property PACKAGE_PIN Y14 [get_ports MDIO_ETHERNET_0_0_mdio_io]

set_property PACKAGE_PIN W16 [get_ports ENET0_GMII_RX_DV_0]

p.256 ◎プラットフォームファイルの Export (参考:図5-17)

大全の通り進めます。

MicroBlaze のプログラムを実行 (Hello World)

こちらも慣れましたので、サクサクと進めます。

p.257 ◎Vitis の起動とワークスペースの指定(参考:図5-18、図5-19)

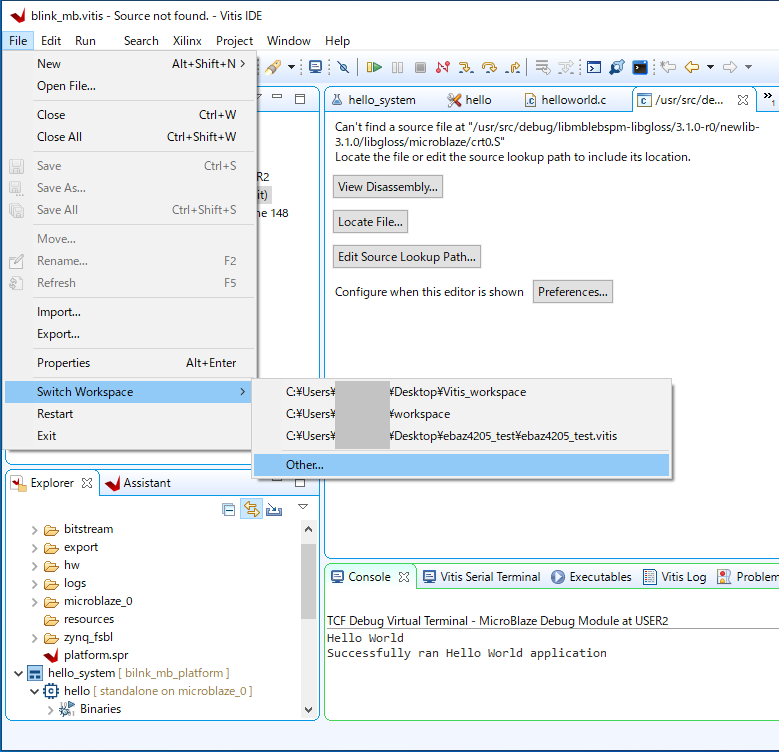

ワークスペースですが、2回目以降に Vitis を起動すると前に使ったワークスペースが開いた状態で起動されます。

(EBAZ4205_taizen など)

ワークスペースを変更して、新しい気持ちで始めたいときは、メニューバーから

File - Switch Workspace - Other

として、ワークスペースのフォルダを再指定します。

C:\Users(ユーザー名)\Desktop\blink_mb\blink_mb.vitis

として、Vivado からエクスポートしたフォルダを指定すると、わかりやすいです。

p.257 ◎プラットフォームプロジェクトの作成(参考:図5-20)

p.257 ◎アプリケーションプロジェクトとシステムプロジェクトの作成(参考:図5-21)

p.257 ◎各プロジェクトのビルド(参考:図5-23)

p.257 ◎デバッグ設定の作成とプログラムのダウンロード(参考:図5-24、図5-31)

p.257 ◎プログラムの実行(図6-11、参考:図5-27)

すべて大全の手順通りで進めます。

実行した結果、MicroBlaze から Hello World できました。

ちょっとアレンジ

Hello World のメッセージの最後に、CR+LF を追加しておきます。

print("Successfully ran Hello World application\n\r");

ビルドしたら、こんどは Debug ではなく、RUN で実行します。

実行した状態で、EBAZ4205 基板で PL のリセットに割り当てたボタン(U67 に搭載したボタン)を押してみます。

MicroBlaze が再起動するので、プログラムが再実行されます。

リセットボタンを押す度に、Hello World できます。

これで、ZYNQ の PL 部に構築されたマイコン(MicroBlaze)を、好きなように使うことができます。

まとめ

FPGAプログラミング大全Xilinx編(第2版)の課題6-1

「MicroBlaze システムのハードウェア構築」

と、課題6-2

「MicroBlaze のプログラムを実行」

を EBAZ4205 で実習することができました。