はじめに

前の投稿で、EBAZ4205 基板を改造して、Cora Z7 相当で動かせるようになりました。

早速、FPGAプログラミング大全Xilinx編(第2版)の

最初の課題 "Lチカ" をやってみます。

関連ファイルのダウンロード

ソースファイル一式を、FPGAプログラミング大全Xilinx編(第2版) サポートサイトから取ってきます。

https://www.shuwasystem.co.jp/support/7980html/6326.html

XilinxFPGA_SE.zip を解凍して、\Cora_Z7-10\dai2-3sho\blink フォルダをデスクトップに展開します。

制約ファイル(blink.xdc)の変更

Cora Z7-10 と EBAZ4205 では、FPGA のピンと、LED やスイッチの接続が違っているため、制約ファイル(blink.xdc)を変更します。

既存のポート名に対応する FPGA のピン番号を修正します。

変更点は、下記の通りです。

クロック入力

Cora Z7-10:H16 (125 MHz) → EBAZ4205:N18 (33.333 MHz)

Cora Z7-10:クロック周期 8ns → EBAZ4205:クロック周期 30nsスイッチ入力 (RESET)

Cora Z7-10:D19 (BTN1) → EBAZ4205:V13 (U67 に付けたスイッチ - 基板端側)LED出力

Cora Z7-10:N15 (赤) → EBAZ4205:W14 (赤)

Cora Z7-10:G17 (緑) → EBAZ4205:W13 (緑)

Cora Z7-10:L15 (青) → EBAZ4205:U12 (NCピン - 出力しても何も起きない)

## EBAZ4205 constraints file

## chapter: 2

## project: blink

# Clock signal

set_property PACKAGE_PIN N18 [get_ports { CLK }]

set_property IOSTANDARD LVCMOS33 [get_ports { CLK }]

create_clock -add -name sys_clk_pin -period 30.00 \

-waveform {0 4} [get_ports { CLK }]

# Reset

set_property -dict { PACKAGE_PIN V13 IOSTANDARD LVCMOS33 } \

[get_ports { RST }]; # BTN[3]

# RGB LED

set_property -dict { PACKAGE_PIN W14 IOSTANDARD LVCMOS33 } \

[get_ports { LED_RGB[2] }]; # Red

set_property -dict { PACKAGE_PIN W13 IOSTANDARD LVCMOS33 } \

[get_ports { LED_RGB[1] }]; # Green

set_property -dict { PACKAGE_PIN U12 IOSTANDARD LVCMOS33 } \

[get_ports { LED_RGB[0] }]; # Blue

回路ソース(blink.v)の変更

Cora Z7-10 と EBAZ4205 の搭載部品の違いから、下記 3 点を変更します。

・クロック周波数が 125 MHz → 33.333 MHz に遅くなるため、カウンタの bit 数を 26bit から 24bit へ減らす

⇒ カウンタ幅を cnt26[25:0] から cnt24[23:0] へ減少

⇒ ALL1 検出を 26'h3ffffff から 24'hffffff へ変更。

・LED が RGB ではなく RG しかないため、点滅パターンを変更 (LEDデコーダ)

・LED への出力値と点灯の論理が逆なので、出力値に ~ を追加して反転で表記 (LEDデコーダ)

/* Copyright(C) 2020 Cobac.Net All Rights Reserved. */

/* chapter: 第2章 */

/* project: blink */

/* outline: LED点滅回路 */

/* modified by KAN573 */

module blink (

input CLK,

input RST,

output reg [2:0] LED_RGB

);

/* システムクロックを分周 */

reg [23:0] cnt24;

always @( posedge CLK ) begin

if ( RST )

cnt24 <= 24'h0;

else

cnt24 <= cnt24 + 1'h1;

end

wire ledcnten = (cnt24==24'hffffff);

/* LED用5進カウンタ */

reg [2:0] cnt3;

always @( posedge CLK ) begin

if ( RST )

cnt3 <= 3'h0;

else if ( ledcnten )

if ( cnt3==3'd5)

cnt3 <=3'h0;

else

cnt3 <= cnt3 + 3'h1;

end

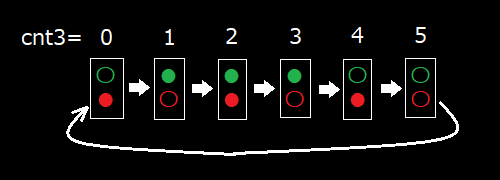

/* LEDデコーダ */

always @* begin

case ( cnt3 )

3'd0: LED_RGB = ~3'b100;

3'd1: LED_RGB = ~3'b010;

3'd2: LED_RGB = ~3'b110;

3'd3: LED_RGB = ~3'b010;

3'd4: LED_RGB = ~3'b100;

3'd5: LED_RGB = ~3'b000;

default:LED_RGB = ~3'b000;

endcase

end

endmodule

コンパイル

オリジナルと同じですので、大全の手順通りでよいです。

動作確認

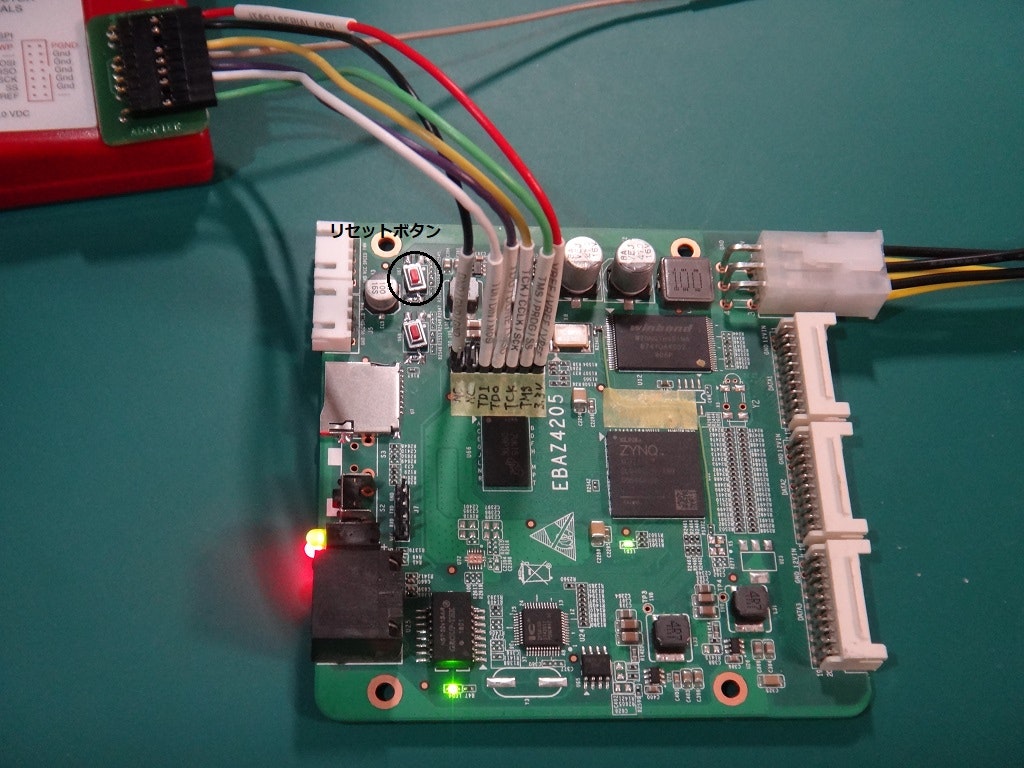

FPGA へのダウンロードが完了すると、cnt3 のシーケンスに従って、LAN コネクタ横の LED が点灯します。

LED の発光パターンは下記を繰り返します。

U67 に付けたスイッチがリセットボタンです。

押すと cnt3 がクリアされて、cnt3=0 から再スタートします。

まとめ

2-1 LED 点滅回路の記述と動作確認について、EBAZ4205 で学習することができました。