US の NSF(National Science Foundation)が資金を提供した半導体設計に関する、米国国内の課題と対策の提案書の Google 翻訳を公開します。「てにをは」やワーディングの揺れはお許しください。

エグゼクティブサマリー

ムーアの法則に従った進歩のペースが低下し続ける中、米国が技術革新を維持するために集積回路(IC、または「チップ」)の教育と研究を支援することが重要です。 さらに、米国の経済的独立、安全保障、将来の国際的地位は、国内の IC 設計能力に依存しています。 IC 設計能力を向上させるには、異種テクノロジを備えた新しいデバイス、改良された設計ソフトウェア ツールチェーンと方法論、異種システムを統合するテクノロジが必要になります。 そのためには、新たな複雑さに対処するために設計をどのように教えるか、またハードウェア システムのキャリア パスへの学生の関心をどのように高めるか、両方を再考する必要があります。 このワークショップの主な推奨事項は、アクセシビリティが重要な問題であるということです。 この目的を達成するために、国立チップ設計センター (NCDC) を設立し、学者と産業界が提携して研究と教育を進め、将来の労働力を訓練する必要があります。 これは、R1 大学に限定されるものではなく、最も広範な効果をもたらすために、R2、コミュニティ カレッジ、少数派教育機関 (MSI)、幼稚園から高校までの教育機関も含めるべきです。 NCDC は、オープン設計ツール、ツール フロー、設計キット、設計コンポーネント、および教育資料へのアクセス、開発、および保守をサポートする必要があります。 アクセシビリティを最大限に高めるために、可能な限りオープンソースのオプションを強調する必要があります。 NCDC はまた、研究と教育の両方の目的で、チップの製造、パッケージング、テストへのアクセスとサポートを提供する必要があります。

イントロダクション

米国の大学におけるチップ設計は、ミードとコンウェイ革命 (コンウェイ) のおかげで開花しました。 1978 年から 1979 年にかけて、カーバー ミードとリン コンウェイは独創的な教科書『VLSI システム入門』を執筆しました [1]。 この本は、デジタル チップ設計を複雑な物理学の問題からはるかに簡単なコンピュータ サイエンスの問題に変換する抽象化を提供し、学界でチップ設計を普及させました。

コンウェイは 1978 年に MIT で VLSI コースを教え、マルチプロジェクト チップの概念につながり、ダニー コーエンは VLSI プロトタイピングのために USC に金属酸化物半導体実装サービス (MOSIS) を設立しました。 MOSISは、当初はNSFの支援を受けて、その後商業事業からの利益を利用して大学のVLSIクラス用に無償チップを製造したが、2020年にこのサービスの提供を中止した。DARPAも1980年にVLSI研究プロジェクトを開始し、ミード&コンウェイの研究を広めて開発を奨励した。 チップと電子設計自動化 (EDA) ツールの開発も率先しました。

チップ設計は、大学と産業界の協力によってさらに促進されました。 初期の設計は MOSIS レイアウト ツールを使用して行われましたが、より高度な設計には合成ツールと配置配線ツールが必要です。 Cadence、Synopsys、Mentor Graphics などの EDA ベンダーは、割引ツールを提供する大学プログラムを設立しました。 ノースカロライナ州立大学は、最新の予測 (つまり、非製造可能) テクノロジー ファイルを使用して NCSU プロセス デザイン キット (PDK) を開発しました [2]。

1990 年代を通じて、大学は活気に満ちた一連の教科書を使用して、大学院または上級学部レベルで大規模な VLSI クラスを教えていました。 MOSIS を通じてチップを製造し、それをテストすることは、何千人もの工学専攻者にとって通過儀礼となりました。 Brunvand は、すぐに利用できるプロセスに業界標準のツールを使用してチップ設計用の EDA ツールとモデルをインストールして構成するためのクックブックを提供しました [3]。 Flow はすべての大学生がアクセスできるほど成熟しました。

近年、VLSI 教育は衰退に直面しており、VLSI クラスはニッチなトピックとしてのみ提供されるようになりました。 NSFが最近開催したパネルディスカッションの教員らによると、ほとんどの大学で入学者数が減少しており、一部の学校ではこれらのコースの過小評価された学生の割合がゼロに近いという。 教科書の売り上げは急激に減少し、主にインドと中国に移った。 MOSIS は、クラスのプロジェクトに長年使用されてきた古い 0.6 ミクロン プロセスのサポートを中止し、クラスへの資金提供を完全に中止しました。 割引価格の VLSI EDA ツールのコストは他の大学ソフトウェアよりも大幅に高く、登録者数が減少すると学生 1 人あたりのコストも増加します。 多くの大学が、これらの学術ライセンスの購入を完全に中止することを提案しています。 さらに、これらのツールとそのコンピューティング インフラストラクチャを維持するコストには、IT スタッフの配置と専門知識、さらにはライセンスとインストールのための専用のコンピュータ システムが必要です。 ライセンスにより、学生は従来のコンピューティング研究室以外のツール、特にほとんどの学術プログラムの事実上の標準であるパーソナル コンピューターでツールを使用することができなくなります。

時代遅れのプロセスを使用した結果は一般に公開できず、高度なプロセスの設計ファイル (デバイス モデル、設計ルール、ライブラリ) は独自のものであり、特別な業界とのつながりを持つ教員のみが利用できるため、学術界における VLSI 研究は非常に困難になっています。 多くの場合、大学は、知的財産の所有権に多くの制限があるため、一部の産業界パートナーが要求する機密保持契約 (NDA) に署名することに消極的です。

輸出管理、責任、ロックアウト、その他の課題。 高度なプロセスでの製造コストも非常に高いため、多くの場合、スポンサー企業が提供する既存のシャトルバスを利用する必要がありますが、これも特別なコネを持つ教員のみが利用できます。 全体として、チップ設計でのキャリアを準備している米国の大学を卒業する学生ははるかに少ないです。

米国は現在、半導体産業において経済と国家安全保障の両方の脅威に直面している。 現在、世界的な半導体不足により、Apple は iPhone 12 の発売を 2 か月延期することを余儀なくされ (「Apple、複数のサイズの新しい 5G iPhone 12 製品ラインを発表」)、自動車業界に予想される 600 億ドルの収益が発生しました [4]。 2014 年、Broadcom は携帯電話アプリケーション プロセッサ市場で Samsung や MediaTek との海外競争に対抗できないことに気づき、部門全体を閉鎖し、シンガポールの企業 Avago に買収されるほど弱体化しました [5]。

供給が限られているため、偽造電子機器の数十億ドル規模の闇市場が存在し、米国国防総省が購入する予備電子部品の推定 15% が偽造品であり、信頼性と安全性の両方を脅かしています [6]。 2020年、連邦通信委員会は、中国の通信会社ファーウェイとZTEを、5Gネットワーキング機器を通じたスパイ活動のリスクを理由に国家安全保障上の脅威に指定した[7]。 中国国家集積回路計画は、2030 年までに最先端の国内集積回路製造能力を開発することを目指しており、同国は 2014 年から 2020 年の間に同産業に 1,500 億ドルを投資しました [8]。 2014年、IBMは自社のチップ事業をGlobalFoundriesに売却し、国内のチップ製造源を終了した。

米国の半導体産業の活性化を目指して、複数の勢力が結集している。 2021 年 3 月、Intel CEO のパット ゲルシンガーは、アリゾナ州に 7nm 製造向けの 2 つの新しい IC 製造工場を建設し、ファウンドリ サービスを外部顧客に販売するための 200 億ドルの投資を発表しました [9]。 これにより、米国の製造能力が大幅に拡大します。 2020 年 3 月のバイデン大統領の「米国雇用計画」では、国内のチップ製造に 500 億ドル以上の投資が求められています [10]。 しかし、重要な課題は、これらの工場で製造のための設計を作成するための労働力をどのように教育し、確立するか?です。

オープンソースのハードウェア設計と EDA ツールが、クローズドソースで悪名高い IC 設計にどのような影響を与えることができるかについて、大きな関心が寄せられています。 DARPA は、完全にオープンソースのツールチェーンの開発に広く資金を提供しており [11]、オープンソースのフィールド プログラマブル ゲート アレイ (FPGA) ツール フローでも、複数の FPGA アーキテクチャ用の非常に成熟したツールチェーンが見られます [12]。 DARPA はまた、サプライチェーンを確保し、集積回路の研究開発を促進するために、Electronic Resurgence Initiative に資金を提供しています [13]。 Free and Open Source Silicon Foundation (FOSSi) は、オープンソース EDA ツールとライブラリを推進しています [14]。 CHIPS Alliance などの業界コンソーシアムは、そのようなオープンソースの機会を中心に結集しています [15]。 Google は最近、古い SkyWater 130nm テクノロジーのオープンソース プロジェクトに対して SkyWater マルチプロジェクト ウェーハ シャトルのスポンサーを開始し、最近、SkyWater の商用 90nm CMOS プロセス テクノロジーである SKY90-FD 用のオープンソース プロセス設計キット (PDK) を開発する計画を発表しました。 16] および GlobalFoundries 180nm テクノロジー [17]。 オープンソース分野における記念碑的な成功の 1 つは、多数の企業や学術機関による RISC-V の採用です [18]。 かつては独自の ISA、ファームウェア、コンパイラで満たされていたマイクロプロセッサ エコシステム全体が、現在では自由に利用できるようになり、パフォーマンスにおいて競争力を発揮できるようになりました。

ミード・コンウェイ革命は、IC 設計をアナログ設計者からデジタル設計者に移行することで始まりましたが、オープンソースの動きにより、次世代の「IC 設計者」がデジタル設計者からソフトウェア エンジニアに移行できる可能性があります。 ハードウェア設計は多くの恩恵を受けています

高位合成、中間表現、プログラミング言語、形式的検証などのソフトウェア設計の効率性と生産性のパラダイム。たとえば、最近では、例えば Chisel [19] や XLS [20] などの新しい高位設計言語が変化し始めています。 ハードウェア設計を抽象化し、最適化と統合のための新たな機会を提供する方法 [19]。 オープンソース IC 設計エコシステムへのアクセシビリティの向上により、誰が IC 設計者になれるかという概念を拡張することで、イノベーションの機会が開かれるだけでなく、多様性を高めるチャンスも開かれます。

ムーアの法則が薄れるにつれ、大学が IC の教育と研究へのアプローチを再考することがさらに重要になっています。 IC 設計の改善には、異種テクノロジーを備えた新しいデバイス、EDA ツールチェーンと方法論の改善、異種システムの統合によって実現する必要があります。 これらすべてにおいて、複雑さに対処するための設計方法と、ハードウェア システムに対する学生の関心をどのように活性化するかという両方を再考する必要があります。 学術界と産業界は、将来の労働力を訓練する際に、今すぐこの変化に対処する必要があります。

過去 2 年間、同様の問題に関する関連ワークショップが開催されました [21]、[22]。 特に、これらは主に製造と研究に焦点を当てていました。 これも私たちのワークショップの一部でしたが、私たちは幼稚園から高校まで、学部生、大学院生(修士号と博士号)といったあらゆるレベルの教育と研究を含む人材育成についてより広範に検討しました。

このワークショップの一環として、私たちは問題について話し合うための会議を 2 回開催しました。 最初のバーチャルワークショップは2021年10月14~15日に公募で開催された。 このバーチャル ワークショップには、学界、産業界、政府関係者から 70 名を超える参加者があり、2 日間を通して非常に活発に活動しました (付録 A を参照)。 このワークショップでは、対面ワークショップの参加者の最終候補リストの選択に役立つトピックに焦点が当てられました (付録 B を参照)。 の

対面ワークショップは、2022 年 5 月 20 ~ 21 日にカリフォルニア大学サンタクルーズ校シリコンバレー センターで開催され、33 名の参加者が登録されました (付録 C を参照)。 新型コロナウイルス関連の問題のため出席できなかった人もいたが、出席者は2日間をパネルディスカッション、分科会セッションに費やし、その後この報告書の初期草案を書き始めた(付録Dを参照)。

Technology Nodes

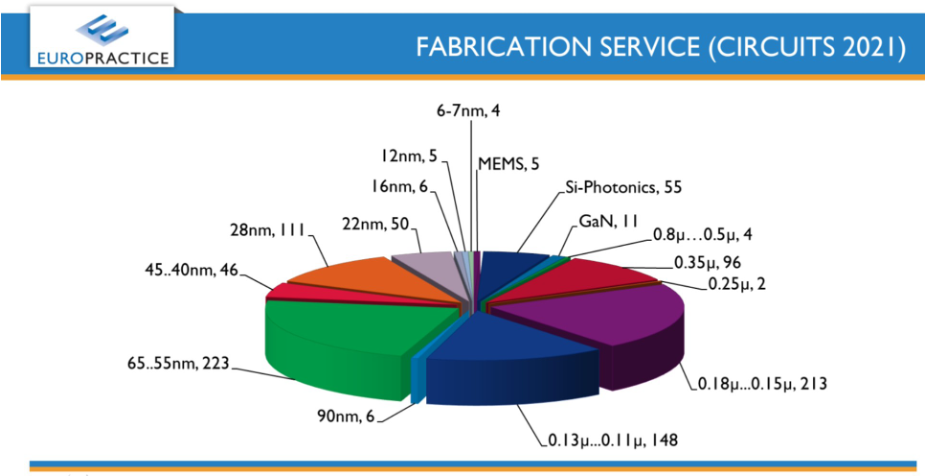

チップ設計コミュニティは、幅広い製造テクノロジー ノード (または「フィーチャー サイズ」) に依存しています。 これは、2021 年のユーロプラクティス製造サービスと 2018 ~ 2022 年の MOSIS のプロトタイピング製造サービス予約の内訳を示す以下のグラフに反映されています。 テクノロジーの選択はさまざまな要因に依存しますが、これらについては以下で詳しく説明します。 テクノロジー ノードに加えて、さらに幅広い多様性をもたらす機能が他にも多数あります。 たとえば、基本ロジック CMOS のほかに、無線周波数 (RF)、高電圧 (HV) 回路、不揮発性メモリ用のアドオンなどのテクノロジ フレーバーがあります。

Source: Lifu Chang, The MOSIS Service, January 2018-May 2022.

比較的古いテクノロジー ノード (40nm 以上) が予約のほぼ 4 分の 3 を占めています。 これは、低速センサー アプリケーションなど、小さい機能サイズを必要とするアプリケーションがすべてではないことによって部分的に説明されます。 これらのトレーリング ノード テクノロジーの使用は、学術的な調査に限定されず、アナログ中心のさまざまな商用アプリケーションでも大量に使用されています。 教育にとって、古いノードは、この分野への入り口が容易であり、新しいノードに伴うコストやその他の複雑さが無いため、魅力的です。

最近、Google と SkyWater Technology は SkyWater の 130nm テクノロジーをオープンソース化しました。これは研究者、教育者、さらには愛好家にとっても魅力的な選択肢となっています。 このテクノロジは、さまざまな有用なアナログ、ミックスドシグナル、RF 回路、および適度な性能のデジタル プロセッサやアクセラレータを設計するのに十分です。 130nm ノードには、不揮発性 SONOS (シリコン酸化物窒化物酸化物シリコン) フラッシュおよび HfOx ベースの抵抗 RAM (ReRAM) デバイスのオプションも含まれています。 さらに最近では、Google と SkyWater が、さらなるパフォーマンスの機会をもたらす 90nm テクノロジーに関する同じ計画を発表しました [23]。 GlobalFoundries による別のトレーリング ノード 180nm テクノロジー [17] の計画もあります。

高性能デジタルおよび広帯域アナログ/ミックスドシグナル/RF 回路の限界を押し上げるには、より新しいテクノロジーが必要です。 最先端技術 (SOTA) は、通常、22nm、16nm、12nm、およびより小さい機能サイズのプロセスでファウンドリによって提供される FinFET/SOI プロセス以降として定義されます。 先進的なノード (7nm 以下) を中心としたエコシステムが人工知能 (AI) および機械学習 (ML) IC 設計の研究開発をサポートしていることに注目します。

したがって、これらの分野の研究プロジェクトは通常、製造だけでなく、IP、EDA、ソフトウェアなどのエコシステムの全面的なサポートを受けています。このため、SOTAプロセスへのアクセスに対する大学からの需要が高まっています。 特に、これは個々の大学の研究プロジェクトだけでなく、DARPA と AFRL の共同後援プロジェクトでも見られます。 過去 5 年間で、22nm と 16nm に関する大学の設計プロジェクトが約 30 件ありました。 ただし、SOTA プロセスを採用しようとしている大学チームが増えているだけでなく、7nm、5nm、およびそれ以降のより高度なノードへのアクセスも提供される必要があります。

ロジック CMOS プロセス テクノロジの機能は、アクティブおよびパッシブ デバイスを追加し、相互接続テクノロジを最適化することによって強化されます。 このような強化されたプロセスは研究に広く使用されています。 たとえば、SiGe HBT は電力処理と高速および周波数性能を向上させるために追加されます。 電源管理アプリケーションに必要な電圧をサポートするために高電圧デバイスが追加されます。 また、相変化材料 (PCM) デバイスが追加され、製造後のプログラミングが可能になります。 さまざまなストレージのニーズを満たすために、DRAM、フラッシュ、ReRAM、STTRAM などのさまざまなメモリも含まれています。 このメモリは、インメモリおよびミックスド シグナル コンピューティングの研究にも使用されています。 PCM および MEMS デバイスも追加され、低損失スイッチ アプリケーションをサポートします。 MEMS デバイスは CMOS システムとも統合されており、幅広いセンシング アプリケーションをサポートします。 もう 1 つの重要な研究分野はシリコン フォトニクスです。これは、CMOS コンポーネントとフォトニック コンポーネントの両方を組み込んだ集積回路をセンシングと通信に利用します。

オープン PDK は、代表的、予測的、または実際のテクノロジー パラメーターを使用して、独自の PDK に伴う多くの課題を回避して研究と教育を可能にします。 これらの一部は、NCSU の FreePDK45 [2]、NCSU の FreePDK3 [24、p.16] など、製造不可能です。 3]、ASU の ASAP7 [25]、Synopsys の SAED 90/32、および Cadence の GPDK 180/45/7。 最近では、Google/SkyWater 130nm PDK [26] や今後登場する SkyWater 90nm および GlobalFoundries 180nm PDK [27] など、製造可能なオープンソース PDK が登場し始めています。 オープン PDK は、寛容なオープンソース ライセンスを使用して自由に利用できるか、少なくとも学術研究者が無料で簡単にアクセスできます。 これらのオープン PDK は、EDA ツール フローのセットアップ、EDA アルゴリズムの探索、アーキテクチャ設計空間の探索、および IC 設計コースの指導に役立ちますが、いくつかのトレードオフがあります。 Synopsys と Cadence の PDK は独自のツール フローでのみ動作しますが、NCSU オプションはオープンソースと独自の EDA フローの両方で広く採用されています。 ASAP7 はオープンソースと独自の EDA ツール フローの両方でサポートを獲得していますが、当初は非営利用途に限定されていたため、業界主催の研究での早期採用は限られていました。

特定のテクノロジー ノードとアクセス サービスに対するニーズは、テープアウトを研究目的か教育目的かによって大きく異なります。 研究ニーズは、研究の種類(デジタル/アナログ/ミックスドシグナル回路、アーキテクチャ、システムオンなど)に応じて、最も古いもの(180nm以上)から最新のもの(5nm以下)までのテクノロジーノードの全範囲に及びます。 -チップ設計、新興デバイス)、対象となる研究指標(パフォーマンス、エネルギー、フォームファクター、フォールトトレランスなど)、そして最終的には取り組むべき研究課題です。 教育のニーズは根本的に異なり、最先端のものを推進するのではなく、教育体験に重点を置いています。 教育では古いものを使用することがよくあります

コスト、複雑さ、法的問題を軽減するためにテクノロジーノードを導入しましたが、これでは現在、より最近のテクノロジーノードで必要とされる多くの現実世界のエクスペリエンス(例:複雑な設計ルールとサインオフ要件、より大きな寄生、変動性とノイズの増加、関連するノードの複雑さなど)を提供できません。 デザインなど)。

Summary of Current State

現在、指導テープアウトには 2 つのアプローチがあります。1 つは比較的最近のテクノロジー ノード (例: カリフォルニア大学バークレー校と CMU の TSMC 28nm) での業界の補助金と、古いテクノロジー ノード (例: コーネル大学の Efabless を介した SkyWater 130nm) での低コストのテープアウトです。 、エール大学、スタンフォード大学、UCSC)。 デザインをまったくテープアウトしない 3 番目のオプションもあります。 以下は、通常は有料の製造サービスのプロバイダーです。

-

MOSIS: MOSIS サービス (www.themosisservice.com) は、GlobalFoundries、TSMC、Intel Foundry Services、Samsung Foundry、および WIN Semiconductors ファウンドリを通じた大学向けの有料製造サービス プロバイダーです。 シリコン プロセス テクノロジーのポートフォリオは、特殊 BCD を備えた 350nm ~ 12nm FinFET の範囲に及びます。

(バイポーラ-CMOS-DMOS) およびその他のプロセス、および磁気抵抗 RAM (MRAM)。 このポートフォリオには、III-V 族化合物半導体 GaAs および GaN プロセスも含まれています。

プロジェクトは、MPW または専用 (フルマスク) 実行のいずれかになります。 MOSIS は、PDK ファイル、トレーニング、設計デバッグ、設計マイルストーン チェック、テープアウト サインオフ、およびその他の必要なサポート項目を有料顧客に提供します。 MOSIS は以前、NSF と産業界の支援を受けたテープアウトのための無料の学術プログラムを実施していましたが、2020 年に廃止されました。 -

MUSE: MUSE は、2018 年に設立された有料のマルチプロジェクト ウェーハ サービスで、現在は TSMC シャトルに重点を置いています (https://www.museemi.com)。 MUSE は当初、大学の研究者のみを対象としていましたが、最近では民間企業のサポートにも範囲を広げています。 MUSE は、一般ロジック、低電力、および RF バリアントを備えた TSMC 180nm、65nm、40nm、および 28nm への共有ブロック アクセスを提供します。 MUSE の最小ダイ サイズは小さい (TSMC 180nm MS-RF-G では 5mm2、TSMC 180nm では 5mm2)

HV-BCD-G2、および小型テクノロジ ノードでは 1mm2)。 MUSE は、すべての TSMC テクノロジーでのフル ブロックおよびプロダクション テープアウトもサポートしています。 MUSE は、対応する PDK、標準セル、I/O セル、および SRAM コンパイラへのアクセスも提供します。 - EUROPRACTICE: EUROPRACTICE (https://europractice-ic.com/) は、25 年以上にわたり、有料の MPW プロトタイピング サービス、トレーニング活動、システム統合ソリューション、少量生産で学界と産業界をサポートしてきました。 EUROPRACTICE は、ヨーロッパの学術機関やスタートアップ企業に設計ツールへのアクセスを提供します。 EUROPRACTICE は、2um ~ 12nm の範囲のフィーチャーサイズの CMOS テクノロジー、SiGe HBT BiCMOS テクノロジー、フォトニクス、MEMS、マイクロ流体、グラフェン、SiC などのテクノロジー一式を提供します。

- CMC: CMC Microsystems (https://www.cmc.ca/fab/) は、主にカナダの機関向けに有料の MPW サービスを提供しています。 さまざまな CMOS および BiCMOS テクノロジー、シリコン フォトニクスおよび MEMS プロセス、さらに III-V エピタキシーをサポートします。

- Efabless: Efabless (https://efabless.com/) は、成熟したからミッドレンジのテクノロジー ノード向けの MPW サービスを使用したプロトタイピングから少量生産までを含む、コミュニティ チップ作成のためのエコシステムを提供します。 最近、Efabless は、オープンソースおよび独自の EDA ツール フローを通じてオープンソース SkyWater 130nm PDK にアクセスするための事実上の標準になりました。 Efabless は、Google が資金提供する OpenMPW プログラムをサポートしています。このプログラムは、設計全体が完全にオープンソースであり、オープンソースで再現可能である限り、学生、研究者、専門家、さらには愛好家に無料で SkyWater 130nm でチップをテープアウトする機会を提供します。 EDA ツール。 Efabless は、MPW スロットを保証し、オープンソース要件を必要としない、有料の ChipIgnite プログラムも提供しています。 Efabless は、オープンソース SkyWater 130nm PDK、オープンソース EDA ツール フロー、および Caravel SoC ハーネスを備えたターンキー コンテナ イメージを提供し、設計とテープアウト プロセスを簡素化します。 このソリューションには、事前に設計されたパッケージング、標準 PCB 評価ボード、チップの立ち上げとテストを効率化するためのテスト ソフトウェアが含まれています。

Key Challenges

Fabrication Costs are Significant

最新のテクノロジーノードの場合、主な課題はコストであり、製造だけでなく、設計と検証の複雑さの管理、さらには設計キットやツールの使用とメンテナンスも含まれます。 一部の古いテクノロジ ノードであっても、適切な数のトランジスタを備えた設計を製造すると、すぐに数万ドルを超える可能性があります。 非常に古いテクノロジ ノードの場合、個々のテープアウト コストは低くなる可能性がありますが、コース用に多くの異なる独自のデザインを製造する必要があるため、すぐにコストが増加する可能性があります。 大学は製作コストをサポートするための内部リソースが大幅に異なり、学生 1 人あたりの 1 クラスの限られた予算は製作コストよりもはるかに少ないことを認識することが重要です。 IC 設計の確立されたプログラムを持つ大学であっても、教育テープアウトに資金を提供するために業界とのつながりを活用する必要があります。

コストに関連するさらに別の課題は、最小ダイ サイズ要件から生じます。 FinFET テクノロジ (通常は 16nm 以下) では、一部のサービスでは最小 2mm X 2mm のチップ面積が必要で、これには 100,000 ドル近いコストがかかります。

Limited Shuttle Space

シャトル プログラムは予約が殺到し、場合によってはキャンセルされる場合があります。 Google が提供し、Efabless がサポートする OpenMPW シャトルの場合、抽選システムを使用して、各シャトルで 40 個のプロジェクトのどのセットを作成するかを選択します。 古いノードなどの特定のテクノロジー ノードへの関心は、学界が主に望んでいるかもしれませんが、製造の実行に経済的に意味があるほど望ましいものではありません。 これらの問題は、研究の進捗や学生の卒業に重大な影響を及ぼします。

Legal Agreements to Access Advanced Technology Nodes are Complex

高度なテクノロジー ノードへのアクセスは、多くの場合、複雑な NDA やその他の使用制限によって管理されます。 たとえば、一部のファウンドリでは、自社のテクノロジーから競合他社の同等の製品に切り替えたいユーザーに 1 年間の「冷却期間」を要求しています。 さらに、最新のノードについては輸出管理を考慮する必要があり、多くの場合、複雑な手順やさまざまな学生の大学キャンパスへの非包括的アクセスにつながります。 場合によっては、学生の出身国やビザステータス、さらには現在の場所(米国国境内か旅行中の国外)に応じて、商用 PDK と非製造可能なオープン PDK を使用するために、単一クラス内でデュアルフローが必要になることさえありました。

Limited Access to PDKs

多くのファウンドリでは、PDK が提供される前にテープアウトを行う必要があるため、各設計チームは、デザイン キットを入手する前に、テープアウト プロジェクトを決定し、資金を提供する必要があります。 コミットメントが必要ない場合、テープアウトのコミットメントが行われるまで、限られた情報を含む PDK が提供される場合があります。 ファウンドリはプロジェクトを保証し、時間の無駄や IP 漏洩のリスクを避けるための明確な PDK 手順を必要としているため、この要件は正当です。 ただし、これは卵が先か鶏が先かの課題を当面もたらします。評価するための PDK がなければ、チームはどうやってテープアウト プロジェクトを決定できるでしょうか? 当面の次の課題は、プロセスの選択を決定するために、チームがさまざまなプロセスにテストチップのテープアウトを行う必要があるかもしれないということですが、これは通常、予算とリソースの観点からは実現不可能です。

Limitations of Non-Manufacturable Open PDKS

非製造可能なオープン PDK は、EDA ツール フローのセットアップ、EDA アルゴリズムの探索、設計空間の探索、およびテープアウト コンポーネントを使用しない IC 設計コースの指導には役立ちますが、現実的なアナログまたはミックスドシグナルの研究には十分ではありません。 これらのオープン PDK の精度は大幅に異なる可能性があり、実際のテクノロジー ノードに基づいていないため、テープアウトへの明確なパスはありません。 Google/SkyWater 130nm などのより新しい、製造可能なオープン PDK はこの問題に対処しますが、最新のテクノロジー ノードへのアクセスは提供しません。

Installing and Maintaining PDKs is Challenging

PDK は複雑で、特に高度なノード (28nm 以下) ではサイズが非常に大きくなります (1TB 以上)。 専門家による PDK のインストールには数日かかる場合があります。 多くの場合、問題が発生し、その解決にはファウンドリまたは MPW アグリゲータとの数日にわたる電子メールのやり取りが必要になります。 これらの PDK は、年に複数回更新する必要もあります。

High-School Programs and Community Colleges are Often Ignored

高校生は明日の IC 設計者ですが、現在、高校生が IC 設計を学び、実験する機会は (あったとしても) ほとんどありません。 コミュニティ カレッジは、IC 設計業界に重要な職業訓練を提供できますが、IC 設計に関連する課題により、IC 設計コースの授業やテープアウトの機会を提供しているコミュニティ カレッジはほとんどありません。

Recommendations

NSF Support for a National Chip Design Center to Manage Research and Instructional Tape-outs

国立チップ設計センター (NCDC) が、トレーニング、EDA ツール、製造サービスという設計支援の「3 つの柱」を大学に提供する集中組織として機能することが非常に必要です。

-

トレーニング: NCDC は、各鋳造プロセスを対象としたテープアウトの成功に向けたベストプラクティスについて、大学の設計チームに詳細かつ詳細なトレーニングを提供する必要があります。 トレーニングの範囲には、PDK、IP、EDA ツール、チップ統合、パッケージング バンプ設計、ファウンドリ セルの挿入、設計マイルストーンとチェックリスト、テープアウト サインオフ要件とチェックリスト、製造スケジュールが含まれる必要があります。 トレーニングには、信頼性、ESD、歩留まりの最適化、その他のナノメートル設計の問題も含める必要があります。 トレーニングは年に複数回提供するか、オンラインでアクセスする必要がある場合があります。

-

EDA ツール: EDA ツールのサポートは重要ですが、ほとんどの大学プログラムはサポートを提供していないか、サポート オプションが限られています。 NCDC は、ライセンスとバージョン要件を備えた既知のツール フローを提供するだけでなく、EDA ツールのバグやエラーを最小限に抑えるためのサポートも提供します。 1 つの方法は、リファレンス デザインを利用するリファレンス実行スクリプトをサポートすることです。 このリファレンス キットは、正確な実行を成功させるための重要なコマンドを示します。 (リファレンス スクリプトとリファレンス デザインの) サポートは、設計者が EDA プロセスを学習するのに役立ち、セットアップ、バージョン管理、誤用による特定の EDA エラーをサポートする必要性を軽減します。 設計者は、基本的なランセットと独自の追加コマンドを知っているため、より自主的なデバッグを行うことができます。 アクセシビリティを最大限に高めるには、参照ツールのフローと設計をオープンソースにして、設計実装スペースを探索するために共有、変更、拡張でき、再配布が制限されないようにする必要があります。

-

製作サービス: NCDC は研究と教育の両方の目的で製作サービスを提供する必要があります。 これには、MPW の集約、ダイシング、およびパッケージングが含まれます。

MOSIS、EUROPRACTICE、Muse、CMC、Efabless はいずれも同様のサービスを提供していますが、Google/Efabless OpenMPW の場合、最終的には有料か容量が制限されています。 したがって、これらは主に資金提供のある業界または学術プロジェクトに焦点を当てています。

NCDC は、コミュニティカレッジ、4 年制大学、大学院生がクラスデザインプロジェクトをテープアウトできる無料の指導テープアウトプログラムを再開し、管理する必要があります。 NSF はまた、集積回路設計プログラムに参加する高校生にテープアウトの機会を提供すべきである。 インフラストラクチャの課題を軽減するオプションとして、クラウドベースの設計環境を利用できるようにする必要があります。 古い CMOS ノード (180nm など) は、ほとんどの指導テープアウトに適しています。 設計品質管理プロセスを含める必要があります。

NSF Program for Research Fabrication Cost

NCDC の支援に加えて、研究テープアウトのための別の資金調達メカニズムを推奨します。 NSF Major Research Instrumentation Program (MRI) は主に機器とインフラストラクチャーに資金を提供しており、テープアウトにはあまり適していません。 NSF は共有施設 (スーパーコンピューターや望遠鏡など) にも資金を提供しており、これらの施設はリクエスト プロセスを通じて共有アクセスを提供します。 NSF が学術指導だけでなく、NSF が資金提供する研究に関連する製作費にも資金を提供するための専用プログラムを作成することを NSF に推奨します。 このプログラムは研究コアプログラムとは異なります。 コストが高い高度なノードにはメリットベースのレビューが必要ですが、指導用の古いノードには大幅に安価であるため、簡単なアプリケーション パスが必要です。

CMOS+X のパイロット活動は素晴らしいスタートですが、私たちは CMOS+X に加えて従来の CMOS 製造を含む専用プログラムを構想しています [28]。 このプログラムは、デジタル VLSI、アナログ/ミックスドシグナル回路、コンピュータ アーキテクチャ、システム オン チップ設計、それらを使用するシステムを含む新興デバイスなどを含む幅広い研究に関連する製造コストに資金を提供する必要があります。プログラムが CISE のみを介して行われる場合は、 、システムの製造に焦点を当てる必要があるが、CISE と他の局(MPS、ENG など)との提携によるプログラムでは、範囲を回路やデバイスに拡大する可能性がある。 プログラムには、複数の明示的な段階 (小規模、中規模、大規模) と、(i) 先端技術ノード上の少数の大規模製造プロジェクトへの資金提供が小規模な製造プロジェクトの資金を完全に圧倒しないようにするための研究および指導目標を含める必要があります。 (ii) 大規模な製造プロジェクトが資金調達年度ごとに費用がかかりすぎるとみなされないようにする。 製造されたシステムは、最先端の IC 設計を推進するために CISE が行っている取り組みを強調する重要な研究成果物となるでしょう。

Infrastructure Development Support for Open PDKs

オープン PDK は、教育と学術探求に不可欠な要素となっています。 ただし、上で説明したように、その用途は主にデジタル デザインに限定されています。 NSF は、アナログ、ミックスドシグナル、RF 設計者を含む、より広範なコミュニティで使用できるようにこれらのオープン PDK を拡張することに関心のある研究者や教育者にインフラ開発資金を提供する必要があります。 この資金は、これらのオープン PDK を使用するためのパッケージ化、ドキュメント、リファレンス フローもサポートする可能性があります。 IP セクションでも後ほど説明しますが、オープン PDK に基づいた完全な設計エクスペリエンスとトレーニングを可能にするために、重要な設計関連資料 (メモリ コンパイラ、IO、レベル シフタ、パワーおよびクロック ゲーティング セルなど) の開発にも資金を提供する必要があります。 主要な IP (外部メモリ インターフェイス、オンチップ NoC など) の開発により、価値と採用も強化されます。 開発資金に加えて、NCDC はそのようなインフラストラクチャと関連ツールを維持および強化し、それらの使用法を訓練し、推奨されるテープアウト EDA フローに統合するために資金提供されるべきです。

Cloud-based Design Environment

また、ユーザーがさまざまな PDK および EDA ツールのセットを試したり、重要なクラウド コンピューティング リソースを活用したりできる、安全なクラウド ベースの設計環境もお勧めします。 NCDC またはその他の管理組織が環境を維持および運用する必要があります。 クラウドベースの試用環境では、ユーザーは実行した後、テープアウトに使用する PDK を決定するか、テープアウトしないことを決定できます。 ユーザーは、高度なノード PDK を利用する必要がある EDA ツールの調査を実行することもできます。 環境はファウンドリと設計チームの両方の知的財産を保護する必要があります。 PDK で保護された環境とさまざまな PDK の試行を奨励することで、最終的にはファウンドリとのテープアウト プロジェクトがさらに増え、ファウンドリの参加を促すことになるでしょう。

Training and Education

大学は、訓練を受けた半導体エンジニアに対する新たなニーズに応える上で、大きな課題に直面することになるだろう。 2030 年までに、半導体製造の仕事の 30% を満たすのに十分な資格のある候補者しか存在しないと推定されています [29]、[30]。 コンピューターのハードウェア エンジニアはソフトウェア エンジニアよりも給与がわずかに高い傾向がありますが、その伸びは大幅に低く、全体の仕事の数は大幅に減少しています [31]、[32]。 しかし、多くの半導体関連の仕事に必要な訓練を受けている電気電子エンジニアを考慮すると、平均給与はコンピューターのハードウェアおよびソフトウェアの両方のエンジニアよりも大幅に低くなります[33]。 このため、半導体企業はコンピューターやソフトウェアの他社と比べて資格のあるアメリカ人候補者を採用するのに苦労しており、そのことがアウトソーシングやH1Bビザ労働者の雇用につながることが多い。

この現象にはいくつかの要因が考えられます。 まず、半導体教育の圧倒的な重点は修士課程および博士課程プログラムにあります。つまり、これらのプログラムへの支援と募集は通常、電気工学またはコンピュータ工学 (ECE) プログラムの学生の 3 年生から始まります。 その結果、ハードウェアおよび半導体教育のための STEM 支援プログラムは、コンピューター サイエンスやソフトウェア エンジニアリングのための強力なプログラムと比較して、事実上存在しません。 さらに、典型的なアメリカの子供は 8 ~ 11 歳の間に家庭用電化製品やモバイル デバイスを与えられ、アプリや Web サイトの開発など、より高いレベルの抽象化の利点についての十分な専門知識と理解を獲得します。 統合の成功により、最新のポータブル コンピューティング システムのモジュール性が低下しました。これは、ユーザーがハードウェア システムや関連する抽象化に触れることが少なくなったことを意味します。

残念ながら、多くの学生は、レジスタ転送レベル (RTL) 設計や電子設計自動化 (EDA) などの下位レベルを理解するメリットを理解できないこともよくあります。 IC の研究と設計の成功により、IC の複雑さがユーザーから遠ざけられたため、短縮されたカリキュラムではその複雑さを伝えることがさらに困難になりました。 業界のリーダーがよく挙げる懸念としては、新しく採用されたエンジニアが先進的なノードのツールやフローに慣れるために「オンボーディング」にかかる時間を増やす必要があるということです。

これらの教育分野での 3D プリンティングの急速な成長と展開とは対照的に、IC 設計における学生の体験学習の機会は非常に限られています。 高まる需要に応えるためには、学生の教育のかなり早い段階でコンピュータ ハードウェアとエンジニアリングに対する感謝と喜びを生み出す革新的なアプローチを開発する必要があります。

ソフトウェア関連分野での就職の障壁は、ハードウェアや半導体関連の職に比べて大幅に低いです。 たとえば、アプリケーションや Web 開発のポジションには、学士号がなくても、ましてやコンピュータ サイエンスの修士号や博士号がなくても、候補者が適切に採用できます。 業界は資格のある博士号候補者に依存しているため、半導体技術者に同等の役割は事実上存在しません。 その結果、たとえ半導体専門家のニーズにしっかりとした技術者コースの開発が含まれていたとしても、多くのコミュニティーカレッジではSTEMコースを指導するために必ずしも博士号を必要としないため、コミュニティーカレッジは多額の投資なしにそのニーズを満たすのは難しいでしょう。 半導体労働者の重要なニーズを満たすには、集積回路の開発が進むにつれて、貿易プログラムや再認定プログラムを開発する必要があります。

ECE を専攻していない学生にとっては、半導体の設計と製造における現代の問題を理解することが非常に必要です。 現代アメリカの生活のほぼあらゆる面が半導体の影響を受けているが、ECE関連分野以外で「チップ不足」の深刻さを真に理解している人はほとんどいない。 これらの問題は、もはや製造会社や EDA 企業だけに影響を与えるものではありません。 専門家らは、世界的なチップ不足により、2021年だけで米国経済に2,400億ドルの損失が生じたと推定している。 科学と工学に加えて、ビジネス、建築、法律、人文科学、芸術、社会科学、および世界情勢の分野の学生は、半導体における現代の問題についてますます読み書きできるようになる必要があります。 これらの問題はアメリカ経済の隅々に影響を与えるため、STEM教育だけでなくリベラルアーツ教育にも大きな変革が必要であることを意味します。

こうした半導体教育上の課題は、国家安全保障に不可欠なミッションクリティカルなマイクロエレクトロニクスを製造するという、すでに緊張している国防総省(DoD)の能力に影響を与えるだろう。 国防総省のマイクロエレクトロニクスの現状は、商業ファウンドリから入手できない少量の最新技術 (SOTP) および従来のマイクロエレクトロニクスの生産に依存している状態です。 国防総省は、国内の半導体製造能力の低下と世界的なサプライチェーンリスクの増大という雰囲気が課題であることを特定したが、これは新型コロナウイルス感染症の世界的なパンデミックの前に予見されていたことが判明した。 国防総省は、偽造、トロイの木馬、軍事環境における特有の信頼性の問題、予測不可能で安全でないサプライチェーンから生じる急速な陳腐化を軽減するために、資格のある半導体エンジニアの大幅な増員を必要としています。 現在の米国の教育制度は、こうした国家安全保障上の課題に対処する準備ができていません。

最後に、差し迫った「入学者の崖」により、集積回路の研究と教育における課題への対処が特に緊急性を増しています。 2008 年の景気後退と出生率の低下により、2025 年までに一般人口に占める大学生の割合が 15% 急激に減少すると推定されています [34]。 これは大学の予算に影響を与え、すでにストレスにさらされているECEおよびCS部門、特に地方の4年制大学やコミュニティーカレッジに負担をかけることになる。 半導体業界の労働力の新たなニーズに応えるには、重要な課題が存在します。学生数が 15% 減少し、ほとんどの競合業界が幼稚園から高等学校までの学生の関心を引きつけ、刺激を与えるという点でかなり有利なスタートを切っているにもかかわらず、資格のある候補者を迅速に 3 倍にする方法を見つける必要があります。 。

博士号取得前の限られた研修機会、資源の枯渇した大学、今後 5 年間で対象となる大学生の急激かつ大幅な減少、世界的な供給ラインの逼迫、半導体需要を満たすための海外ファウンドリへの依存など、不安定な組み合わせにより、限界が生じています。 IC の労働力に参加するための経路が不足しており、現代の問題に対する理解が限られている国民は、国家インフラと防衛に壊滅的な影響を及ぼす可能性があります。 現在の IC エンジニアリング パスウェイによって資格のある受験者の数が 3 倍になったとしても、教育システムは新たな需要に応えることができません。 これは、集積回路の研究と教育における多様性、公平性、包括性の問題が国家安全保障の問題であることを意味します。 2030 年以降の新たな問題に対処するには、これらの課題を解決するための革新的な「総力を挙げて」のアプローチが必要です。

Summary of Current State

VLSI と半導体教育の現状はかなり暗いです。 小中学生、幼稚園から高等学校までの生徒は、集積回路の設計概念に触れることはなく、せいぜいブラック ボックスとしてコンピューティングに触れる程度です。 彼らは半導体が社会に与える影響を理解していません。 VLSI と半導体は過小評価されています。 すべての革新はソフトウェアにあり、ハードウェアは解決された問題であるという誤った認識です。

中等教育以降の教育においては、VLSI および半導体教育の機会が大幅に不均等になっています。 VLSI クラスは非常に少なく、テープアウト (つまり、生徒が実際にチップを作成する) クラスは R1 スクールのみで行われます。 学生の大多数は R1 教育機関に所属しておらず、その他の教育機関 (R2 および少数の教育機関) には通常、プログラムがまったくありません。 ロボット工学、医学、コンピューターサイエンスなどの他の分野とのつながりが不足しており、これらの分野に対する VLSI や半導体の利点は高等教育プログラムではあまり強調されません。 「ハードウェア」プログラムは難しすぎて参入障壁が高いという偏見がこの分野にはあるため、このプログラムに参加する学生はほとんどいません。 その結果、R1校でも授業が削減されることになりました。 これまで多くの R1 学校では設計、テスト、検証の授業が行われてきましたが、そのほとんどは単学期の選択 VLSI コースに置き換えられ、前述したようにテープアウトの機会はありませんでした。

VLSI および半導体のトレーニングと教育は、主に大規模な R1 スクールで修士号および博士号プログラムの大学院生に焦点を当ててきましたが、修士号や博士号を必要としない技術者やアプリケーション エンジニアなど、他の形式の VLSI エンジニアは対象になっていませんでした。 多くの注目を集めました。

Key Challenges

Competing interests in K-12 and early UG

VLSI への学生の参加を増やすには、早い段階で学生と関わることが必要です。 しかし、初等中等学校における課外活動や「特別」教育に費やされる時間と注意力には限りがあります。 ロボット工学 (FIRST など)、コーディング (K12 キャンプなど)、人工知能、物理コンピューティング (Raspberry Pi、Arduino など) に取り組むよう学生を鼓舞し、動機付けるために、K-12 レベルでいくつかの取り組みが作成されています。 K-12 の生徒を VLSI に参加させる際の主な課題は、成熟した取り組みと、この分野に参入するために何が必要かについての理解が不足していることです。 幼稚園から高校までの生徒の VLSI 知識のギャップをどのように埋めることができるかを理解する研究はありません。 さらに、スタンドアロンの取り組みが必要かどうか、および/または既存の取り組みとの連携によって VLSI トピックを十分にカバーできるかどうかも不明です。

Lack of appropriate material and existing material is decentralized

集積回路の設計方法を学びたい幼稚園から高校までの学生、学部生、大学院生のための情報パイプラインに亀裂が生じています。 古典的な「hello world」プログラムから始まる高級プログラミング言語の研究とは異なり、VLSI のエントリ ポイントは何であるべきか、途中でどのような抽象化を行うべきかは不明です。 カリキュラム全体でコースを接続して、業界への就職や大学院への一貫した道筋を作成することにも課題があります。 さらに、EDA ツール (Cadence/Synopsys/Siemens Support、OpenROAD、EDAPlayground、NanoHUB など) のトレーニング資料はアドホックであり、アクセシビリティ、相互運用性、バージョン管理の問題があります。

Lack of trained educators

もう 1 つの重要な課題は、大学レベルであっても適切な訓練を受けた教育者が不足していることです。 VLSIを教えていた経験豊富な教員が退職しており、大学はこれらの教員を新卒者に置き換えるのが難しいと感じています。 強力な VLSI スキルを身に付けて卒業した学生は、ほとんどの大学では太刀打ちできないような高額な報酬を産業界から得ています。 多くの大学は、既存の VLSI 教育プログラムの強化はおろか、維持に必要な背景と経験を備えた教員の採用に苦労しています。

Lack of trained support staff

強力な VLSI プログラムをサポートするには、学生が使用するシステムを保守するスタッフが必要です。 このサポートには、EDA ツールの実行に使用されるワークステーションの購入と保守、EDA ツールのインストール、PDK のインストール/保守/デバッグ、EDA ツールのライセンス管理、PDK とツールの定期的な更新の実行が含まれます。 シングルシート ライセンスを必要とする EDA ツールは、サポート スタッフが最小限の大学、特に学部生に仮想プライベート ネットワークへのアクセスを許可できない大学では実装が非常に困難な場合があります。 専任のスタッフをサポートできない大学では、これらのタスクは多くの場合、専任のスタッフをサポートできない大学の教員に課せられるため、教育や研究に集中する能力が低下します。

EDA/VLSI Costs and Challenges

大学レベルで IC 設計を効果的に教えることは困難であり、見落とされがちな多くの隠れたコストが含まれます。 IC 設計を成功させるために必要な EDA ツールは非常に複雑で、インストールと保守には経験豊富な教職員が関与します (上記を参照)。 EDA 業界は教育目的で大学に無料または低価格のライセンスを提供していますが、これらの大学ライセンスに関連する法的問題により、大学がスクリプト、ノウハウ、その他の関連情報を共有して教育現場での使用と展開を簡素化することが困難になっています。 オープンソース ツールはプロプライエタリ ツールの代替として使用されることが増えていますが、プロプライエタリ ツールに比べてバグが多く、サポートが少なくなっています。 また、教育活動としてのICテープアウトには費用と時間がかかります。 学生がチップをテストするには、EDA ツールに加えて、ハードウェア ラボのリソースと技術サポートが必要です。 ほとんどの VLSI 教育は 1 学期の選択コースに移行しているため、学生がカスタム集積回路を設計、テープ出力、テストする教育体験に十分な時間をスケジュールするのは困難です。 これは特に、HBCU、HSI、女子大学、および部族大学が堅牢な VLSI 教育を提供する能力を損なうものです。

Limited Interest in IC Design

IC 設計は生活のあらゆる分野でイノベーションをサポートする重要な分野ですが、学生の間では、他の魅力的な新技術に比べて IC 設計への関心が低いです。 学生たちは、IC 設計を、革新性、機会、課題が限られた「バックエンド」インフラストラクチャ活動として見ているようです。 聡明な学生は、機械学習 (ML)、サイバー セキュリティ、クラウド コンピューティング、およびその他の人気のあるトピックに惹かれるようです。これらの分野はハードウェアに強く依存しています。 IC 設計、その機会、技術的課題についての適切な理解は、受験生、保護者、カウンセラーの間では限られています。

Lack of Diversity in VLSI Design

多様な労働力を創出するという課題は STEM のすべての分野に及びますが、この問題は特に VLSI 分野にとって困難です。その理由は次のとおりです。 (1) VLSI のプログラムを維持するために必要な立ち上げコストとリソースは、多くの場合 R1 機関のみが利用可能であり、( 2) R1 指定を受けている少数のサービス提供機関はほとんどありません (HBCU がない場合も含む)。 さらに、VLSI/EDA の分野が他の ECE 分野とどのように比較されるかは不明ですが、男女平等が欠けています。

エンジニアリングおよびコンピューター サイエンスの分野で女性を誘致する広範な取り組み (例: Grace Hopper Conference、WISE、IEEE WIE) はありますが、VLSI/EDA に対する取り組みはそれほど多くありません (例: Cadence Women in Technology Fellowship、DAC Women in Electronic Design Automation Achievement Award)。

Recommendations

Mitigate the competing interests of IC Design

私たちの最も重要な推奨事項は、IC 設計の研究、トレーニング、人材育成を、特に NSF と CISE の明確かつ目に見える焦点にすることです。 全員の関心を引く利害が競合しており、NSF と CISE が IC 設計の研究、教育、トレーニングを、それ自体の分野として、また学際的な教育の中核要素として特定し、支援することが、影響を与えるために重要です。

私たちの最初の推奨事項は、NSF が幼稚園から高等学校までおよび大学のプログラム向けのブートキャンプ、チュートリアル、教育リソースの開発をサポートすることです。 K-12 の活動の目標は、教育者が生徒に IC 設計の世界について興味を持ってもらえるようにすることです。 これには、すべてのソフトウェア アプリとゲームがそれらを実行するためにどのようにハードウェアを必要とするか、また最新の iPad や Bluetooth デバイスを含む世界のテクノロジーの進歩におけるムーアの法則の役割についての説明が含まれます。 ハードウェアの役割は、既存のプログラミング言語やロボット プログラムにも関連付けられる必要があります。 学部レベルでは、NSF は VLSI の新しいプログラムのない教育機関での開発を奨励し、既存の教育機関でのプログラムを拡張し、ロボット工学、生物医学工学、または航空宇宙を統合することによって IC 設計の学際的な価値を強調するプログラムの開発を奨励する必要があります。 。 他の多くの分野はチップに依存していますが、限られた用途で既製のハードウェアのみを使用しています。 「もしも」の質問を強調することで、高度なチップがどのように低消費電力、高解像度、そして分野全体のイノベーションを促進する新機能につながるのかを学生に示すことができます。 大学院レベルでは、これらの分野の労働力の高齢化に対処するために、IC設計における大学院研究への支援を復活させる必要がある。 さらに、エネルギー効率が高く、持続可能で安全なコンピューティングなどの新興分野での継続的な課題は、引き続き重要な研究の豊富な分野です。

私たちの 2 番目の推奨事項は、NSF が社会における VLSI と IC の重要性を強調する広報およびメディア資料の開発を支援することです。 これは、これらの資料が、この分野における CISE 提案の広範な影響への貢献として歓迎されるだけでなく、他の人が利用できるようにこれらの資料をホストする情報交換所の設立を示唆するものである可能性があります。

これに関連して、NSF はあらゆるレベルの学生がこの分野への参加を奨励できるよう、コンテストの開発を支援する必要があると考えています。 K-12 レベルでは、これは FIRST Robotics、iGEM、MIT App Inventor、IceStudio と同様の開発になる可能性があります。 それは「Girls who Fab」の形をとる可能性があり、医療、神経インプラント、ブロックチェーンなどの主要なエキサイティングなアプリケーションに焦点を当てることができます。 IEEE SSCS PICO デザイン コンテスト [35]、ICCAD CAD コンテスト [36]、DAC システム デザイン コンテスト [37]、ISPD デザイン コンテスト [38] などの既存のコンテストの継続的なサポートは、これらのスキル セットの継続的な重要性を強調するのに役立ちます。 DAC ヤング スチューデント フェロー プログラムなどのチュートリアルも同様です [39]。 最後に、IC 設計 (おそらく最初は FPGA を使用する) が学際的なチームの取り組みの一部であるメーカーのようなスペースを奨励することは、より広い範囲のイノベーションにおいて IC 設計が果たす役割を強調するのに役立つでしょう。 これには、混合信号アプリケーション、AI アプリケーション、サイバーセキュリティ アプリケーション、ロボット工学/制御アプリケーションなど、電気工学およびコンピュータ工学のカリキュラム全体に関連する概念を強調することが含まれる可能性があります。

別のオプションは、CSGrad4US [40] に似た「ChipCorps」を提案することですが、IC 設計を目的としています。これは、国益や愛国心だけでなく、持続可能性、エネルギー効率、地球を救うという欲求によって動機付けられる可能性があります。 最後に、NSF は、IC 設計概念をコア STEM カリキュラムに組み込む研究を奨励することができます。 たとえば、ブール論理とスイッチとしてのトランジスタは、中学校の数学「イノベーション」のカリキュラムに簡単に組み込むことができます。

Support shared educational materials

教育のあらゆるレベルでの教育と学習の障壁を取り除くために、私たちの 2 番目の推奨事項は、質の高い教材を維持し、教育の障壁を取り除くことができる集中機関を設立することです。 これは、National Chip Design Center (NCDC) の一部であるか、大学や単科大学での教員をサポートするためのトレーニング、セミナー、講義、プラグ アンド プレイ ラボ、および採点ルーブリックを開発および普及する情報交換所として機能する別の機関である可能性があります。 、さらには個人の学習者も。 教育機関は、ライセンスの提供と管理、機密情報の管理、テストなど、VLSI の教育とトレーニングに必要な膨大なレベルのサポートを運用するためのインフラストラクチャとノウハウを提供する必要があります。ワークショップとトレーニングでは、初級レベル、中級レベル、 あらゆるレベルでの継続的な学習を奨励したり、学習者を新しい分野に移行したりするのに役立つ高度なコンテンツを提供します。 たとえば、学生は FPGA 設計のトレーニングを受けて、VLSI 設計スキルを開発し、FPGA と VLSI フローの両方で使用されるツールをサポートします。 カリキュラムはサポートする必要があります

テープアウトまたは「疑似テープアウト」(レイアウトはするが加工は行わない)により、学部の学習は理論と現実を結びつけた「フルスタック」になります。 教育は、テスト設計 (DFT)、機能検証、システム オン チップ (SoC) などの重要なトピック、さらにはさまざまな研究焦点 (フォトニクス、量子、ML など) を含むようにさらに拡張される必要があります。 中央機関があれば、ベストプラクティスの資料や授業の資料を簡単に共有、更新、適応させることができます。 NSF は、教材ライブラリをさらに発展させ、ワークショップを改善するために、中央組織に教材を提供するために VLSI 研究助成金を提供する必要があります。

優れた教科書の開発は、関連するコースやプログラムの指導に役立ちます。 Patt と Patel の「Bits to C」に関する本 [41] に加えて、最後にチップ製造を含む新しい本「Bits to Chips」も役に立つかもしれません。 さらに、学生をコンピュータ工学や IC 設計に興味を持ってもらい、「Apps to Silicon」をカバーする新入生レベルのコースを開発することも役立つかもしれません。 したがって、NSF は、BME/CS/MechE/材料科学の学生を受け入れ、プログラムの早い段階でコンピュータ エンジニアリングの学生とペアになって、IC 設計 (または FPGA 設計) を構築するコースのモデルを検討する必要があります。 これは、14 歳の子供にチップの作り方を教える幼稚園から高校までの取り組みと同じようなものかもしれません。 これらすべての場合において、この議論には、これらのクラスの範囲の実現可能性だけでなく、その取り組みの主要な学習目標も含める必要があります。

Educator training for VLSI programs

VLSI および IC 設計分野における訓練を受けた教育者の不足と労働力の高齢化に対処するために、NSF は夏季研修プログラムを支援すべきである。 これらのプログラムは全国の R1 機関で主催され、地域の学校の教員の研修をサポートするように設計されるべきです。 教員は、ツールと設計フローに加えて、クラウド内の EDA や FPGA 開発ボードなどの集中リソースにアクセスする方法を学ぶ必要があります。

NSF はまた、特に VLSI プログラムが存在しないか限定されている学校において、VLSI に焦点を当てた若手教員に対する NSF キャリアタイプ賞を支援し、これらの学校がこの分野の教員を雇用することを奨励すべきである。

Lack of trained staff

国立チップ設計センターは、複数の機関に割り当てられる EDA ツールやティーチング・アシスタント (TA) のサポートを含む、IC 設計プログラムをサポートする集中的な場所として設立されるべきです。 これらの NCDC TA は、IC 設計に必要なツールのインストール、アクセス、構成に役立ちます。 また、テープインとテープアウトの両方のクラスを支援するための IP とインフラストラクチャを作成できるスタッフもサポートする必要があります。

EDA/VLSI costs and challenges

EDA ツールとテープアウト授業に関連するコストと課題に対処するために、NSF は教育者のサポート コミュニティを作成することで、オープンソース ツール、設計フロー、ベスト プラクティス、スクリプトやその他のリソースの共有を引き続きサポートする必要があります。 ベスト プラクティスのより多くの交換を促進するために、引き続き EDA ベンダーを関与させる必要があります。 NSF はまた、NCDC の一部として複数の大学が使用できる試験やその他の資本設備のための集中的な地域リソースの創設にも資金を提供すべきである。 このテスト施設では、短い対面トレーニングとリモートの FPGA ベースのテストを組み合わせる必要があります。 また、大規模な大学がコンピューティング リソースやライセンスを近隣の機関と共有することを奨励することもできます。

Diversity & Inclusion

VLSI と IC の設計を教える際の基本的な問題を理解するには、調査を行う必要があります。 これらの結果を利用して、VLSI 教育を拡張して、より多くの学生を大学院の VLSI トレーニングに備える必要があります。 たとえば、R2 の学生が VLSI の R1 大学院プログラムに入学するには、事前トレーニングが必要です。

VLSI 分野におけるジェンダーと人種の多様性の欠如に対処するには、この問題を理解する必要があります。 調査研究は、少数派グループがどこに登録されているかを理解し、彼らの機関がこの分野への道を確保する方法を特定するために実施されるべきである。 これには、マイノリティを支援するすべての機関が持続可能な VLSI プログラム、または VLSI プログラムへの完全なアクセスを提供する地域パートナーを確保することが含まれます。

これらの研究は、さまざまな社会経済的背景を持つ学習者を適切に教育するための適切な学習経路にも取り組む必要があります。 VLSI トレーニング/チップ設計の重要性について、生徒の意識に効果的に取り組み、影響を与えるにはどうすればよいでしょうか? 学生を半導体業界に引き付けるにはどのような戦略が効果的ですか?

EDA Tool Flows

電子設計オートメーション (EDA) 業界は比較的歴史が浅く、人気が高まったのは 1980 年代初頭になってからです。 これは主に、ミード・コンウェイ時代にコンピュータ工学(電気工学のみではなく)設計者の数が増加したことによって促進されました。

[42] また、ハードウェア記述言語、合成、および標準セルを使用する特定用途向け集積回路 (ASIC) 設計スタイルの出現も同様です。

最も初期で最も成功した EDA ツールの 1 つは、1969 年にバークレーのクラス プロジェクトとして回路シミュレーション用であり、最終的に SPICE につながりました [43]。 同様に、Magic (1984) [44] や Electric (1983) [45] などの多数のレイアウト ツールの作成は、MOSIS 製造サービスを通じてスケーラブル CMOS (SCMOS) 設計ルールを使用する Mead-Conway 設計を促進するのに役立ちました。

最初の配置配線 (P&R) ツールは 1970 年代半ばに ASIC 設計用に作成され、VLSI Technologies (1979)、LSI Logic (1981)、その後の TSMC (1987) などの企業によって最初に提供されたファブレス半導体ビジネス モデル中に使用されるようになりました。 。 これらのツールは、1981 年に最初の商用 EDA 企業を設立し、1984 年にデザイン オートメーション カンファレンスの設立につながりました。EDA コンソーシアム (EDAC) は 1988 年に設立され、IEEE および ACM とともに DAC の長年の共同スポンサーでした。 IBM、Intel、TI などのいくつかの企業には、統合デバイス製造 (IDM) ビジネス モデル用の独自の EDA ツールの歴史があります。

Intel と、程度は低いものの TI だけが今もこれを行っています。

独自の商用ツールは、積極的な開発、高性能、安価な (または無料の) アカデミック ライセンスにより、80 年代後半から 90 年代にかけて学界で人気を博しました。 カンファレンス全体は教育者によって作成され、独自の EDA ツールを使用したベスト プラクティスに関する出版物が出版されました [46] ~ [48]。 特に、マイクロエレクトロニクス教育に関する IEEE 国際会議 (MSE) は 1999 年から 2018 年の奇数年に開催され、「姉妹」会議であるマイクロエレクトロニクス教育に関する欧州ワークショップ (EWME) は偶数年に開催されました。

これらのカンファレンスは主に VLSI 教育の衰退とともに発展しており、せいぜい大規模なカンファレンスの 1 つのトラックとして存在しています。

現在、EDA は半導体チップの設計、検証、テストのためのツールを扱う約 130 億ドルの産業です。 EDA の「ビッグ 3」企業は引き続き Synopsys、Cadence、Mentor Graphics (現在は Siemens の一部) であり、市場のほとんどをカバーしています。 Magma Design Automation のような成功したスタートアップ企業も時折ありますが、Avant! 数例を挙げると、Corporation、Cascade Design Automation、Apache Design Systems など、最も一般的な結果は大手 3 社による買収です。

今後は、IC 設計において EDA テクノロジーがますます中心的な役割を果たしていくことを理解することが重要になります。 システムの革新は、設計を実行できるかどうかにかかっています。 の

よく嘆かれている設計能力のギャップは、設計者が最先端ノードのチップ上の可用性トランジスタを使用できる能力がますます低下していることを意味します。 設計能力は、設計自動化テクノロジ、つまり EDA に依存します。 2022 Design Automation Conference の最近の開会基調講演で、Mark Papermaster (AMD CTO) は、3nm ノードで見られる利点の半分以上は設計技術の協調最適化 (DTCO) によるものであり、この割合は増加していると指摘しました。 急速に。 DTCO と継続的なアルゴリズムおよび機能の革新により、EDA は今世紀のムーアの法則の価値軌道の重要な要素である「設計ベースの等価スケーリング」を可能にします。 したがって、NSF は、VLSI 設計だけでなく、EDA の基礎となる技術の教育、研究、人材育成もサポートする必要があります。

Summary of Current State

EDA 企業は通常、自社独自のツールのリファレンス フローを提供していますが、これらのフローは、通常、複数のベンダーのツールや、さまざまなテクノロジとそれに関連する PDK の特定の設定を必要とする設計プロセス全体をカバーしているわけではありません。 このため、半導体企業や学術機関は独自の設計フローを開発する必要があります。 その結果、膨大な数の多様なフローが存在し、一貫性がほとんどありません。 これらのフローの開発、デバッグ、サポートにかかるコストは、ほとんどの学術機関のリソースをはるかに超えています。

独自ベンダーからの安価で無料の学術ライセンスへの依存は寛大に見えるかもしれませんが、実際には、研究の独立性や相互運用性への取り組み意欲に悪影響を及ぼします。 特に、ほとんどのライセンスではベンチマーク比較が明確に禁止されており、研究が妨げられています。 場合によっては、学術機関が独自のツールフローを変更して共有しようとすることもありますが、情報が競合他社の手に渡ることを望まない企業は、ツールのライセンスを取り消すと脅迫しています。 学者が企業に影響を与える行為を行って研究に必要なツールにアクセスできなくなった場合、その研究分野は基本的に立ち入り禁止になります。

独自のツールには事実上サポートがありません。 通常、1 人または 2 人の被指名者がオンライン ヘルプにアクセスでき、講師や生徒からの質問はすべてこの担当者を経由する必要があります。 通常、少なくとも 1 人の被指名者は設計の知識を持たない IT スタッフ メンバーです。 一方、オープンソース ツールは完全にコミュニティでサポートされているため、サポートの品質とレベルは非常に散発的です。 オープンソース ツールのドキュメントは不足しているか、古いことがよくあります。

最近、一部のコースでは、SkyWater 130nm オープンソース PDK [26] を使用して、Efabless の OpenROAD [46]、OpenLANE [47]、および Caravel/OpenMPW [51] インフラストラクチャの使用を開始しました。 これらは独自のツールに比べてアクセスしやすいものの、サポートの問題があり、ツールのほとんどがボランティアでサポートされているため、安定性に問題があります。 さらに、これらは TCL/Python スクリプト、ベースライン フロー、分析レポートの理解、その他の基本的なスキルを教えますが、最終的には今日のほとんどの業界の仕事で使用されているものとは異なります。

Key Challenges

Access barriers

人材育成においては、新世代ができるだけ早い段階から VLSI 設計に興奮し、魅力を感じられるように、ツール、フロー、設計イネーブルメントへのアクセスに対する障壁を取り除くことが重要です。

Standards and interoperability

今日の設計フローは、実際にはオープンではない標準に依存しています。 例えば、物理検証をサポートする標準フォーマット(例えば、「デザインルールチェック」)は存在せず、システム設計制約に関するオープンフォーマットも存在しない。 研究開発の安定した基盤には、完全にオープンソースのリファレンス実装とライブラリが必要です。 現在、オープンソースのリファレンス実装とライブラリを必要とする研究への資金提供ポリシーは存在しません。

Reproducibility

科学と知識の進歩は再現性にかかっています。 報告された結果を再現するために使用される方法が自由かつオープンに共有できない場合、前進は妨げられます。 独自のツール ベンダーによって面倒で制限的な規定が課されており、これは IC 設計と EDA 領域の進歩に萎縮効果をもたらします。 学術界と産業界の間の再現性と協力には、多くの場合、複雑な法的合意が必要です。 NSF は、データ管理計画における公的にアクセス可能な成果物に関する IC 設計および EDA 研究の分野において、独自のポリシーに従っていません [52]。 特に、連邦規則集 (2 CFR 215.36) によれば、研究者は「研究結果を検証するために必要な、科学界で一般的に受け入れられている記録された事実資料」と定義される研究データを共有する必要があります。 これには、結果を再現するための EDA ツールとフローが含まれる必要があります。

オープンソース EDA の場合、この障害は存在しませんが、比較は多くの査読者によって出版できる「最先端」とは見なされないことがよくあります。

Applicable training

就職の準備のために、業界で使用されている最新の商用ツールに関するトレーニングを受けることが非常に望ましいです。 これらの「商用」ツールはオープンソース ツールまたは独自のツールである可能性がありますが、現在業界のほとんどが独自のツールを使用していることに注意してください。 実地訓練の量を減らすために、あらゆる訓練を同じツールで行うことが望ましい。 ただし、一部の必須スキルは、学生が使用した可能性のある特定のツールに依存せず、より広範なツールのセットが利用する概念に依存します。

Maintenance costs

設計フローとオープンソース ツールにはメンテナンス (トレーニング資料、ツールの更新、進化するコンピューティング プラットフォーム、ライブラリの変更など) が必要であり、継続的なコストがかかります。 このメンテナンスのコストは最小限に抑えることができますが、完全になくすことは非常に困難です。 オープンソース プロジェクトをリリースする研究プロジェクトは、重要な学生貢献者が卒業すると放棄されることがよくあります。 NSF やその他の研究機関は伝統的に継続的なメンテナンスに資金を提供していません。

Recommendations

Improve accessibility

NSF は、トレーニング、調査、研究において業界品質の結果を生み出すことができる設計フローのメカニズムとインフラストラクチャを積極的にサポートする必要があります。 これにより、ツールの起動、調整、メンテナンスなどの無駄や冗長な作業が削減されます。 デザイナーと教育/コースのサポート。 教育/実験用資料の開発と保守。 独自の EDA ツールとオープンソース ツールの両方に対して 1 つ以上の「標準フロー」を定義および維持する必要があり、高度なノード、古いノード、および FPGA ターゲットで利用できるようにする必要があります。

NSF がこれらのフローを一元管理し、品質が保証された簡単な「立ち上げ」を提供するサービスを、おそらく国立チップ設計センターで確立することをお勧めします。 たとえば、CMC Microsystems (カナダ) は、「設計を確実に成功させるために、設計プロセスを通じてユーザーをガイドするのに役立つ設計方法論」を提供しています [53]。

設計フロー ユーザーが「何をすべきか」を知るために CMC 設計環境をガイドするステップバイステップの説明

設計チェックリスト 実装を確実に成功させるために設計で考慮すべき項目のリスト

設計チュートリアル 設計フローを実行するための教材。 サンプル設計ファイルやライブラリも含まれる場合があります。」 [53]

同様に、工業技術研究所 (ITRI、台湾) と IMEC/EUROPRACTICE (ヨーロッパ) は、学者の障壁を劇的に下げる構造化されたフローと受け渡しポイントの例を提供しています。

Promote sharing of methodologies and flows

NSF は方法論とフローを共有する研究プロジェクトに資金を提供する必要があります。 これには、初期リリースだけでなく、コミュニティへの継続的なメンテナンスとサポートも含まれる必要があります。 プロジェクトの成功には、研究出版物や引用だけではなく、ユーザーの数も含まれる必要があります。 研究テーマに必要な広範な影響と同様に、すべての提案には「コミュニティサポート」要素が含まれている必要があります。

学術ユースケースと産業ユースケースの間で完全にオープンソースのフローがどのように共有されるかを示す例は、機械学習の分野です。 Google が TensorFlow 環境をオープンソース化したとき、ML の研究開発の量は TensorFlow によって大幅に加速されただけでなく、PyTorch などの代替ソリューションも劇的に増加しました。 同様に、LLVM や GCC ツールチェーン スイートなどの他の完全にオープンソースのソフトウェア リファレンス フローは、学術研究と業界の間のギャップを埋めるのに役立ちました。 これに応えて、Google、Microsoft、Amazon、Intel、AMD などの企業は、研究者が新たなイノベーションに集中し続けることができるように、膨大な数のソフトウェア エンジニアリング リソースをこれらのプロジェクトに提供してきました。

Promote common formats for data interchange

NSF が次の取り組みを支援することを推奨します。(i) フローの開発と配布における現在のギャップとリスクを特定する。 (ii) データ交換のためのオープンな正規フォーマットを定義する。 (iii) 参照実装を開発する。 (iv) これらのフォーマットの採用をサポートします。

標準と中間フォーマットに関しては、採用前に少なくとも 1 つの完全にオープンなソリューションを備えた複数の独立した実装を求める W3C の要件と同様のポリシーを持つことは、研究開発のための安定した永続的な基盤を構築するのに役立ちます。

共通フォーマットを持つことの重要な利点は、アクセシビリティと共有というこれまでの目標を促進できることです。 これは「フロー ランナー」プラットフォーム (Hammer、mflowgen、SiliconCompiler、OpenLane など) で見られ、チップ設計状態 (合成可能な RTL、フロアプラン DEF など) 間でのツール (論理合成や配置配線など) の互換性を可能にします)。

Role of open-source EDA tools and flows

これらの正規フローを確立して共有するための最も簡単な最初のステップは、オープンソース ツールとオープン イネーブルメント (つまり、PDK とライブラリ) のフローの開発と保守をサポートすることです。 これは、NDA、輸出管理、その他の潜在的なアクセス障壁の必要性を回避することで、シンプルさを最大限に高める特別で非常に影響力のある組み合わせです。 このサービスの最終的な目標は、ツールに依存しないフロー (またはフローのファミリー) を維持し、さまざまなオープンソース ツールや独自のツールをフロー内で使用できるようにすることです。 OpenROAD と OpenLANE は、ユーザーがツール自体のさまざまなコンポーネントを調整できるため、このフローの開始点として適しています。 OpenROAD は、2019 年からの IEEE CEDA 設計自動化技術委員会の「ロバスト デザイン フロー」(RDF) の中核であり、目覚ましい成長を遂げていますが、その将来は不透明です。 不足しているコンポーネントも多数あります。 完全にオープンソースで編集可能、柔軟かつ拡張可能な RTL から GDS へのツール チェーンは、独自の IC ツールでは提供できないものです。 さらに、オープンソース ツールは、独自のツールでは実現できないいくつかの基本的な役割を果たします [54]。 (i) オープンソースは、ソース コード自体を通じて EDA アルゴリズム、ソフトウェア アーキテクチャ、およびソフトウェア開発を教えることにより、EDA 人材の育成を可能にします。 DAC-2022 のパネルディスカッションで、Cadence の Charles Alpert 博士は、OpenROAD での開発経験により、開発者が組織に採用されてから 2 年間の学習曲線を節約できると述べました。 (EDA ツールについての洞察は、「ボタンを押す人」ではなく、設計方法論の革新者を育成するのにも役立ちます。) (ii) オープンソース ツールの使用を自由に拡張できるため、現在では実現不可能なシステム レベル、アルゴリズム、アーキテクチャの探索が可能になります。 独自のツールを使用して。 (iii) オープンソース ツールは自由に共有可能なデータを生成できます。 重要なのは、これにより、IC 設計のための AI および機械学習の研究の妨げがなくなるということです。

これらの正規フローは、独自のツールと直接競合することを意図したものではありません。 ただし、OpenROAD から生まれる開発/革新の一部は、商用ベンダーによって統合/採用される可能性があります。 企業は、使用できないツールには投資しません。また、研究を本番環境に移行するコストが非常に高い場合にのみ、最小限の投資を行います。 たとえば、Google の研究哲学ページ [55] から: 「私たちは常に、科学出版物が私たちの研究活動の多くにとって重要な要素であると考えてきましたが、基礎研究プロジェクトの場合、オープンソース コードのリリースと新しいデータセットは特に価値があります。 」

NSF は、新しいフロー抽象化と EDA ツールに関する研究を奨励する必要があります。 Hammer、mflowgen、SiliconCompiler、OpenLane はすべて、理解しやすく再ターゲット可能なフロー抽象化を提供すると考えることができます。 オープンソースまたはプロプライエタリを含む、さまざまなツールをフロー ステップ (合成や詳細なルーティングなど) にプラグインできます。 ミード・コンウェイ時代はデジタル設計の抽象化を高めましたが、ソフトウェア開発者が次世代チップを設計できるように抽象化を高める新しい時代が必要です。

Intellectual Property (IP)

知的財産 (IP) は、再利用可能な半導体設計コンポーネントを指します。 通常、これらはデジタル、ミックスシグナル、またはアナログ コアの形でシステム オン チップ (SoC) で利用され、処理コア自体、メモリ インターフェイス、コプロセッサ、ネットワーク インターフェイス、センサー、 コアの他に、スタンダード セル ライブラリ、入出力 (IO) パッド ライブラリ、メモリ (コンパイラ、コントローラなど) も IP とみなされます。

IP の再利用により、設計者は既成の設計を使用できるようになり、全体的な生産性が向上します。 IP は、要件に応じて、ハード (特定のテクノロジーのレイアウト レベル) またはソフト (動作レベルで、レイアウトを作成するための合成、配置、配線を通じてテクノロジー間で移植可能) のいずれかとして提供できます。 ハード IP はアナログおよびミックスドシグナルに好まれることが多いのに対し、デジタル IP は動作的なものが多く、Verilog などのハードウェア記述言語 (HDL) で実装されます。

設計検証はおそらく設計の中で最も時間のかかるコンポーネントであり、IP の再利用により、設計者はコアが検証されていると想定して、全体的な設計と検証の労力を軽減できます。 ただし、設計 IP とのインターフェイスには追加の検証と SoC 設計者が必要になる場合があるため、システム検証に重点が置かれます。 ARM などの企業全体は、IP を顧客にライセンス供与し、その結果得られる設計に対してライセンス料またはロイヤルティを請求することでビジネスを行ってきました。

企業はサードパーティから IP のライセンスを取得するか、独自の IP セットを保有します。 このため、機密性と基盤となるインフラストラクチャには複数の層があり、そのすべてが学者が設計を再現したり、システム全体に関わる高度なトピックを教えたりすることを困難にしています。

Summary of Current State

教育機関や研究機関がアクセスできるものと、設計を実現するために必要なものとの間には大きな隔たりがあります。 一部の R1 機関は産業提携を通じて IP にアクセスできますが、大部分はアクセスが制限されているか、まったくアクセスできません。

Cell Libraries

独自の商用ライブラリを入手するのは困難です。 テクノロジーの章での議論と同様に、複雑なライセンスとデータ共有には多くの問題があります。 多くの場合、「ブラック ボックス」ライブラリとモデルは、全体のレイアウトを持たず、代わりにセル (またはコア) の「抽象的な」ビューだけを持って提供されます。 これにより、学生は内部を見ることができなくなり、スタック全体を探索することができなくなります。 これらのライブラリは、ファブ (TSMC、Intel など) およびサードパーティ プロバイダー (ARM など) から入手できます。 さらに、企業によっては、契約上の表現により、特定の細胞ライブラリーを研究および/または指導に利用することを禁止している場合があります。 これは最終的に、スタンダード セル ライブラリを適切に使用する方法に関する知識を学生に与えるのに悪影響を及ぼします。

Memories

メモリは基本的な構成要素であり、細胞と同じくらい重要です。 メモリは、特定のサイズのハード IP ブロックとして利用できるか、メモリ コンパイラによって生成される場合があります。 多くのメモリ コンパイラでは、生成できるメモリのサイズとオプションの範囲が限られています。 標準のスタティック ランダム アクセス メモリ (SRAM) 以外にも、レジスタ ファイル、FIFO などのメモリのバリエーションが多数あります。

独自のメモリ コンパイラはファブまたはサードパーティによって提供される場合がありますが、多くの場合不変であり、製造契約が締結されるまで内部のすべてを省略してメモリ自体のブラック ボックス ビューのみを提供する場合があります。 メモリ コンパイラは、TSMC または他のファブとの契約により利用可能です。

OpenRAM [56]、[57] と呼ばれる、オープンソースで積極的に開発されているメモリ コンパイラが 1 つあります。 これは、SkyWater 130nm でシリコン検証済みメモリを製造するために使用されており、FreePDK45 および AMI 0.35/SCMOS もサポートしています。 OpenRAM は Google/Efabless OpenMPW プログラムと提携しており、Caravel テスト ハーネスの一部としてすべての MPW 設計と多くのユーザー プロジェクトにコアを搭載してきました。 5 つの OpenRAM テスト チップが製造され、最初のチップが受け取られ、機能することが確認されました。

Soft/Hard Digital/Analog Cores

最も悪名高い仕様は、幅広い熱意と採用を受けている RISC-V 命令セット アーキテクチャ (ISA) です [18]、[58]。 多くの RISC-V コアが利用可能になっています [59] ~ [63]。

オープンソースの IP リポジトリはいくつかありますが、一般にそれほど活発ではありません。 たとえば、OpenCores.org には多数のコアがあり、その多くは未検証です。 デジタルコアとアナログコアの両方を備えた UMIPS と呼ばれるリポジトリがありましたが、20 年近く更新されていません [64]。 さらに、IP はほとんどが TSMC の単一の 180nm プロセス用であり、NDA が必要でした。

独自の IP を保有する企業は多すぎてリストできませんが、ARM、Dolphin、SiFive、Synopsys などが含まれます。これらはすべて高品質の IP を提供していますが、ライセンスが必要で、テープアウトが計画されるまでは「ブラック ボックス」モデルのみを提供する場合があります。

Standards

IP の配布方法を標準化するための取り組みがいくつか行われてきました。 これらには、構造やツールだけでなくデータベース モデルも含まれます。

OpenAccess と呼ばれる「オープン」データベース標準の使用が推進されていますが、これは実際にはオープンソース ソリューションではなく、完全なアクセスを得るには複雑な契約とメンバーシップが必要です。 これらの形式は標準化されておらず、誰もが使用する形式でもありません。 これは最終的に、IP を効果的かつ効率的に利用する方法に関する問題につながります。

IP-XACT は、IP を共有するための標準構造を提供する XML 形式です [65]。 FuseSoC は、IP を配布および統合するためのパッケージ管理システムです [66]。

IP の再利用もサポートするインターフェイス標準が多数あります。 これらには、オープンソースの Wishbone バス [67] や、ARM AMBA [68]、IBM CoreConnect [69] などの商用バスが含まれます。

Key Challenges

最新の IC を構築するには多くのサポート インフラストラクチャが必要ですが、学者はほとんどアクセスできません。 ここ数十年で、標準セル ライブラリは、古いテクノロジまたは制限付きライセンスを通じて、制限された方法でアクセスできるようになりました。 最近でも、通常の SRAM や不揮発性メモリを含むメモリ コンパイラは依然として大きな課題となっています。

しかし、知財に関する根本的な課題の 1 つは、依然として検証と文書化です。 IP の検証は、誰でも使用できる有用で信頼性の高い IP を作成するために不可欠です。

Fundamental IP

高品質で使いやすく、基本的で簡単に変更およびカスタマイズできる IP へのアクセスが不足しています。 この欠如は、研究結果の再現性や学生のトレーニングに重大な影響を及ぼします。 少なくとも、次のような完全なデジタル システムが必要です。

- スタンダードセルライブラリ

- 補助セル(タップ、レベルシフタなど)

- I/Oパッドセル

- DFT 対応セル

- メモリコンパイラ (フラッシュ、SRAM、DRAM、RRAM)

上記の最小限の IP セットに加えて、物理世界と対話するシステムに必要な追加の混合信号コンポーネントとアナログ コンポーネントがあります。

- フェーズロックループ (PLL)

- アナログ - デジタル コンバーター (ADC)

- デジタル - アナログ コンバーター (DAC)

- ユニバーサルシリアルバス(USB)

- 電圧レギュレータ (LDO など)

Complex and restrictive licenses

教育、研究、プロトタイピングのために IP にアクセスするには、アクセス料金や製造契約に加えて、複雑な NDA が必要です。 ほとんどの大学が、業界とつながりのある選ばれた少数の R1 学校へのアクセスを制限するような協定に署名することは不可能です。

研究資産(すべての EDA フロー、IP、その他の分野)のリリースのための「学術のみ」および「非営利」ライセンス手法の普及により、学界と産業界の協力が妨げられ、産業界が投資を支援するインセンティブが減少しています。 これにより、ライブラリのライセンス付与方法に問題が発生し、教室で使用できなくなる場合があります。 最終的に、学生は通常、フル機能の商用グレードのスタンダード セル ライブラリにアクセスできなかったり、アクセスできなかったりするため、苦しむ傾向があります。 悲しいことに、これにより、学生は業界でよくある分野の訓練を受けられなくなります。

Lack of maintenance and verification

利用可能なオープンソース IP は十分に検証されておらず、保守されていません。 多くの研究プロジェクトは、結果として得られる知的財産をまったく共有しません。 学生は卒業し、バグ修正、拡張機能、その他の改善のためのリソースがないため、利用可能になったプロジェクトは通常、最初の作成後は静的なままになります。 一般に、作成された知的財産は研究プロジェクトを証明するのに「十分」に検証され、それ以上の作業は卒業を遅らせるだけであり、教員の昇進にはつながりません。 EDA ツール フローのアップグレードでは IP の変更が必要な場合があり、新しい機能の追加または拡張が必要な場合があり、新しい使用例のサポートが必要な場合があります。

Recommendations

RISC-V ISA の最近の成功は、オープンソースが多くのことに対して実行可能なソリューションであることを示しています。 さらに、オープンソースは商業利用を可能にし、ビジネスモデルを成功させるために独自のソリューションを必要としません。 これらの推奨事項は、高品質でオープンで共有可能な IP の開発とサポート、およびその使用の奨励を中心としています。

Support IP development

メモリや接続などの基本的な領域向けに高品質の完全にオープンソースの IP を作成するには、多額の投資が必要です。 これらの IP は、誰でもアクセスでき、FPGA および ASIC 実装全体で動作し、以前に推奨されている参照 EDA ツール フローと互換性がある必要があります。 FPGA と ASIC の実装は異なりますが、両方とも重要です。 たとえば、FPGA 実装は、ASIC 実装の製造に入る前にアーキテクチャと設計を検証するために利用できます。 ただし、FPGA と ASIC はどちらもデザイン フローのメカニズムが異なります。 したがって、教育の強化とより良い研究アイデアの促進に役立つ、両方の分野の知財開発に対するより良いサポートが必要です。

NSF は、テクノロジーだけでなく労働力の育成にも影響を与える知財を生み出すプロジェクトに投資する必要があります。 これらのプロジェクトの成功には、ユーザー数や研究プロジェクトや出版物での使用を通じて、より広範な影響を与える要素が含まれている必要があります。

National Chip Design Center などの IP の集中ソースにより、ユーザーの成功と統合の追跡が可能になります。 これは、問題に対処するために特定の IP を利用した研究者を結び付けることで、他の人にも利益をもたらすでしょう。 中央リソースはより多くのユーザーとより迅速な導入につながり、最終的には IP の品質が向上します。 NSF は、ユーザーにとって不可欠な新しい基本的な設計問題に対処するための戦略的な「大きな課題」に資金を提供する必要があります。 これは、研究者が解決する必要がある壮大な課題を生み出すのに役立つ特定のコンテストを通じて行われる可能性があります。 これは NSF MRI 賞と似ていますが、特に半導体 IP を対象としています。

Promote maintenance and verification in addition to development

NSF は、IP の維持をデータ管理計画の重要な要素とする必要があります。 NSF の提案には、より広範な影響力と知的メリットが必要ですが、結果を広め続ける責任もあるはずです。 さらに、NSF は、研究提案によって生み出された知財の成功を維持するために、後続の資金提供のメカニズムを作成する必要があります。

科学的な厳密性を確保するために、研究プロジェクトはコミュニティによって再現可能であること、およびその再現性を継続する計画が求められるべきです。 提案には、シミュレーション、形式的手法、またはその他の方法を通じて結果が有効であることを証明するための正確性と検証に特化したセクションが必要です。 EDA ツールの変更、テクノロジーの規模の変更、その他の前提条件の変更に応じて、これらと同じ方法を使用して IP を維持できます。 従来、これにより、役に立たなくなった「古くなった」IP が生じていました。

Centralized infrastructure and distribution

IP の構築、検証、配布には体系的なメカニズムが利用可能である必要があります。 たとえば、Python には IP の配布を支援する優れたメソッド (pip install、npm など) があります。 FuseSoC [66] などのいくつかのアプローチがありますが、これは標準ではありません。 国立チップ設計センターは集中リポジトリをホストし、NSF が資金提供したプロジェクトによって生成された IP の継続的統合ポリシーを推奨する必要があります。

NSF は、重要な IP ブロックのオープンソース検証テスト スイートをサポートする必要があります。 これらの検証テスト スイートは、IP ブロック開発者による採用と、新しい IP ブロックの迅速な開発の有効化によって評価される必要があります。 さらに重要なのは、これらのブロックは多くのアーキテクチャにとって重要であるため、米国の研究者、学術機関、商業機関にとって可用性が最優先であることが重要です。

IP ブロックはリファレンス デザイン フローとの互換性を確保する必要がある

- 参照 EDA フローとの互換性/サポート

- EDA リファレンス フロー用の CI との統合

Require reproducibility of research

NSF は研究プロジェクトの再現性を要求する必要があります。 つまり、NSF には、選択された助成金が再現可能であることを保証する責任を負う委員会が必要です。 また、このグループは、特定の従業員がこれらのアイデアをどれだけうまく展開して効果的なアイデアを生み出すことができるかを確認する責任を負う必要があります。 NSF には、データが生成され、複製できるメカニズムが必要です。 再現可能により、アクセスと高品質が可能になり、開発中のものが有益であるという情報を業界に伝達するのに役立ちます。

Industry collaboration

業界のコラボレーションを促進することは、将来のイノベーションにとって重要です。 これは、オープンソース IP が科学的発見の将来にとって非常に重要であるという考えに基づいています。

研究者はアイデアを試す必要があり、このオープンソース IP は、より合理化された効率的なアーキテクチャとシステムを促進するのに役立ちます。 オープンソースは、ユーザーがさまざまなアイデアを試し、おそらく以前は解決できなかった長年の問題を解決できるようにするパズルの非常に重要なピースです。 さらに、オープンソース ハードウェアを使用すると、研究者間のコラボレーションが容易になるだけでなく、反復可能なインスタンスやインフラストラクチャを作成する可能性も高まります。 これは、将来の資金調達を可能にする持続可能性の創出を支援する計画を含めることが要件となる可能性があります。

NSF は企業と研究機関との交流促進を支援できますか? 企業が学術機関と提携して多くの人々を助けるソリューションを効果的に実現できれば、企業は学術機関との共同取り組みを促進できる可能性があります。 業界の協力は、学術機関が統合して実行できる改善のための相互作用やアイデアを促進するのにも役立つ可能性があります。 これは、業界の 1 つの部門を妨げる可能性のある科学的発見、問題、課題に対処するためのより良いアイデアにつながります。

Documentation and training

知的財産を取得し、それを効果的に使用するには、文書化とトレーニングも重要です。 多くの機関は、デザインの統合に役立つ情報にアクセスできません。 個人のトレーニングとその知的財産を効果的に使用する方法に役立つ教育的取り組みを行う。 これは、半導体とは何か、そしてそれを効果的に使用する方法についての理解を促進することで、将来米国で働く人にとって不可欠なものとなる可能性があります。

Packaging and Testing

電子パッケージングの従来の機能は、信号接続をサポートし、電力を供給し、熱を除去し、機械的および環境的脅威から組み込みチップを保護することです。 高度なパッケージングは、さまざまな材料に基づくデバイスの異種統合、最適化されたプロセッサーでの大型ダイの一連の小型ダイへのチップレット化、システム全体の帯域幅を劇的に増加させる機会など、これらを超える付加価値機能を提供します。 ハイエンドのデジタル システムでは、将来的には、複数の 2D および 3D (スタックされた) チップをモジュールに統合するためのインターポーザーの大規模な使用と、モジュール間で信号を通信するためのフォトニクスの使用に焦点が当てられる可能性があります。 スペースとコスト効率の高い統合を可能にするために、ファンアウトおよびファンインのウェーハ レベル パッケージング (FOWLP および FIWLP) を使用して構築されるシステムが増えています。 混合信号および電力供給アプリケーションは、III-V 族およびシリコンデバイス、たとえば GaN 高電圧およびパワーデバイス、または高密度 CMOS テクノロジーと統合された InP 高周波デバイスのヘテロジニアス集積から恩恵を受けることになります。 多くのアプリケーションは、非シリコン技術に基づくデバイスが CMOS ウェーハ上に製造される CMOS+X アプローチから恩恵を受けることになります。 一般的な例は、CMOS 上に抵抗膜 RAM (ReRAM) を統合して、メモリ内での不揮発性ストレージや処理を可能にするものです。

Summary of Current State

現在、パッケージング製造の 90% はアジア太平洋地域で行われています。 高度なパッケージングへの研究アクセスは存在しないか、手配するのが困難で費用がかかります。 5nm テクノロジー ノードの IC の一般的なコストは 5 億ドルを超え、その 50% は製造とパッケージングに起因します。

パッケージングの状況も急速に変化しています。 現在、インターポーザはハイエンドのパッケージングを引き継ぎ、フォトニクスはモジュール間通信における電気的相互接続を引き継ぐことになります。 異種統合は、シリコン、III-V、その他の材料セットの密接な統合により、アナログおよびパワーエレクトロニクスにパラダイムシフトを引き起こします。 ファンアウト ウェーハ レベル処理 (FOWLP) およびファンイン ウェーハ レベル (FIWLP) の最近のプロセス技術では、IC の設計とパッケージングを同時に実行する必要があります。 ただし、インターポーザーは、Xfab、SkyWater、nHanced Semiconductors によって提供されるようなレガシー テクノロジを使用して構築できます。 後者の 2 つは、バンピング、ハイブリッド ボンディングなどのさまざまな統合テクノロジもサポートしています。

IC 設計とパッケージングの共同設計概念には、エンジニアのための設計支援が必要です。 IC 設計の場合、ファウンドリが提供する PDK は、エンジニアが IC 設計を完了するために使用するツールです。 パッケージングには、アセンブリ デザイン キット (ADK) と呼ばれる同等のものが必要です。ADK は PDK と並行しています。 ADK には、EDA と Outsourced Semiconductor Assembly and Test (OSAT) 機能の組み合わせが含まれています。

CISE コミュニティではパッケージングのコースを提供している大学はほんの一握りです。 調整されたコース順序を提供するところはまだ少ないです。 VLSI コースには、パッケージングや関連開発に関する資料が含まれているものはほとんどありません。 高等教育機関には、パッケージング、特に IC をテストできるパッケージの設計に関する体系的なカリキュラムがありません。

大学の研究プロジェクトで製造されるチップのカスタム パッケージングは、特に現代の商用品質のパッケージの場合、調達が困難であることがよくあります。 大学では既製のパッケージやチップオンボード統合を使用するのが一般的です。

教育現場で製造されたチップのテストは、専用のテスト ボードと PC ベースの機器を使用して管理できますが、それはその場限りの方法で行われ、各グループが同様のインフラストラクチャを再現します。 対照的に、研究環境で製造されたチップのテストとデバッグには、プローブ システム、ロジック アナライザなどの多大な機器サポートが必要です。より高度なテクノロジでは、これらの高密度 IC をテストするための精巧な研究室が必要です。 すべての大学がこれらの機能を備えているわけではなく、下位層の学校では問題がより顕著になります。

Key Challenges

University access to advanced packaging

現在、大学が高度なパッケージング技術を利用できるのは非常に限られています。 その結果、陪審員による組み立てのアプローチがよく使用されます。 たとえば、多くのプロジェクトは次のようにパッケージ化されています。

チップを既存の既製パッケージまたはプリント基板にワイヤボンディングし、マイクロプローブを使用して高速信号を導入または測定します。 (ワイヤボンドは高周波信号をサポートしません。)回路機能を検証するには十分ですが、システム設計と共同最適化における博士課程の学生のトレーニングにはほとんど役に立ちません。 大学の研究者が高度なパッケージングを使用したい場合は、研究開発用のロットを構築する意欲のある非常に限られた範囲のベンダーから独自の製造フローを組織する必要があります。 たとえば、大学の研究者は、MPW ウェーハをトップメタルまでのみ処理し、CMOS+X またはヘテロジニアス統合ステップを組み込むためにウェーハを専門ファブに転用するようにファウンドリを手配するかもしれません。 これには費用がかかり、時間もかかります。 より良い解決策が必要です。

Lack of US based packaging industry

パッケージ製造の 90% はアジア太平洋地域で行われています。 業界のオンショアリングの機会を創出するには、人材と技術知識が必要です。 パッケージ化されたコースのセットを提供する大学はほとんどありません。 マイクロエレクトロニクスのコースには、高度なパッケージングに関するモジュールが含まれているものはほとんどありません。

Chip/package co-design

パッケージングと埋め込みチップの最適な共同設計は、サイズ、重量、性能、電力、コストを改善する大きな機会をもたらします。 IC 設計とパッケージングを同時に実行するという共同設計の概念には、エンジニアのための設計支援が必要です。 IC 設計の場合、ファウンドリが提供する PDK は、エンジニアが IC 設計を完了するために使用するツールです。 アセンブリ デザイン キット (ADK) と呼ばれる、パッケージングに同等に必要なもの。 ADK は PDK と並列します。

これらには、EDA と Outsourced Semiconductor Assembly and Test (OSAT) 機能の組み合わせが含まれています。 PDK/ADK の共同設計により、製造/パッケージのコストを少なくとも 75% 削減できます。

Many universities lack facilities to test research chip

大学のプロジェクトが研究目的で作られたものであるか教育目的で作られたものであるかを検証するには、テストが必要です。 クラステープアウトのテストは、事前設計されたボードとともにチップ上にテストインターフェイスを組み込み、PC ベースのテスト機器を使用することによって容易に行うことができます。 ただし、研究システムのテストはより複雑で、高度なテスト機器 (プローブ ステーション、顕微鏡など) へのアクセスとそれを使用するノウハウが必要です。 多くの大学にはそのようなアクセスがありません。

Recommendations

NSF should establish a Call for Packaging Research Infrastructure

NSF は半導体パッケージング研究インフラストラクチャ プログラムを確立するか、より広範なプログラムに含めるべきである。 これにより、プロトタイピングを可能にする適切な範囲の高度なパッケージングおよび統合テクノロジーへの組織的かつ体系的なアクセスが提供されるはずです。 この呼びかけは、ADK の最適なコンテンツと、ADK、PDK、EDA ツール間の相互設計の共同設計を理解するための研究活動を促進するはずです。 最終的には、オープンソース ADK が利用可能になり、プロプライエタリ ツールとオープンソース ツールの両方の推奨フローがこれらの ADK をサポートする必要があります。

NSF should establish a Call for Chip/Package codesign and design with Heterogeneous Integration technologies

NSF は、CMOS+X、高度なパッケージング、および異種統合テクノロジから生じる機会を探ることに特化したプログラムを確立する必要があります。 このプログラムは、上記のプログラムで実装されているインフラストラクチャを活用し、設計技術協調最適化 (DTCO)、チップ パッケージのプロジェクトを奨励する必要があります。

ツールとフローの共同設計、最適な異種統合、およびケーススタディの設計、製造、テスト。 インターポーザー上のチップレットへのパッケージングは、インターフェイスに関するユニークな研究の機会を提供します。何らかの標準に向けて活動するコミュニティを確立する必要があります。

NSF should establish a Call for Shared Test Infrastructure

国立チップ設計センター (NCDC) (または特定の大学の地域研究室) は、サポートとトレーニングとともにテスト機器とインフラストラクチャを提供する必要があります。 個々の学校がこの機器を保有することは意味がないかもしれませんが、研究者や学生がその機器にアクセスするために旅行することは理にかなっています。 この呼びかけでは、テスト用の半導体計装機器を共有できる利害関係者のコミュニティ(たとえば、全国的または地域的)を確立する必要があります。 大学がこれらの試験施設を設立するための設備投資や、他の研究者にメンテナンスやサポートを提供するための継続的な支援が必要です。 これらの施設は、最小限の料金または無料ですぐに利用できる必要があります。 また、コミュニティは、IO インターフェイス、設計などを含むテストを支援するために、主要な IP の共有を実施することを奨励する必要があります。

Conclusions

このワークショップのレポートでは、参加者によって特定された最も重要な分野、つまりテクノロジー ノード、トレーニングと教育、電子設計自動化 (EDA) ツール フロー、知的財産 (IP)、およびパッケージングとテストにおける主な課題と推奨事項が提示されました。 参加者全員は、各分野に早急な対応が必要な深刻な課題があることに同意しました。 最も普及している 2 つのソリューションは、両方を採用しているようです。

オープンソースおよび独自のサポート対象 IP、設計キット、ツール フロー、およびこれを調整するための国家計画。 他の地域と同様の国立チップ設計センター (NCDC) の設立は、米国の広範な VLSI 設計コミュニティを創設、維持し、アクセスを提供する最も効果的な方法です。