目的

- AXIを理解する

- AXIを説明できるようになる

- AXIを用いて設計できるようになる

対象

FPGAを勉強し始めた初心者の方

目次

-

AXIの概要

- AXIとは

- AXI4の3つの仕様

- AXIを理解するコツ

- AXI4の基本プロトコル

- AXI4-Stream

-

AXI4-Lite

- AXI4-Liteを理解する

-

AXI4

- AXI4を理解する

AXIの概要

AXIとは

AXI(Advanced eXtensible Interface)は、主にシステムオンチップ(SoC)設計で使用される高性能な通信インターフェースです。ARM社が開発したAMBA(Advanced Microcontroller Bus Architecture)仕様の一部として誕生し、初期のAXI(AXI3)は2003年に導入され、その後2010年にAXI4へと進化しました。

AXI4の仕様は、ARMウェブサイトから入手できます。

AXI4の3つの仕様

- AXI4 : アドレスを使って、バースト機能も備え、マスターからスレーブへデータを送るフルスペックなプロトコル

- AXI4_Lite : アドレスを使って、マスターからスレーブへデータを送る低速だが軽量なプロトコル

- AXI4_Stream :アドレスを使わず、マスターからスレーブへデータを送る高速かつ軽量なプロトコル

| 特徴 | AXI4 | AXI4-Lite | AXI4-Stream | 説明 |

|---|---|---|---|---|

| バースト転送 | 〇 | × | × | 複数のデータを一度に連続して転送できる機能 |

| 独立した読み取り/書き込み | 〇 | 〇 | × | 読み取りと書き込みが別々のチャンネルで同時に行える機能 |

| データストリーム転送 | × | × | 〇 | 連続したデータ(例えばビデオや音声)を効率よく転送できる機能 |

| アドレスフェーズ | 〇 | 〇 | × | データ転送前に転送先のアドレスを指定する手順 |

| データフェーズ | 〇 | 〇 | 〇 | 実際にデータを転送する手順 |

| フロー制御 | 〇 | 〇 | 〇 | データの送受信のタイミングを調整してデータの衝突を防ぐ機能 |

| 主な用途 | 高性能データ転送 | シンプルな制御レジスタ | 連続データストリーム | どのような用途に適しているか |

| 設計の難易度 | 難 | 中 | 易 | 実装や設計の難易度 |

AXIを理解するためのコツ

AXI(Advanced eXtensible Interface)を理解するためには、以下の2つのポイントを押さえることが重要です:

- マスターとスレーブの役割を理解する

- 信号の意味を理解する

1. マスターとスレーブの役割を理解する

AXIインターフェースでは、デバイス間の通信を行うために「マスター」と「スレーブ」が存在します。

マスター(Master):

- 役割:データ転送の主導権を持ち、読み取りや書き込みの要求を行うデバイスです。

- 例:CPU、DMAコントローラなど。

スレーブ(Slave):

- 役割:マスターからの要求に応じてデータを提供したり、受け取ったりするデバイスです。

- 例:メモリ、ペリフェラル(周辺機器)など。

マスターとスレーブの関係を理解することで、どのデバイスがどのような役割を果たしているか、どのように通信が行われているかを把握しやすくなります。

2. 信号の意味を理解する

AXIインターフェースでは、多くの信号が使用されますが、以下の主要な信号を理解することが重要です。

読み取りチャンネル(Read Channel)

-

AR (Address Read):

- araddr:読み取りアドレス。

- arvalid:読み取りアドレスが有効であることを示す。

- arready:スレーブが読み取りアドレスを受け取れる状態であることを示す。

-

R (Read Data):

- rdata:読み取りデータ。

- rvalid:読み取りデータが有効であることを示す。

- rready:マスターが読み取りデータを受け取れる状態であることを示す。

書き込みチャンネル(Write Channel)

-

AW (Address Write):

- awaddr:書き込みアドレス。

- awvalid:書き込みアドレスが有効であることを示す。

- awready:スレーブが書き込みアドレスを受け取れる状態であることを示す。

-

W (Write Data):

- wdata:書き込みデータ。

- wvalid:書き込みデータが有効であることを示す。

- wready:スレーブが書き込みデータを受け取れる状態であることを示す。

-

B (Write Response):

- bresp:書き込み応答(成功、エラーなど)。

- bvalid:書き込み応答が有効であることを示す。

- bready:マスターが書き込み応答を受け取れる状態であることを示す。

AXI4の基本プロトコル(ハンドシェイク)

AXI4プロトコルには、データ転送のタイミングに基づいて3つのパターンがあります。それぞれのパターンについて説明します。

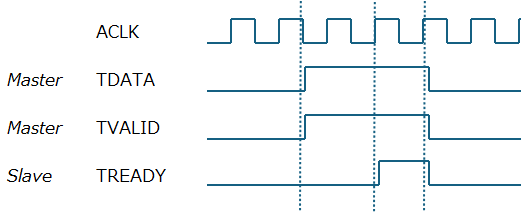

1. Valid先行型

説明

このパターンでは、マスターが先にTVALID信号をアサートし、その後スレーブがTREADY信号をアサートすることでデータ転送が行われます。

特徴

- マスターがデータを準備できたことを示すために、

TVALIDを先にアサートします。 - スレーブがデータを受け取る準備ができると、

TREADYをアサートします。 - 両方の信号がアサートされた時点でデータ転送が行われます。

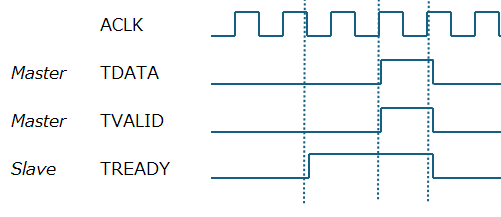

2. Ready先行型

説明

このパターンでは、スレーブが先にTREADY信号をアサートし、その後マスターがTVALID信号をアサートすることでデータ転送が行われます。

特徴

- スレーブがデータを受け取る準備ができたことを示すために、

TREADYを先にアサートします。 - マスターがデータを準備できると、

TVALIDをアサートします。 - 両方の信号がアサートされた時点でデータ転送が行われます。

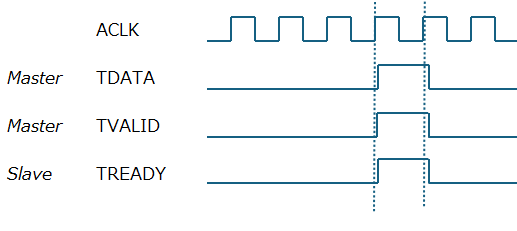

3. Valid/Ready同時型

説明

このパターンでは、マスターとスレーブが同時にTVALIDおよびTREADY信号をアサートし、データ転送が行われます。

特徴

- マスターとスレーブが同時にデータの送受信の準備ができている場合に用いられます。

- 両方の信号が同時にアサートされることで、効率的なデータ転送が可能となります。

まとめ

AXIインターフェースを理解するためのコツは以下の通りです:

- マスターとスレーブの役割を理解する:どのデバイスがデータ転送を主導し、どのデバイスがそれに応答するのかを把握する。

- 信号の意味を理解する:各信号の役割とその流れを理解することで、AXIバスの動作を把握する。

これらのポイントを押さえることで、AXIインターフェースの仕組みをより深く理解できるようになります。