この記事はまだ執筆中の為不完全な箇所があります

この記事では、A3921の使い方を書いていこうと思います。

この記事は初心者が勉強用に作ったので、データシートの読み方を丁寧に書いてあるだけの記事です!今見返したら恥ずかしい[追記2024/09/12]

#目次

#1.はじめに

この記事は回路初心者が備忘録とMarkdown記法の練習を兼ねて書いています。

そのため間違ったことを書いている可能性が十分あるので、間違いを見つけたら@TakenMakerにDMするかこの記事にコメントしてください。あと高専1年の頃国語赤点すれすれ取ったことがあるような奴なので文章変かもしれません

検索してもA3921についての解説は出てこなくて自分も困ってたので役に立つかもしれないです。

#2.A3921とは?

上記の画像のようなフルブリッジゲートドライバICです。

このゲートドライバの特徴として

- チャージポンプがついているためDuty比を100[%]に設定できる

- 保護回路が充実している

- 秋月電子電商に売っている

といったことが挙げられます。

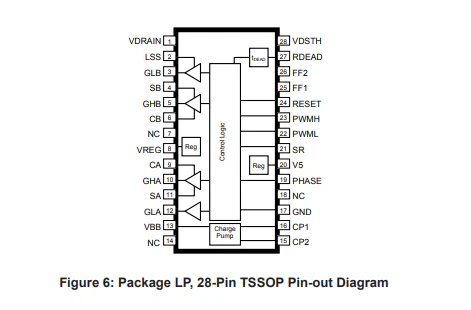

#3.ピン配置

ピン配置は上の画像のようになっています。各ピンの細かい説明はデータシートの8ページから13ページに書いてあります。

- VDRAIN

- このピンはハイサイドのドレインと直接接続します。このピンについて以下のような記述があります。

This is a low current sense input from the top of the external FET

bridge. This input allows accurate measurement of the voltage at

the drain of the high-side FETs.この記述から、VDRAINに入る電流を検出することでハイサイドのFETのドレインにかかる電圧を正確に測定していることがわかります。なぜこの電圧を測定しているかはVDSTHのところに詳しく書きますが、外付けFETの故障の判定にFETのドレイン-ソース間電圧VDSの値が必要だかららしいです。また、VDRAINピンに入力される電流はVDSTH端子に印加される電圧に比例し、次式の関係が成り立ちます。

$I_{VDRAIN}$の単位を$[\mu A]$,$V_{DSTH}$の単位を$[V]$とするとI_{VDRAIN}=72\times V_{DSTH} +52 - LSS

-

このピンについては以下の記述があります。

>This is the low-side return path for discharge of the capacitance on the FET gates. It should be tied directly to the common sources of the low-side external FETs through an independent low impedance connection.

この記述から、ローサイドのFETをオフにする際にローサイドのFETの入力容量$C_{iss}$を放電するのに用いられるピンだということがわかります。したがって、ローサイドのFETのソースに直接接続します。

- GLX

- まず初めにGLXはGLA,GLBピンのことを指します。データシートによく見られるので読む際は気を付けてください。(~~自分はこれが何か分からず1時間くらい悩みました~~)

ローサイドのFETのゲートへの出力をするピンです。したがって、ローサイドのFETのゲートに直接繋げます。

また、スイッチング時間の調整のためにゲートドライバとFETのゲートの間に任意でゲート抵抗をつけます。

ゲート抵抗については[なかどんさんの記事](https://qiita.com/donburikun_/items/36c873690bb6eae11026)がわかりやすいと思います。 - SX

-

これもSA,SBピンのことを指しています。

>Directly connected to the motor, these terminals sense the voltages switched across the load. These terminals are also connected to the negative side of the bootstrap capacitors and are the negative supply connections for the floating high-side drives.

この記述から、このピンはモーターにかかる電圧を検出するピンだということがわかります。したがって、モーターに直接接続します。また、このときこのピンはハイサイドのFETのソースと接続されているため、ブートストラップコンデンサのマイナス側とも接続をします。さらに、このピンはハイサイドのプッシュプル回路のマイナス側と接続されているので、ハイサイドのFETの入力容量$C_{iss}$の放電電流が流れます。そのため、低インピーダンスでモーターと接続する必要があります。

- GHX

- GLXがローサイドのFETのゲートへの出力ピンだったのに対して、GHXはハイサイドのFETのゲートへ出力するピンです。

したがって、ハイサイドのFETのゲートに直接繋げます。

GHXピンもGLXピンと同じように任意でゲート抵抗をつけます。 - CX

- ブートストラップコンデンサのプラス側と繋げるピンです。

ハイサイドのFETがオフの時、約VREGまで充電されます(VREGについては後程説明します) - NC

- No connectionの略です。そのため何も接続しません。(そのはずですがほかの人の回路を見てたらここをVREGと繋いでいる人がいました。なので少し心配です・・・)

- VREG

- 内部で約13[V]まで昇圧して出力しているピンです。

パスコンのほかに過渡電流を供給するためのコンデンサを接続する必要があります。

詳しくは[7.その他](#7その他)で説明します。 - VBB

- バッテリーと直接接続して電圧を供給します。

>A low-cost diode can be placed in the connection to VBB to provide reverse battery protection. In reverse battery conditions, it is possible to use the body diodes of the power FETs to clamp the reverse voltage to approximately 4 V. In

this case, the additional diode in the VBB connection will prevent damage to the A3921 and the VDRAIN input will survive the reverse voltage.

とあるので、バッテリーとVBBピンの間にダイオードをつけることで、逆電圧保護が可能だとわかります。

- CPX

- チャージポンプコンデンサを接続するピンです。

CXがそれぞれのピンに対してコンデンサを接続するのに対して、CPXはCP1とCP2の間にコンデンサを接続します。 - GND

- 説明するまでもないですがGNDと接続します。

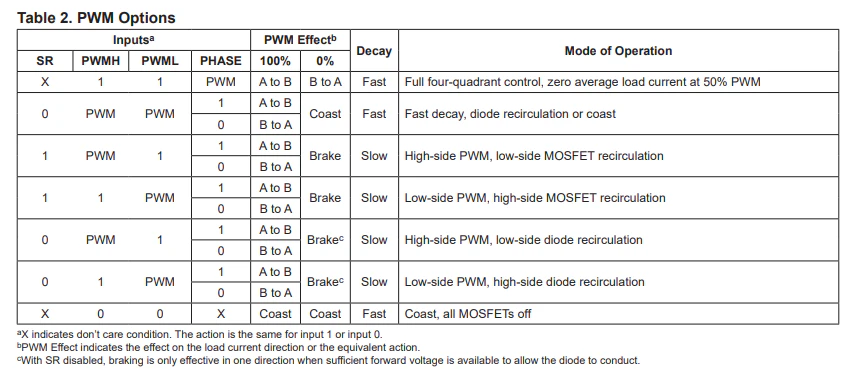

- PHASE,SR,PWMX

- これらのピンへの入力の状態によってHブリッジのどのFETがオンになるかが決まります。真理値表は以下のようになっています。

ここからは、SM方式のDCモータドライバを設計する場合について解説します。

SM方式で駆動させる場合の各ピンへの入力の表は、上記の真理値表から次のようになります。PWMH PWML PHASE SR 動作 1 1 1 $\phi$ 正回転 1 1 0 $\phi$ 負回転 0 1 $\phi$ 1 ブレーキ したがって、表から - SRとPWMLは常時1

- PWMHにPWM入力を流す

- PHASEに回転方向の制御信号を流す

といったことをすると、SM方式で駆動するモータドライバを設計することができます。

実際には、このように考えなくても次の表からしたい動作を実現させるための入力を選択することができます。

また、LAP方式にも対応させたい場合はPWMHとPWMLをジャンパーピン等で短絡させてPHASEにPWM信号を流せば実現させることができます。

余談ですがLAP方式、SM方式、ASM方式の中で一番効率がいいのはSM方式らしいです。 - V5

- 5[V]を出力するピンです。

>The power supply connections should be decoupled with a ceramic capacitor, typically 100 nF, between the supply pin and ground.

とあるので、100[nF]のパスコンをつける必要があります。

- RESET

- このピンをlowにするとすべての内部回路やレギュレーターが動作しないスリープモードになります。スリープモード中はVBBからの消費電流は最小レベルになり、もし保護回路が何らかの異常を検知していた場合、その状態がクリアされます。また、RESETをリセットパルス時間tRESよりも短い時間lowにすることでスリープモードに入らずに異常を検知している状態をクリアにすることもできます。

動作させるときに毎回RESETをhighにするのは~~めんどくさい~~ので、通常は20~33[kΩ]の抵抗でプルアップして使います。 - FFX

- このピンはA3921が故障を検知したときにHIGHになって故障の状態を知らせてくれます。

[オープンドレイン出力](https://forum.digikey.com/t/topic/5696)のピンなので抵抗をつける必要があります。

各出力の意味は次の表で知ることができます。  また、2つ以上の故障が同時に検知された場合は、それぞれの故障の出力の論理和が出力されるようです。

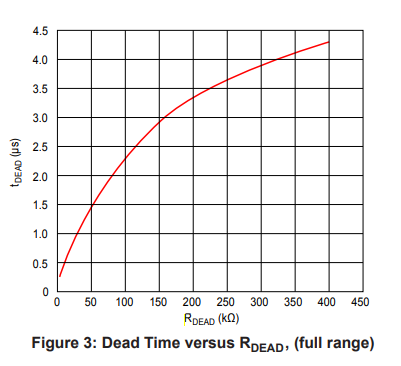

Fault Descriptionの具体的な説明については、一つ一つ説明すると気が狂うのと故障したとき以外見ないと思うので省略します。データシートのp12~p13に書いてあります。 - RDEAD

- A3921のデッドタイムはこのピンに接続する抵抗によって決まります。

3[kΩ]以上の抵抗をRDEAD-GND間に接続したときのデッドタイムは次のような関係になります。  また、このピンをV5と直接つなぐと、最大デッドタイムである$6[\mu s]$に設定されます。

しかし、この図では正確に生成されるデッドタイムを知ることはできません。

正確に求める場合は次のような近似式を使います。\begin{equation} t_{DEAD}(nom)=50+\frac{7200}{1.2+(\frac{200}{R_{DEAD}})}\\ \end{equation} (ここで、R_{DEAD}は[k\Omega ],t_{DEAD}(nom)は[ns]単位)この式は$6[k\Omega ]< R_{DEAD}< 60[k\Omega ]$の時に最も高い精度が得られます。

また、$R_{DEAD}$に流れる電流は次の式で推定することができます。I_{DEAD}=\frac{1.2}{R_{DEAD}}$I_{DEAD}$についての式はデータシートに単位の指定がされていませんでしたが、SI単位系でいいと思います。

- VDSTH

- VDRAINピンとSXピンを用いて測定したそれぞれのハイサイドのFETの電圧$V_{DS}$がこのピンに入力されている電圧を上回ると、A3921は短絡していると認識します。なぜ$V_{DS}$の値で短絡を判断できるかというと、正常に動作しているとき(ハイサイドとローサイドのFETが同時にONになっていないとき)はFETのオン抵抗が非常に小さいためほとんどモータで電圧降下され$V_{DS}$が非常に小さくなるのに対して、短絡しているときはモータを経由せずにGNDと接続されるため非常に大きい貫通電流が流れて$V_{DS}$の値が大きくなるからです。

また、V5に接続するか、VDSDISよりも高い電圧をこのピンに印加すると、この短絡検出機能を無効にすることができます。

- Load Supply Voltage(不確実)

- バッテリーによって供給する負荷電圧です。バッテリーの電圧が-0.3[V]から50[V]の範囲内のものを使用しなければいけません。

- Logic Inputs and Outputs

- PWM入力等の電圧です。-0.3[V]から6.5[V]以内となっているのでArduino,mbed両方に対応しています。

- V5 Pin

- V5ピンの絶対最大定格です。(この下のCA and CB Pinsまではこれと同じような感じなので省略します)

GHA and GHB PinsのRatingのところにSx to Sx+15とありますが、このSxはSAとSBピンのことです。

- Operating Temperature Range

- 動作温度範囲のことです。-40℃になることはシベリア在住の方じゃない限りないと思いますけど、150℃以上には普通になりそうなので熱設計に気を付ける必要がありそうです。

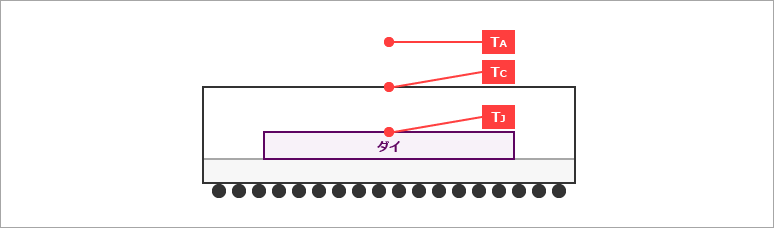

- Junction Temperature

- ジャンクション温度範囲のことです。ここで気を付けたいのが、ジャンクション温度と周囲温度はまったくの別物だということです。

周囲温度(Ta),ケース温度(Tc),ジャンクション温度(Tj)の関係は上の図のようになります。

つまり、ジャンクション温度はケース内部にある回路自体の温度ということになります。詳しくは[ここ](https://www.macnica.co.jp/business/semiconductor/articles/intel/121897/)を見てみてください。 - Transient Junction Temperature

- 1[s]を超えない時間なら、ジャンクション温度が175[℃]までになっても大丈夫らしいです。その横の説明文にある"lifetime duration not exceeding 10hr"という文章がよくわからないので後で調べます

- Storage Temperature Range

- A3921を動作させていない状態において、A3921を安全に保存または輸送できる周囲温度の範囲のことらしいです。詳しくは[ここ](https://detail-infomation.com/diode-absolute-maximum-rating-temperature/)を見てみてください。

#5.熱特性

熱設計でヒートシンクが必要かどうかを調べる場合に、ここに書いてある値から温度が最大絶対定格の温度以下かを計算することで判断することができます。

- $R_{ΘJA}$

- ケース内部の回路(ダイ)と外気の間の熱抵抗です。JEDEC規格と呼ばれる規格に基づいた4層プリント基板なら28[℃/W],(片面に3.8インチの銅面積を持つ)2層プリント基板なら32[℃/W]となります。

- $R_{ΘJP}$

- ケース内部の回路(ダイ)とパッケージ(ケース)の間の熱抵抗です。

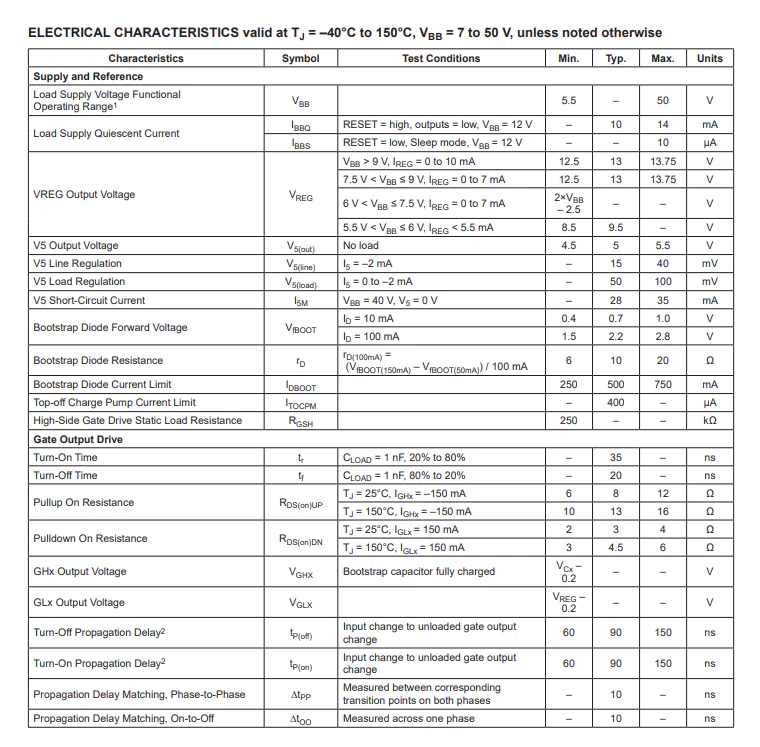

#6.電気的特性

特に断りのない場合、ジャンクション温度が-40[℃]~150[℃],VBBが7[V]~50[V]の範囲の時の値です。

思ったよりも項目が多いのでわかりにくいところ以外は説明を省略します。

- Load Supply Voltage Functional Operating Range

- VBBピンにバッテリーによって印加する電圧の範囲です。ただし、(一般的な)限界値である7[V]以下では電気的特性の表の値が保証されないらしいので、7[V]~50[V]の範囲の電圧を印加したほうがいいと思います。

- Load Supply Quiescent Current

- A3921が静止しているときの消費電流です。静止しているといっても出力がlowなだけなときとRESETピンがlowでスリープモードに入っているときの2種類あり、前者の場合は$I_{BBQ}$,後者の場合は$I_{BBS}$に書かれています。

- VREG Output Voltage

- VREGに出力される電圧です。$V_{BB}$の値などによって変わります。

- V5 Output Regulation

- V5に出力される電圧です。

- V5 Line Regulation

- $V_{BB}$が変動したときのV5の変動値です。(不確実)

- V5 Load Regulation

- V5で消費される電流$I_5$が0[mA]から2[mA]になったときのV5の変動値です。

- V5 Short-Circuit Current

- V5が短絡したときに流れる電流です。

- Bootstrap Diode Forward Voltage

- $I_d$が書かれている値の時にブートストラップダイオードに印加される電圧の値です。

- Bootstrap Diode Resistance

- ブートストラップダイオードの抵抗値です。

- Bootstrap Diode Current Limit

- ブートストラップダイオードの流せる最大の電流値です。

- Top-off Charge Pump Current Limit

- チャージポンプの流せる最大の電流値です。

- High-Side Gate Drive Static Load Resistance

- 不明(To do)

- Turn-On Time,Turn-Off Time

- Turn-On Timeは$V_{gs}$を与えて$V_{ds}$が20%から80%まで上昇するまでの時間です。Turn-Off Timeはその逆で$V_{ds}$が80%から20%まで下降するまでの時間です。

- Pullup On Resistance,Pulldown On Resistance

- プッシュプル回路の出力インピーダンスです。この値が小さいほど瞬間的にゲートに流す電流が大きくなり、FETをスイッチングできるスピードや周波数が速くなります。

- GHx Output Voltage,GLx Output Voltage

- それぞれGHxピン,GLxピンがhighの時に出力される電圧の値です。GHxピンはブートストラップ回路が内部で組まれているのでブートストラップコンデンサで充電される電圧と$V_{REG}$の和が出力されます。

- Turn-Off Propagation Delay,Turn-On Propagation Delay,Dead Time

- それぞれの意味は次のタイムチャートで示されています。 SM方式なら一番左上、真ん中の左側、LAP方式なら一番左下のタイムチャートとそれぞれ対応しています。

- Propagation Delay Matching, Phase-to-Phase

- To do

- Propagation Delay Matching, On-to-Off

- To do

- FF1 and FF2 Fault Output (Open Drain)

- 故障フラグが出されていない(OFFになっている)時のFFXピンの電圧です。

- FF1 and FF2 Fault Output Leakage Current

- 故障フラグが出されている(ONになっている)時に内部のNch FETに漏れ出る電流の値です。

- Input Low Voltage

- lowにするための電圧です。0.8[V]未満にしないとlowとして認識されません。

- Input High Voltage

- HIGHにするために必要な電圧です。2.0[V]以上でHIGHになります。

- Input Hysteresis (Except RESET Pin)

- リセットピンを除いた入力ヒステリシスの値です。入力ヒステリシスについては[こちら](https://analogista.jp/comparator-basic/)を参考にしてください。

- Input Hysteresis (RESET Pin)

- リセットピンの入力ヒステリシスの値です。

- Input Current (Except RESET Pin)

- リセットピン以外の入力電流です。入力電流については[こちら](https://toshiba.semicon-storage.com/jp/semiconductor/knowledge/e-learning/cmos-logic-basics/chap4/chap4-2-3.html)を参考にしてください。

- Input Pulldown Resistor (RESET Pin)

- 内部にあるRESETピンのプルダウン抵抗の抵抗値です。

- RESET Pulse Time

- RESETピンが$t_{RES}$よりも長い時間lowになるとスリープモードに入ります。スリープモードに入らずに故障フラグをクリアにするためにはこの時間よりも短い時間lowにしなければいけません。 Protectionについては重要なところ以外省略します

- VDSTH Input Range

- VDSTHピンに入力できる電圧の範囲です。

- Overtemperature Fault Flag Threshold

- 150[℃]を超えると検知して故障フラグを出すらしいです。温度検知もしてくれるんですね。

ブートストラップコンデンサの容量が大きすぎると充電に時間がかかるためPWM周波数や最大デューティーサイクルが制限されることになり、また逆に容量が小さすぎるとFETの入力容量を充電するときに大きな電圧降下が発生するため、適切なブートストラップコンデンサを選定する必要があります。電圧降下を小さくするためには、ブートストラップコンデンサの電荷量$Q_{BOOT}$の値をFETのゲート入力電荷量$Q_g$よりも十分大きくする必要があります。

$Q_{BOOT}$の値は、$Q_{BOOT}$の値が$Q_g$の値の$n$倍であるとすると、次式で表されます。

Q_{BOOT}=C_{BOOT} \times V_{BOOT}=Q_{GATE} \times n

\\したがって\hspace{400pt}\\

C_{BOOT}=\frac{Q_{GATE} \times n}{V_{BOOT}}

ここで、$V_{BOOT}$はブートストラップコンデンサにかかる電圧です。また、FETが動作している時のブートストラップコンデンサの電圧降下は次式で近似されるとデータシートに書いてあります。

\Delta V \approx \frac{Q_{GATE}}{C_{BOOT}}

したがって、$n=20$としておけば$\Delta V$は$V_{BOOT}$の約5[%]になります。

また、通常の動作条件下では$V_{BOOT}$の最大値は$V_{REG}$の最大値と等しいらしいです。

- ブートストラップコンデンサの充電時間

ブートストラップコンデンサの充電に必要な時間$t_{CHARGE}[\mu s]$は$C_{BOOT}[nF]$の値を用いて次式で求められます。

t_{CHARGE}=\frac{C_{BOOT} \times \Delta V}{100}

$\Delta V$は通常、FETの入力容量を充電するときに低下する電圧の量であり$400[mV]$以下です。ただし、電源投入時などブートストラップコンデンサが完全に放電されていた場合、$\Delta V$は$12[V]$とみなすことができます。

-

$V_{REG}$に接続するコンデンサの選定

$V_{REG}$はローサイドのFETのゲートへの電流とブートストラップ用充電電流を供給するのに使われています。ローサイドのFETをONにした時の過渡電流は$V_{REG}$では直接供給することができないので、$V_{REG}$に外付けのコンデンサを接続して供給してやる必要があります。最悪の場合、ローサイドのFETのONにした後すぐにブートストラップコンデンサを充電する必要があるのでこのコンデンサの値はローサイドのFETをONにしたときの電圧降下とブートストラップコンデンサの再充電をしたときの電圧降下の和が十分小さくなる値である必要があります。データシートには$20 \times C_{BOOT}$が適切な値だと書いてあります。また、$V_{REG}$と$GND$間に接続するコンデンサなのでこのコンデンサにかかる最大の電圧は$V_{REG}$です。 -

パスコンをつける

V5ピン,VREG,VBBピンにはそれぞれ100[nF]のパスコンをつける必要があります。(上の説明でいったかもしれません...)

-消費電力

熱設計をする際に必要になるのが、A3921によって消費される電力$P_D$です。$P_D$は次式で計算することができます。

P_D=P_{BIAS}+P_{CPUMP}+P_{SWITCHING}

ここで、

\begin{eqnarray}

P_{BIAS} &=& V_{BB} \times I_{BB}\\

P_{CPUMP} &=& \bigl((2 \times V_{BB})-V_{REG}) \times I_{AV},V_{BB}<15[V]のとき\\

&または&\\

&=& (V_{BB}-V_{REG}) \times I_{AV},V_{BB} \ge 15[V]のとき\\

P_{SWICHING}&=&Q_{GATE} \times V_{REG} \times N \times f_{PWM} \times R_{atio}

\end{eqnarray}

であり、また上の式で

\begin{eqnarray}

I_{AV}&=&Q_{GATE} \times N \times f_{PWM}\\

R_{atio}&=&\frac{10}{R_{GATE}+10}

\end{eqnarray}

です。また、$N$はPWM1周期でスイッチングされるFETの数です。

従って、ASM方式なら$N=1$,SM方式なら$N=2$,LAP方式なら$N=4$となります。

#8.終わりに

自分が作ったA3921のEagleのライブラリを貼っておきます。(これも何か間違いがあればDMよろしくお願いします...)

まだまだ全然わからないことばっかりありますが、設計していく中でわかったらまた追記していきます。