目的

Tang-Nano-4Kに機器追加追加無しで、データのやり取りをやりたい。

USBシリアルを使えば通信は出来るんだけど、USBシリアル邪魔だものね。

USBでJTAGが繋がってるから、通信できる可能性は有るのだけど。

誰かがやってくれるかもしれないが、待ってるだけも何だし。

◆◆◆ よし、出来る範囲で頑張ってみるか ◆◆◆

うーん、資料がないゾ。

経緯

Tang-Nano-4Kに、別途USBシリアルを繋げば通信できるのは当たり前。

でもケーブルの結線は邪魔だし、接続を何時迄覚えて居られるかな。

そもそもは、JTAGのシリアル端子がFPGAに繋がって居れば問題無かった話だが。

※多分、端子が足りなかったのだろう。

其れなら、JTAGやってるBL702の通信モードを変えればと思ったが...。

※BL702はFTDI所生のFTD2XX.dllからのコマンドは受け付ける謎仕様。

※FTDIの真似っこしているようだが、大部分のコマンドは無視されてる様子。

謎の壁は厚かったが、突破口として通信可能な条件を見出した、

謎は解けた、と言っても判ったのはごく一部だとは思うけど。

開発環境

Tang-Nano-4K 効率よくデバッグするなら2個必要。(何処かで買って)

GOWIN EDA Education版 verilogのコンパイルに必要。(GOWINに登録して落して)

ARMコンパイラ Cortex-M3のプログラムコンパイルに必要。( 〃 )

謎とき(JTAGのコマンド解析)

JTAG通信を司っているBL702へ書き込まれているプログラムの資料は見つからなかった。

※メーカーに公開の義務も無いけど、コマンド位公開してほしいものだ。

「FTDIのsampleプログラム」でアクセスするとレスポンスが帰ってきた。

この結果より、FT_Open,FT_Close,FT_Write,FT_Readは動作する模様。

その他のコマンドは、送っても動作しているかどうか良く判らなかった。

送信している波形をAnalyzer Oscilloscopeで表示させ、解析回路を作成。

同様な波形を送信する事により、LoopBack(FTDIのsampleソフト)での通信に成功。

※クロックに同期した送信波形。SPI信号、のような。

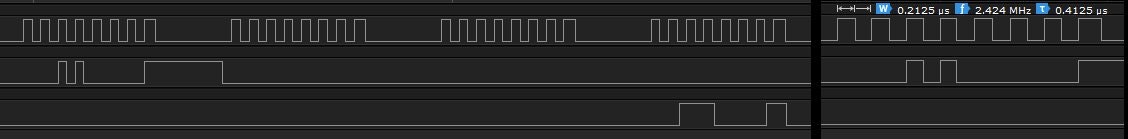

送受信波形を下記に示す。左図では1(0x31)を送信、上からTCK,TDI,TDO、

TCKに同期してTDIにデータ送信、暫くして受信データ(エコー)がTDOに表れてる。

右図は左波形の拡大、約2.5MHzで通信している事を示す。

ここで問題発生、プログラムを弄ったら通信できなくなった。

変更点を比較すると、動作正常と動作異常のソフトではテスト用の送信データを変えていた。

正常 送信データ "0123456789"

異常 送信データ 0x11,0x22,0x33,0x44,0x55,0x66,0x77,0x88,0x99

この結果と、正常時も初回は"0123"が送られずに、"456789"のみ送信されている事より、"0123"はコマンドとして処理されていると判断。

初期コマンドとして"0123"を送る事にした。

しかし更に問題発生。13KB程度送受信した処で送信が停止する事態。

其処で"0123"を色々変更して挙動を確認して次の結果を得た。

"0" コマンドとは関係なし。送出は不要。

"1" 送信データ長を指定するコマンド。MSBからの送信となる。

"23" データ長。0x3332 -1 = 13105Byte が送信データ長と認識される。

システム構成

開発システムは下記部分で構成。

ホスト通信ソフト FTD2XX.dllを制御して、パソコン画面ででデータを送受信。

SPIターミナル USBの信号を受けて、SPI信号に変換するハード。

SPI信号交換回路 ホストとモニター間での、SPI信号交換するFPGAによる回路。

cm3モニター ホストからの通信で、モニターとして動作。

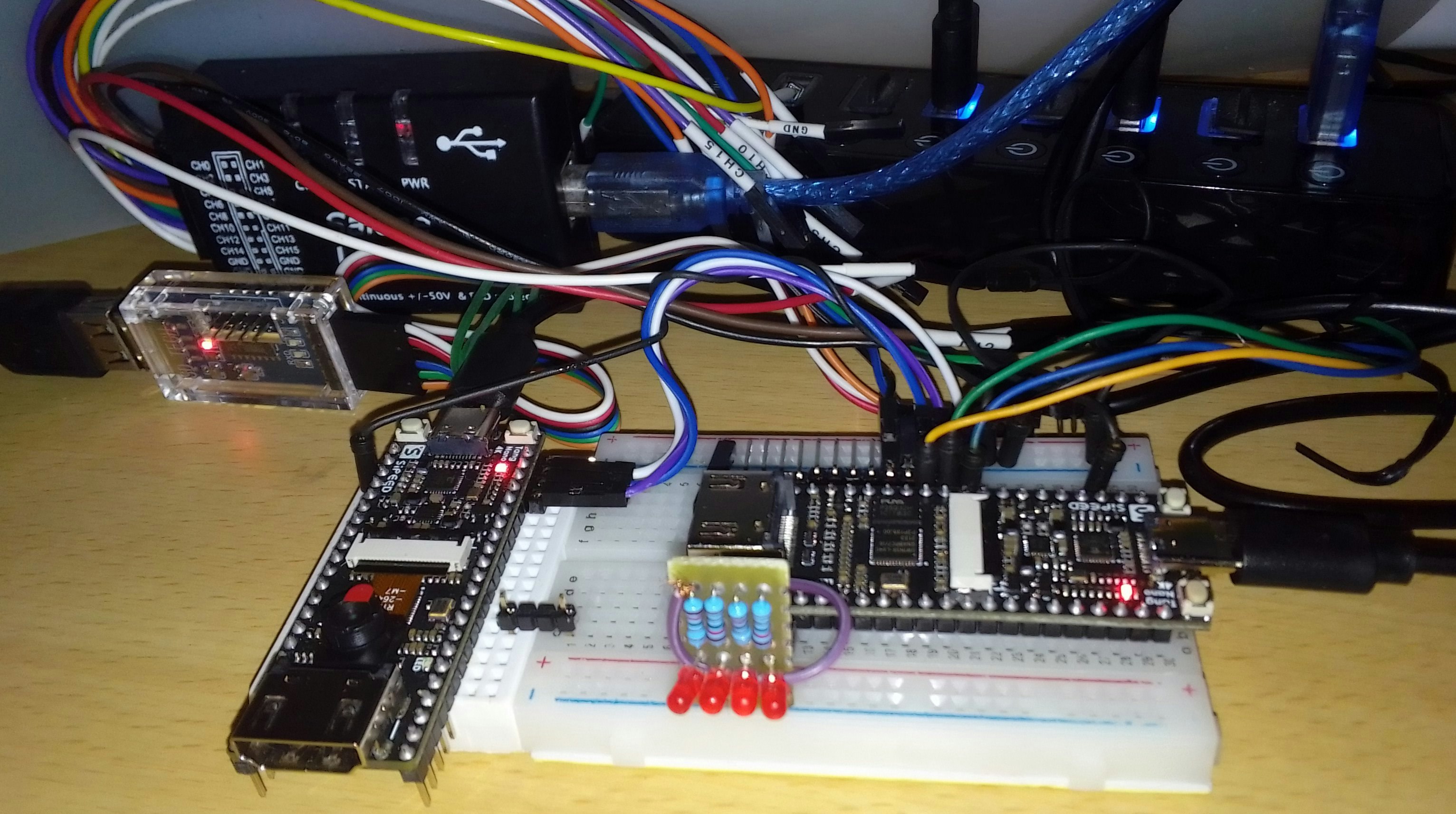

開発環境(笑)

前方右がTang-Nano-4K本体、表示用LED付、右も同様だがターミナルとして使用。

後方右は電源SW付USBハブ、左にロジアナが見える。その前はURT通信用のUSBシリアル。

ホスト通信ソフト

送受信動作は、

FT_Open -> FT_Write(初期化コマンド) -> FT_Write(データ送信) -> FT_Read(データ受信) -> FT_Close

を無限に繰り返す。

此処での注意事項として、データ送受信のByte数は同一にすること。

※間違えると戻ってこない。

FT_ReadはFT_Write時に受け取ったデータであり、新たに受信用クロックの送出は行わない。

※cm3側の受信処理では、0x00のダミーデータを送信してるが。

「ホスト通信ソフト」をgithubに上げておく。

ソフトはUSBTransferをベースに改変したのでC#で書かれており、VS2017でコンパイルした。

左上の Start Term をクリックして、緑に変われば通信可能になっている。

その横に表示の Devices はUSBポートに繋がっているデバイス数(x2)。

接続後デバイスが有効(デバイス数が2又は4)になってからクリックする事。

※相手がSPIターミナルで無くとも、通信可能と誤検知する。

SPIターミナルとJTAG用ピンのユーザー使用について

本体FPGAとの通信は、Tang-Nano-4K上のBL702を通信デバイスを使用するが、取り得る選択肢が二通りある。

[本体のBL702を利用]

Tang-Nano-4Kが一個で事足りるが、Analyzer Oscilloscopeが使えなくなる。

追加の外部配線は不要。

JTAGビンは、TCK(input)=7,TDI(input)=3,TDO(output)=4 に設定しておく。

[別のTang-Nano-4Kを利用]

Tang-Nano-4Kが余計に必要。

追加の外部配線として、TCK(16->7),TDI(13->3),TDO(17->4)を接続する。

※( )内は(ターミナルデバイス->本体デバイス)への結線を示す。

ターミナル側のJTAGビンは、TCK(input)=7,TDI(input)=3,TDO(input)=4 と設定しておく。

※FPGA側から余計な信号を貰わないように。

本体側のJTAGビンは、TCK(input)=16,TDI(input)=13,TDO(output)=17 と設定。

JTAG用のピンをユーザー側で使用する為に下記を設定。

Project -> Configuration -> Place&Route -> Dual-PurposePin -> Use JTAG as regular IO にチェックを入れると、JTAG用ピンをユーザーが使用可能となる。

【! 此処で重要な注意事項 !】

上記操作を実行後は、通常状態ではFPGAへの書き込みが出来なくなる。※当然だな

この状態で書き込む場合、JTAGSEL(Tg-Nano-4Kの08ビン)をGNDに接続する必要が有る。

※Use JTAG as regular IO のチェックを外せば元の状態に戻る。

※08ピンをGND接続状態では regular IO は利用できない。※これも当然

SPI信号交換回路

機能としては、JTAGからのSPI信号をMCUに送る。MCUからのSPI信号を、JTAGに送る。

どちらも相手はマスターなので、信号交換はSPIスレーブxスレーブとして動作する。

通信速度が異なるので、バッファ(16Byte)をかましている。

動作は「githubに上げた」、test_mcu_top.vを見てくれ。

※当初はデータ受信動作で誤入力多し。

JTAGからの信号が弱く、TDOの変化でTCK(クロック)にノイズが乗っているのをAnalyzer Oscilloscopeで確認。

FPGAの出力低減策として、DRIVE=8->4にする事により誤入力は無くなったが。

Analyzer Oscilloscopeの動作に影響しそう。真っ当なノイズ除去対策が必要かも。

cm3モニター

モニターの入出力を、UARTからSPIに振り替えただけ。

※USRKEY2を押しながらリセットで、UART入出力に切り替わる。

「githubに上げておく。」

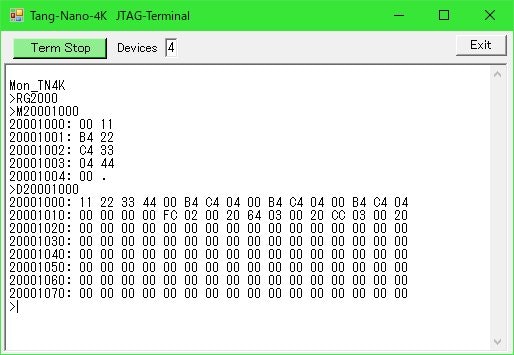

対応コマンドとして、下記を追加。

RS SPIからの受信データを表示。

RG GPIO入力を表示

WS SPIから送信 ※ WS 30 31 32 33 34(CR)

WG GPIOに出力 ※ WG 0001(CR)

Analyzer OscilloscopeによるMCU搭載回路のデバック

前回、mcuのデバックは出来ないと言っていたが、動作限定されるが利用可能で有った。

先ず、MCU込みの回路とソフトをEEROMに書込んでおく。(旧いProgrammerが必要)

次に、同一ロジックをAnalyzer Oscilloscopeの操作で書き込み、実行する。(Educationバージョンで)

MCUが稼働可能な状態で、Analyzer Oscilloscopeでの計測が可能となる。

※ロジックを書き換えても問題無く使えたが、何処まで行けるかは不明。

MCU

MCUに付属のGPIOは Enable GPIO をチェックするだけでは、inoutとしてビンへの接続しか出来ず内部使用不可。

しかしその下の、 Enable GPIO I/O のチェックを外すと入出力が分離される。

この状態では、GPIOの信号がFPGA内で信号として利用可能となる。

※専用のIOポートを作らなくても、GPIOを使ってFPGA部との信号のやり取りが出来る。

MCUのRAMとして、ディフォルトでは16KB割り割り当てられるが、これは20KBしか無い貴重なBSRAMの無駄遣い。

EMPU設定画面で SRAM部 をダブルクリックして 設定画面を開けば SRAM SiZE の変更設定が可能。

※BSRAMが多く残れば、Analyzer Oscilloscopeでのキャプチャー範囲が増やせる。

MCUが必要なRAMはコンパイル画面のdataセクションの表示で判る。(多分)

現状は1084Byteと表示されている。設定で4KBを割り当てている。2KBに減らしても良いかも。

BSRAMの使用について

通信バッファを構成しているが、バッファを256byteとした場合、BSRAMを使用していた。

バッファを32byteにした場合、BSRAMは使用されなくなったが、LUTの使用が200LUT程度増加。

最適なバッファ容量も有るだろうが、BSRAMとLUTのどちらを使うかを天秤にかける事も出来る。

※BSRAMがもっと多ければ何の問題も無いが、コストに絡むのだろう。

BSRAMが必要なのはAnalyzer Oscilloscopeの使い勝手向上の為であり、素人的運用だけど。

Analyzer Oscilloscopeの利用について

設定ファイル作成時には、 For Post-Synthesis を推奨しているが、 For RTL Design の方が使い勝手が宜しい。

この状態ではロジックで作成した信号名だけが表示される。中間的な信号は無い方が素人は判りやすい。

また、他社の物の様に、信号が存在しませんと言われない。

この状態ではその分、最適化されて無いと言う事だろうけども。

なにより、この程度の規模ではコンパイルは爆速、ロジックをガシガシ組み替えて動作確認が出来るのは嬉しい。

※シミュレーター環境組むほどの能力も根気も無いからね。

Programmerと同様、USBにデバイスを1個以上接続すると動いてくれない。

従って、書き込み時は本体のみにして行うが、Analyzer Oscilloscope動作時はそうも行かない。

そこで、まず本体のみ接続しておきAUTO(連続再起動)で起動し、追加デバイスは起動後に繋ぐ。

JtagTermは後から繋いだ方と通信するので、その儘で計測続行が可能。

※本体をUSBハブの上流に置かないと駄目かも知れない。

但し、都合よくトリガが掛かるように考慮しないと、再トリガで波形が流れてしまう。

※MCUからGPI経由でトリガ信号を制御すれば問題無し。

凄く便利なんだけど、設定の判り難さは何とかならないものか。

特にトリガ条件の設定。Valueの設定が、RとかF,0,1とか言われても判るかな。

※トリガ信号を一本に絞り、自前でトリガ条件回路作れば済む話だけど。

感想

今回のデバックでも活用したが、コンパイル速度が速いのと相まってAnalyzer Oscilloscopeが超便利。

ものの数十秒でロジックの動作再確認が可能になる。これなら半田付けよりも早いぜ。

昔からFPGAで戯れてる身としては、ターンアラウンドの改善には驚異さえ感じてしまう。

こんな機材を使う勉強と、紙上でand,orなんて言ってるレベルでは、競争にならないだろうな。

パソコンと基板一枚あれば、技術レベルは飛躍的に向上。でも日本の教育ではやんないだろうね。

高級な機材を有する教育期間も有るだろうが、其れじゃあ遅いんだな。

プログラム教育が問題になってるが、ハードウェアはそれ以前じゃ無いかな。なんてね。

JtagTermが使えるレベルになっているとは思うが、制約が面倒くさいので、使うかどうかは微妙。

なお、上記記載内容は全て無保証であり、各自の責任においてご利用願います。