目的

DOSを探してガラクタ箱を漁っていると、MB6890.ZIPがひよっこり出てきた。

なんだろうと思い起すと、なんと!ベーシックマスター レベル3のROM(BASIC)ではないか。

そしてなんと、来年はレベル3が1980年5月に発売されてから来年5月で生誕40周年ではないか。

◆◆◆ そうだ、ベーシックマスター レベル3 生誕40周年を祝おうではないか ◆◆◆

ささやかな祝福ではあるが、ベーシックマスター レベル3をFPGAで再現してみよう。

まあ、40周年は今から約半年後ですけどね。

経緯

投稿者は日立関連の会社に在籍したことが有り、それなりの思い入れが有ります。

※他社製の機器を購入申請すると、却下率が高かったという事情も有る。

※レベル3に通信アダプタ(自社製)を接続し、遠隔(リモート)監視システムを構築した。

しかし、なにせ大昔の事であり詳細を覚えているはずもなく、まずは情報を収集。

1.国会図書館に出向き、月刊I/Oの別冊『ベーシックマスター活用研究』に記載の回路図をコピー。

※回路図は入手したが、ロジックが複雑で、根気が続かず詳細分析は断念。

2.「日立 ベーシックマスター レベル3 マーク5 / S1」で機能等を再確認。

※上記以外は断片的で、かろうじて残っているという状態か。

<未来技術遺産登録について>

2015年9月1日に国立科学博物館の定めた重要科学技術史資料(通称:未来技術遺産)の第00206号として、登録されている。

しかし技術資料も保管せず、筐体(あえてガラクタといおう)を保管してなにをしたいのか、何の役に立つというのだろうか。

目的が良く判らない。

むしろコンセプト、回路図、ROM等を収集/公開して次の世代に、多少なりと技術を伝承すべきと思うがどうだろう。

過去の技術者の自己満足の世界ではなかろうか。こんな事をしているから諸外国に置いて行かれるのだろうね。

もしベーシックマスターの関係者がこれを見られたら、技術を公開してほしい。(まあ、いないだろうが)

コンセプトなど

今回の目標は完ぺきなMB6890のemulatorを作ることではない。

その理由としては、単に投稿者の技術レベルが低い為であり、完全性は求めない(求められない)。

ではなぜ行うのか。その理由は

1.投稿者の知的欲求を満足させる(自己満足を含むが)。

2.多少なりと次の世代への啓発を。

FPGAの例題として、LEDちかちかが推奨されているが、それ以降は極端に敷居が高く、無理と諦めてしまっているのではないか。

こんなことが出来る、この程度のことはできる等を見せて、連続的な技術のステップアップを図れるようにすべきであろう。

現在のFPGAによる開発は下記のよう、昔に比べ格段に簡単になっている。

その分、最先端は高度になっているともいえるが、昔に比べ出来る事は格段に多くなっている。

レベル1 専用LSI/ICを配置/配線し、グルーロジック(周辺回路)のみをFPGAで構築。 <-------- 黎明期

レベル2 専用LSI/ICをFPGAで(自分で)設計、メモリーは専用ICを配置/配線する。 <-------- 10年ぐらい前か

レベル3 専用LSI/IC(モジュール)のVHDLを探してきて設置、全回路をFPGAで構成可能。 <-------- 現在のレベル

※ちなみに今回のemulatorは現時点では、DE10の5%のロジックと10%のメモリで構成出来ている。

emulatorは32MHzで動作し、また規模は1/10程度の事より、DE10は実機の320倍の性能を有する事になる。(ほんとかいな)

前提条件

以下のハード・ソフトを予め準備の事。(購入先、金額は参考までに)

1. FPGA-board DE10-nano(ソリトンウェーブで購入した 18k円)

2. IO-board MiSTer FPGA IO 5.6 Board for DE10 Nano(ebayで購入 6k円)。VGA出力部分のみ使用。

3.Quartus Prime FPGAのプログラムを作成。(開発は Ver17.1)

開発手順

まず下記に示す順序で回路を構築。コンパイルエラーを潰していく。

signaltapで信号確認しながら間違いを訂正していったら、一週間程度で初期画面が出た。(やったね)

※メモリが潤沢にあるのでsignaltapを使い放題。

これが旨く行ったら、後は個別に機能をインプリメントすればいい。

<動作確認>

1.DE10のハード動作を簡単なプログラム(例えばLチカ)で確認。

2.VGAハードを接続し、簡単な表示プログラムを作成し、表示回路の動作確認。

3.所持するL3(レベル3)ROM使える事をソフトemulatorで使える事を確認する。

<回路設計>

せっかくコピった回路図だが、詳細には分析しなかった(面倒くさい)。

「日立 ベーシックマスター レベル3 マーク5 / S1の記載を参照し、機能を順にインプリメントした。

※そのため、本物と似ていない部分が有るような気がする。

1.モジュール(6808,CRTC等)を集めプログラムに配置。

2.メモリ類をalteraのライブラリを使用して定義、ROMはROMファイルと結びつける。

3.L3のCS(チップセレクト)信号を作成し、各モジュールに配線。

4.CPU(MPU)のアドレスバスを、各モジュールに配線。

5.CPU(MPU)の出力データバスを、各モジュールに配線。

6.CPU(MPU)の入力データバスに、各モジュールの出力をCSで選択して接続。

7.L3(レベル3)で使用している、レジスタ類を定義、CSで選択してR/W接続。

8.ROMを逆アセンブルし、プログラムの動作(特にスタートアップ)を確認。

9.コンパイル結果をFPGAに書き込む。

10.リセットスタートし、RESETベクターからの、ROMの読み取り動作をchipscopeで確認。

11.メモリへのR/W、プッシュ/プル動作部分で、RAMの動作を確認。

12.CRTCへのアクセス信号を参照し、CRTCの初期化を確認する。

13.CRTCが0x400(VRAM戦闘)にアクセスした時に、メモリから0x48('H')が出力され、FONTROMからは対応するビットデータが出る事を確認。

※ここまで正常であれば、初期画面には'HITACHI....'と表示されるはず。

主要モジュール

本emulatorはMultiCompの6809部分をベースにして構築している。

※webサイトが紹介出来ればいいのだが、既にサイトが閉鎖されているような気がする。

※MultiComp_MiSTerが技術的に同じような気がする。

1.CPU(MPU) 6809

MultiCompで使用されているものを利用。

2.RAM

alteraのライブラリを使用。

2port.ramとして定義しているので、表示アクセスとの競合を考慮する必要はない。

3.ROM

alteraのライブラリにROMデータをバインド。

※L3BAS.HEXをROMフォルダに格納の事。

※ROMファイルがBINの場合はHEXに変換が必要。

4.FONT

alteraのライブラリにROMデータをバインド。

※ROMファイルがBINの場合はHEXに変換が必要。

5.CRTC

「BBC Micro for Altera DE1」に使用されているものを利用している。

※VGA出力とする為にインターレースは無効としている。また、表示位置補正の為にVSYNCの位置をずらしている。

※インターレースを無効とする為に「mc6845.vhd」に2か所改悪(----でコメントアウト&追記)。

残光性のモニターが入手できるのであればコメントを取り外せば動くかな。

※インターレースを無効にしているので、インターレースを前提にしているソフトは動かない。

6.キー入力

キーボードレジスタ(0xffe0)にスキャンコード(0x80-0xfe)をセット後、入力無(0xff)をセットすることにより入力となる。

PIAではなく単なるレジスタとして設計している。

なお、本emulatorにはキーボードを付属していない。※色々な手段が考えられるが、ハード/ソフトの追加が必要でちょつと面倒。

ではどうやって入力するかというと、jtag-usb接続を利用して、システムコンソールから入力する。

※Misterのロジックを使えばUSBからの入力が可能となるが、機構が良く判らない&コンパイル時間が長くなるのでやっていない。

動作方法

1.ソースをQuartusでコンパイルする。

ソースファイルの場所は

2.output_filesフォルダに**.rbfが出来上がるのでDE10に書き込む。

3.システムコンソールを起動する。(Quartus tools -> System.Debugging.tools -> System.Console)

4.System.ConsoleのSystem.Explorer(左側)のscriptsフォルダに格納したスクリプトを実行(Execute.script)する。

※ダウンロードしたscriptsフォルダを予めコピーしておく。

<スクリプトに関する解説>

スクリプトはTCLコマンドで作成している。(attera方言が微妙)

L3にキーコードを送る場合、スクリプトファイルに ss "キーデータ"と記載し実行すると、L3の画面に"キーデータ"が表示される。

※ssはスキャンコードを送る関数。

※最低限のキーしか定義していないので、未定義のキーも存在する。(必要なら追加してね)

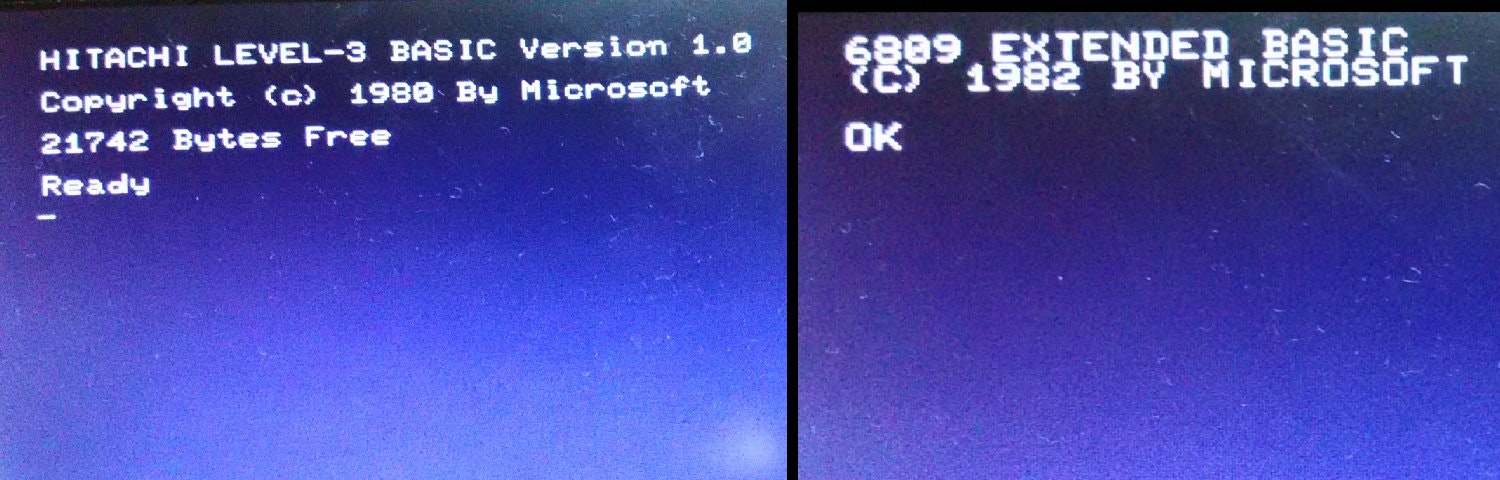

起動画面 6809 EXTENDED BASICでの起動

起動画面 6809 EXTENDED BASICでの起動

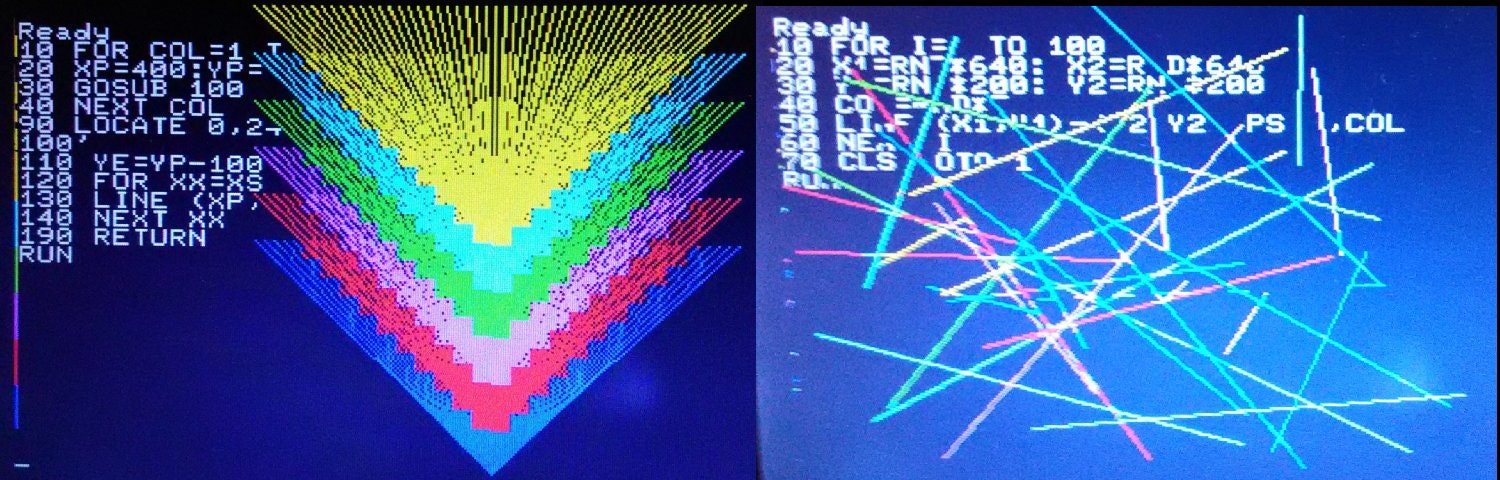

グラフィック表示の例(32Mhzにすると早いぞ)

グラフィック表示の例(32Mhzにすると早いぞ)

L3ROMが無い場合は

L3ROMを持っていないが、どうしても試して見たい場合はROMフォルダ内のEXT_BASIC.HEXをL3BAS.HEXにリネームしてコンパイルする。

※EXBAS.HEXは「6809 EXTENDED BASIC(Microsoft 8KBasic)」にL3用の入出力を追加したもの。(freeになっているはず)

キー入力スクリプトは sn "キーデータ"と記載し、実行する

※snはアスキーコードで送る関数。

FPGAで設計されたベーシックマスター レベル3は現存しない。(多分)

※10年位前に開発中の記述が散見されたが、開発資料などは見当たらない。

これは、技術資料が公開されてないことに起因すると考える。(一部公開している会社も有るが)

過去の技術を伝承し将来につなげる為に、可能な限り公開すべきと考えるが、如何なものだろうか。

なお、もし追試する奇特な方がおられた場合、上記記載内容は無保証であり、各自の責任においてご利用願います。