効能

VTL_on_FPGAのハードの基本動作をお手軽にデバッグする事が出来ます。

※多少誇大広告気味

元ネタ

下記サイトが非常に参考になりました。

[Icarus Verilogコンパイラを使う]

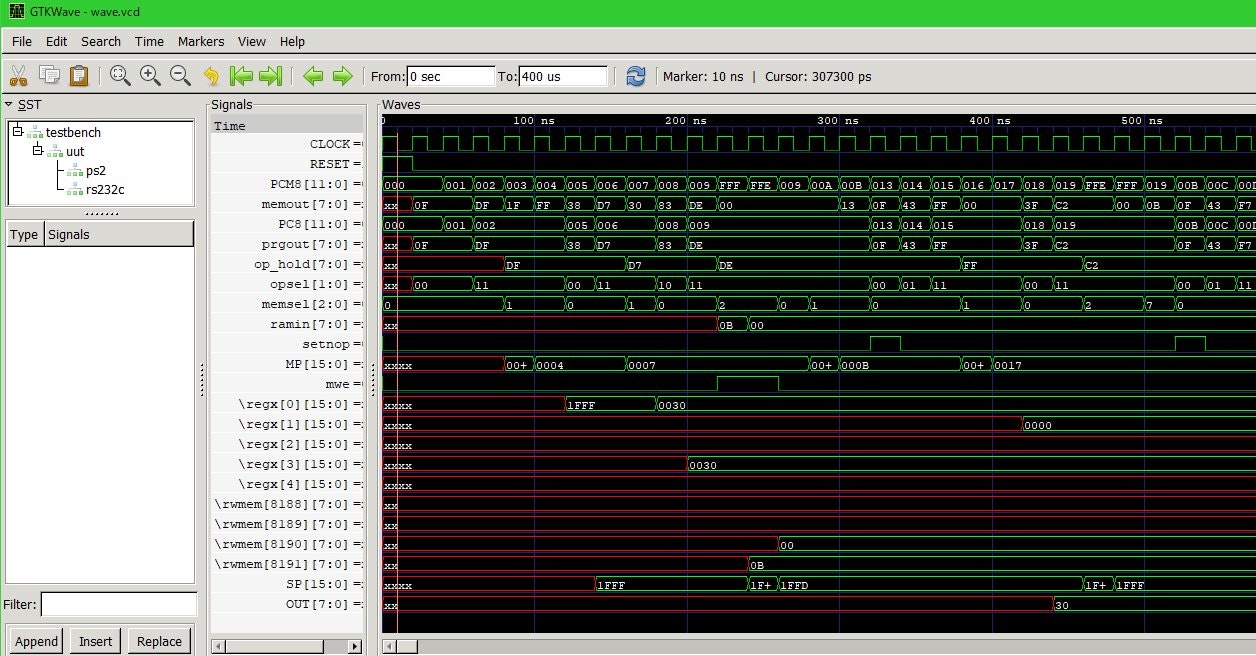

利点:クロック毎の各信号の挙動がまるわかりで、自分のおろかさを見つけられます。

欠点:目を皿のようにして信号を見つめる必要があります。

テストベンチを書くのがキモだと思います。

インストール

が、元ネタはLinuxであり、Windows用のIcarus Verilogとgtkwaveのインストールが必要。

インストール先は各自で異なると思うので「_run.bat」を編集して下さい。(\APP2\の部分)

プログラムソースはこちらに上げています。

[td4_sim]

@@echo off

C:\app2\iverilog\bin\iverilog -o td4.o rs232c.v ps2_rx.v td4.v td4_tb.v

C:\app2\iverilog\bin\vvp td4.o

timeout 3

C:\app2\iverilog\gtkwave\bin\gtkwave wave.vcd -a td4.gtkw

del td4.o wave.vcd

操作

(1)「TEST.GM」に次のようなVTLプログラムを書きます。

10 B=$30

20 !=90

30 B=B+1

40 #=20

90 <0=B ]

(2)GAME86を起動し、「[[[」コマンドを発行。

「pram.hex」が作成されます。

※開始番地を0にするのを忘れないように。(R=$0000)

G>>[[[

[p0 [LO gm80\test.gm [p1 [LO gm80\gm80.gm #=1

-PASS1-

10 0000 B= $

20 0009 !=

30 0011 B= B + 1(01)

40 001A #=

90 0022 <= B ]=

-PASS2-

0000 NOP: 0F

0001 LIA: DF 1F FF

0004 STS: 38

0005 LIA: D7 30 ; 10 B=$30

0007 STA: 83

0008 JSR: DE 00 13 ; 20 !=90

000B LDA: 43 ; 30 B=B+1

000C LIB: F7 01

000E ADD: 01

000F STA: 83

0010 JMP: FE 00 08 ; 40 #=20

0013 LDA: 43 ; 90 <0=B ]

0014 LIB: FF 00 00

0017 OUT: 3F

0018 RTS: C2

0019 RTS: C2

Hex作成 クリップ作成

SOURCE:44(0000-002C)

OBJECT:26(C000-C019)0000-001A

WORK :42(7800-7857)

G>>

(3)「pram.hex」を「TD4_SIM」にコピー

「_run.bat」を起動。

エラーが無ければ、次のような画面が表示されます。

その他

とりあえず動いているのレベルであり、状況によっては動かない可能性が有ります。

上記記載のハード、ソフトは無保証であり、各自の責任においてご利用願います。