はじめに

MathWorks社のHDL Coderを使うことで、SimulinkモデルからVerilogHDL/VHDLを生成しFPGAの実装まですることが出来ます。

HDL Coderが対応しているFPGAはこのページに載っているのですが、各FPGAに載っているベンダーIPがフルに使えるわけではなく、一部のIPについてはカスタムボードの設定が必要のようです。

ここらへんの情報(特にPS+PL部を動かす場合)があまりネット上に転がっていない上に、公式ドキュメントにもあんまり明記されていないようなので、やり方を備忘録がてら記載します。

そこで、この記事では、Xilinx社のSoC ZC702のXADCの取り込みを例に下記の順番で実装手順を解説します。

- 前提となる知識

- 開発環境の構築方法

- 具体的な実装手順

- 動作確認

本記事ではZC702ですが、ゆくゆくはほかのFPGAのカスタム手順も追加出来ればなあと思っております。

開発環境

開発環境はこの記事を書いている時点で最新のバージョンであるMATLAB R2023bを入れています。

また、サポートパッケージとしてHDL Coder Support Package for Xilinx Zynq Platformを入れています。

- OS: Windows 11

- MATLAB: R2023b

- MATLAB

- Simulink

- MATLAB Coder

- Fixed-Point Designer

- HDL Coder

- HDL Coder Support Package for Xilinx Zynq Platform

- Xilinx Vivado 2022.1

HDL CoderはSimulinkの中で作成したサブシステムから、FPGAに搭載するサブシステム、CPUに搭載するサブシステムを指定し生成します。それぞれインターフェイスが用意されたひな形(リファレンスデザイン)が用意されており、そこにソフトウェア・ユーザロジックはめ込むイメージです。そのため、インターフェイスをわざわざ作ることなく設計をすることが出来ます。

しかし、逆に言うとリファレンスデザインに含まれていないベンダーIPを含むシステムは生成することが出来ません。そこで、リファレンスデザインのカスタマイズを行います。

リファレンスデザインのカスタマイズは、まずFPGA側のリファレンスデザインのカスタマイズを行います。続いて、その内容をCPU上Linuxに知らせるためDeviceTreeの作成を行います。

それぞれ、FPGAのリファレンスデザイン作成についてはPL側イメージ作成編、デバイスツリー作成についてはPS側イメージ作成編で解説します。

今回はZC702にXADCコアを追加して取り込んでみます。イメージは下記の図のようになります。

PL側イメージ作成編

本記事では、ベンダーIPの例としてXilinxのADコンバータであるXADCを取り込み、SimulinkからHDLのコード生成をする際に叩けるように設定してみます。

そのためには、2つのファイルが必要になります。

- Vivadoでの「リファレンス設計」ファイル

- HDL Coder用「ボード登録」ファイル

ボード登録ファイルよりリファレンス設計ファイルを参照することで、連携させることが可能です。

Vivadoでの「リファレンス設計」ファイル作成編

MATLABにはサポートパッケージというものがあり、リファレンスとなるデザインが簡単にインストール出来るようになっています。このデフォルトのリファレンスデザインを拡張し、XADCのコアを追加します。

まず、MATLABのアドオンマネージャからHDL Coder Support Package for Xilinx Zynq Platformをダウンロードします。

HDL Coder用「ボード登録」ファイル作成編

HDL Coder Support Package for Xilinx Zynq PlatformにおけるZC706ボードのリファレンスデザインを拡張します。まず、ZC706のVivadoのデザインファイル(拡張子xpj)を開きます。

そこから、下記のようにXADCへアクセスするためのIPを追加します。

追加するIPはXADC WizardのIPを追加します。

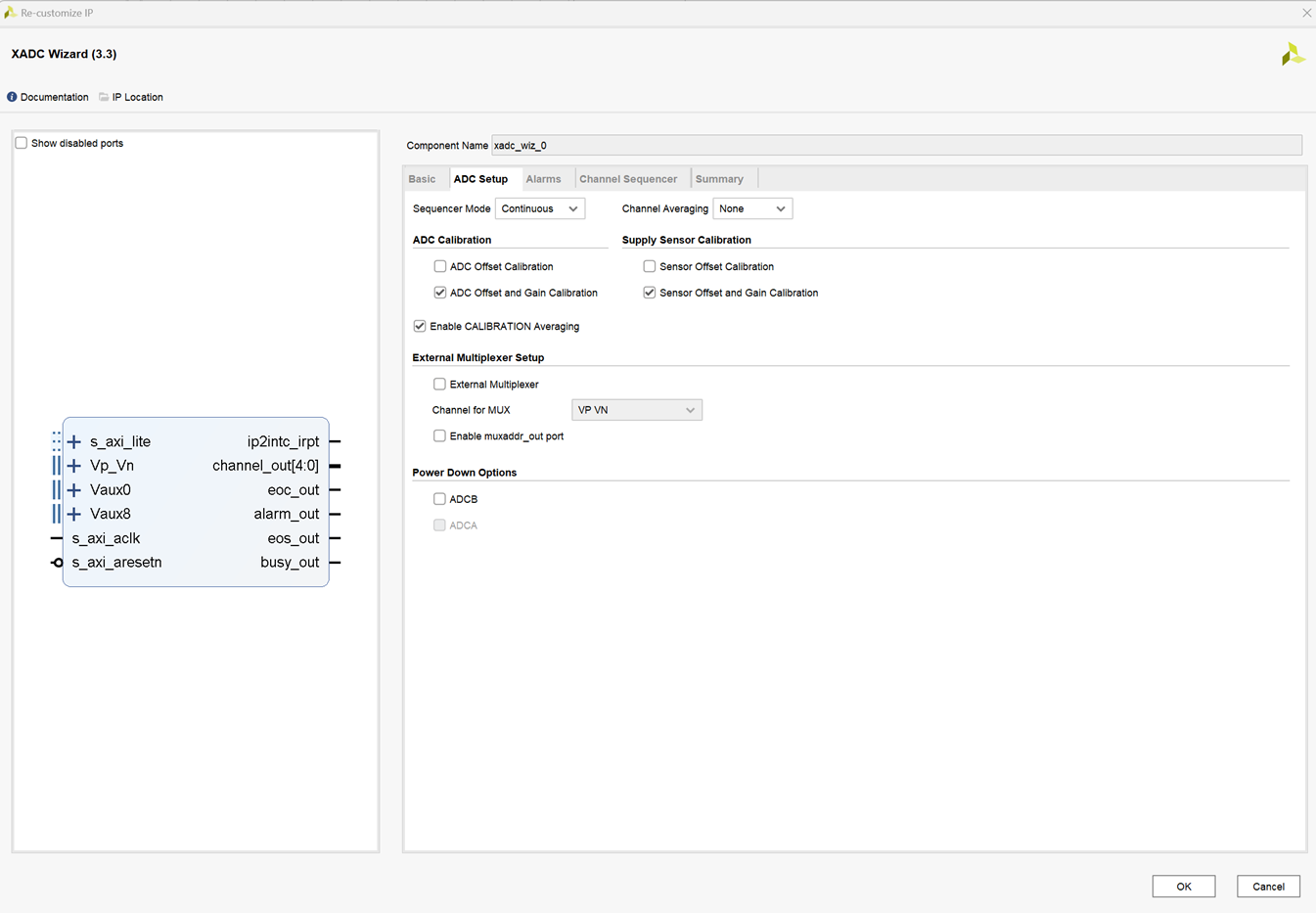

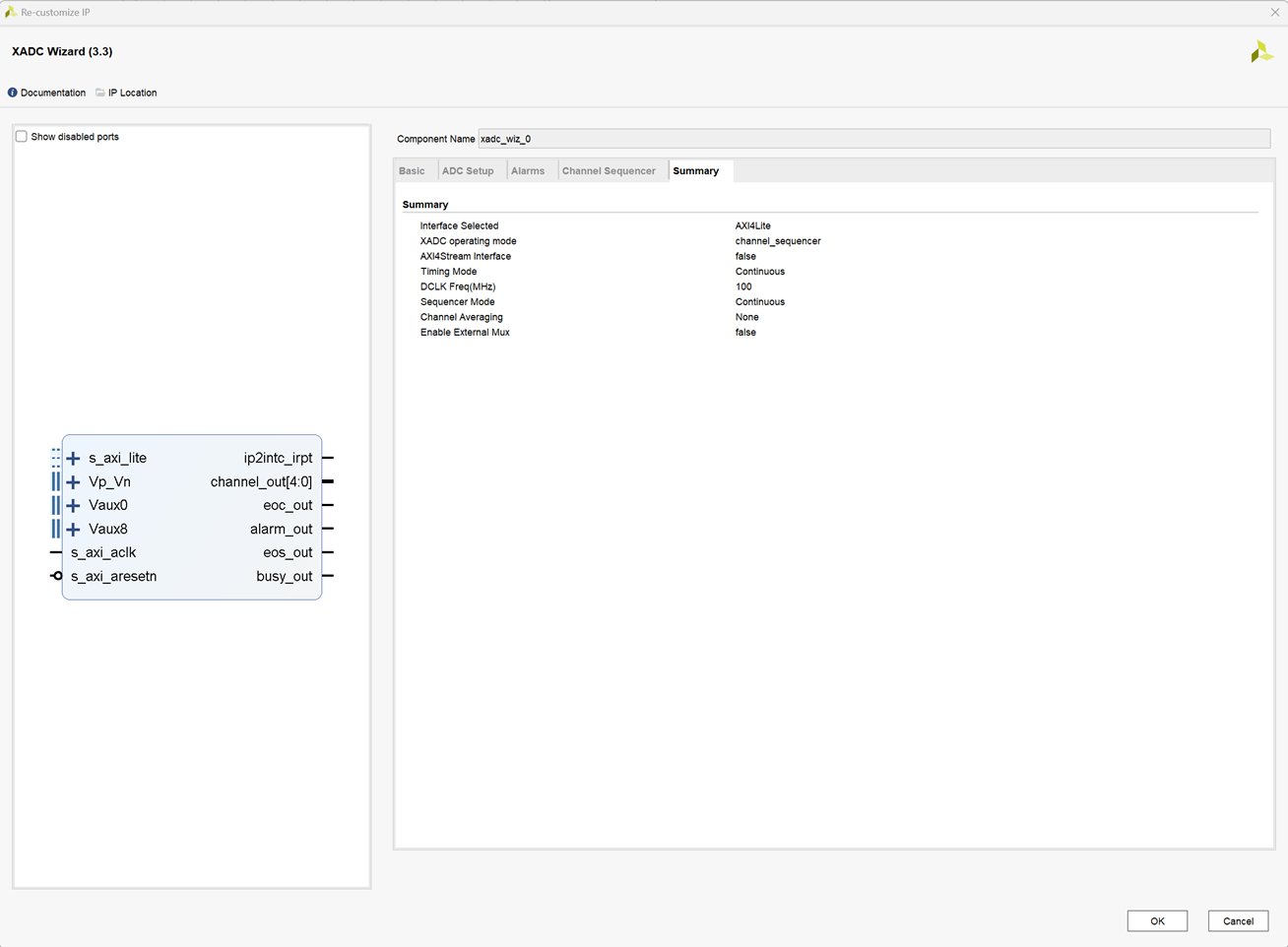

Wizardでの設定は下記の通りです。

WizardでのXADCの追加が完了したら、AXI Interconnectへ接続します。

参考:

Zynq XADCの使い方

Testing input voltage on Xilinx zynq-7020 Z-turn by XADC

7シリーズFPGAおよびZynq-7000 SoC XADCデュアル12ビット1MSPSアナログ-デジタルコンバーター

レジスタのアドレスの設定は下記のように行います。

XADC用のAXIインターフェイスと、HDL Coderから接続するためのインターフェイスを用意します。

続いて、XADC IPからペリフェラルのピンアサインを行います。まず、外部ポートを作成し、XADC IPのうちVaux0とVaux8に接続します。

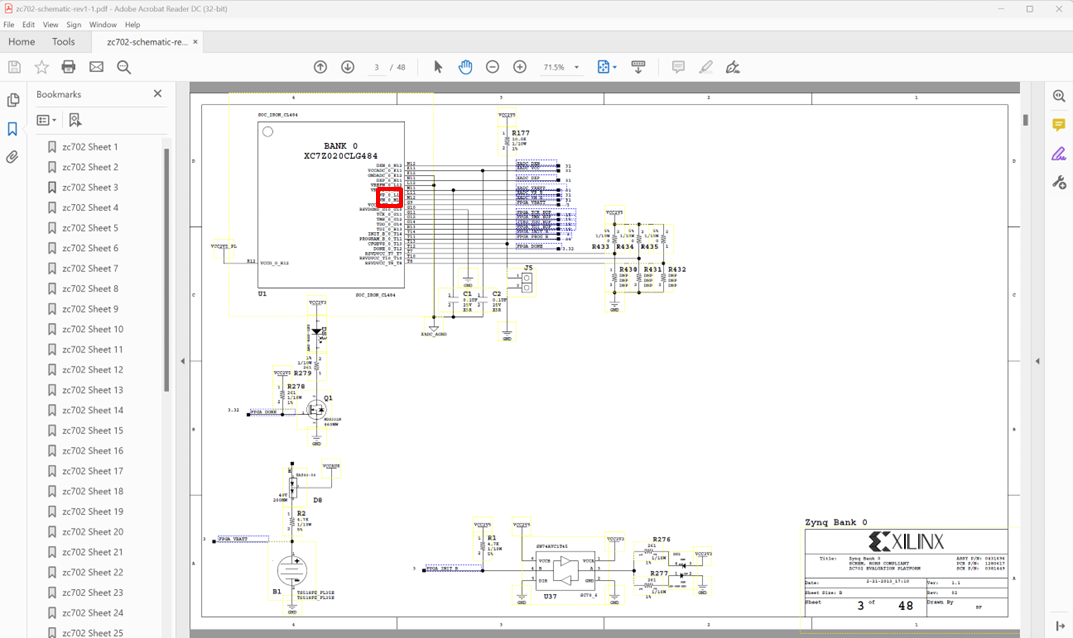

作成した外部ポートに物理ピンをアサインします。先ほど作成した、Vaux0とVaux8に加え、デフォルトで用意されるVnVpも赤枠内に表示されていると思います。

赤枠で囲んだ通り、ピンアサインを行うため、Package PinとBankの値を設定します。

これらの値はデータシートより確認することが可能です。「xilinx zc702」等でググることでXilinxのドキュメントページが出てきますので、その中を覗いてみると回路図のデータシートからピンの番号・バンクを確認することが可能です。

また、そのピンの接続先のピンヘッダも確認することが出来ます。

XDCファイルに下記の情報を書き込みます。

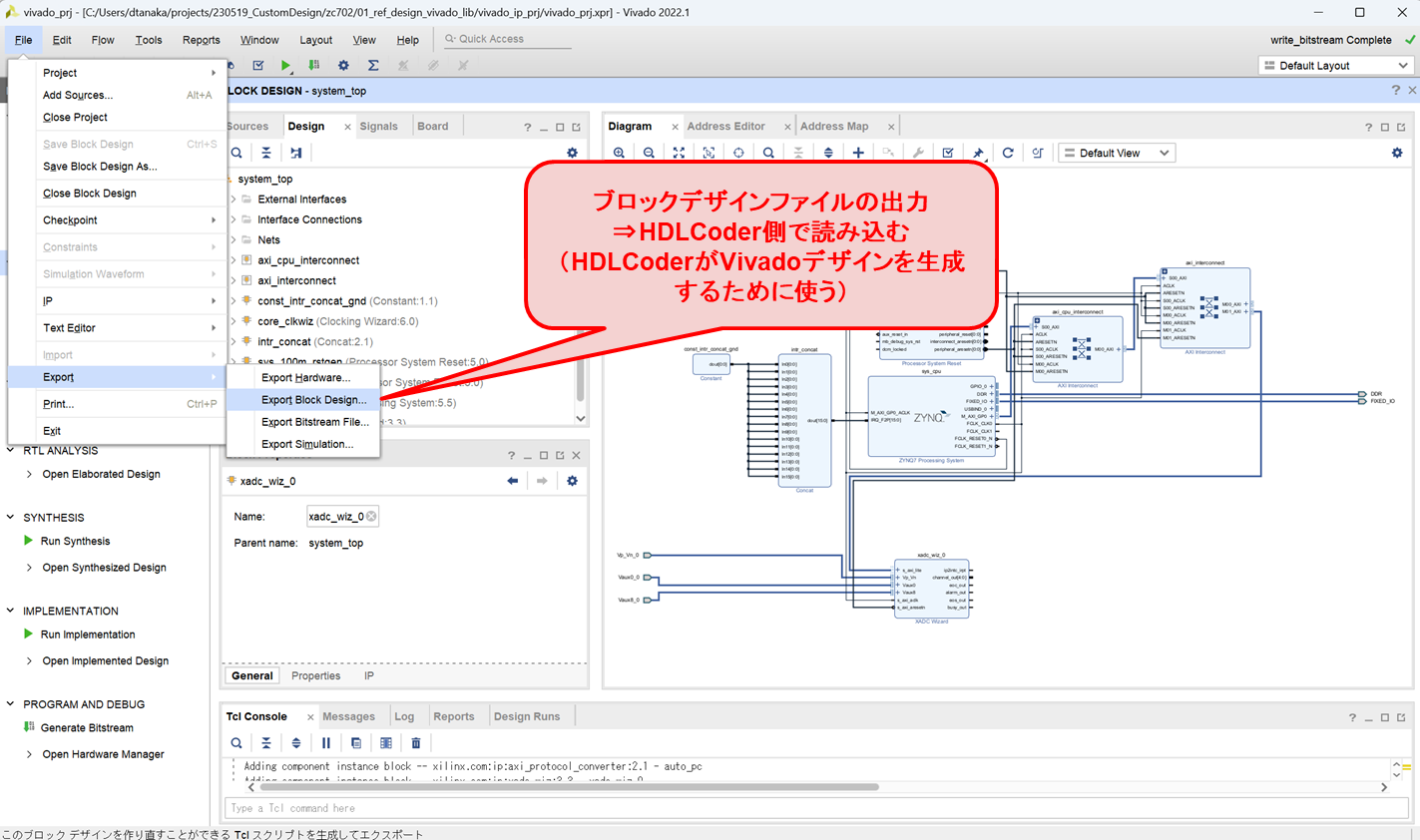

モデルのエクスポートを行います。

HDL Coder用「ボード登録」ファイル作成編

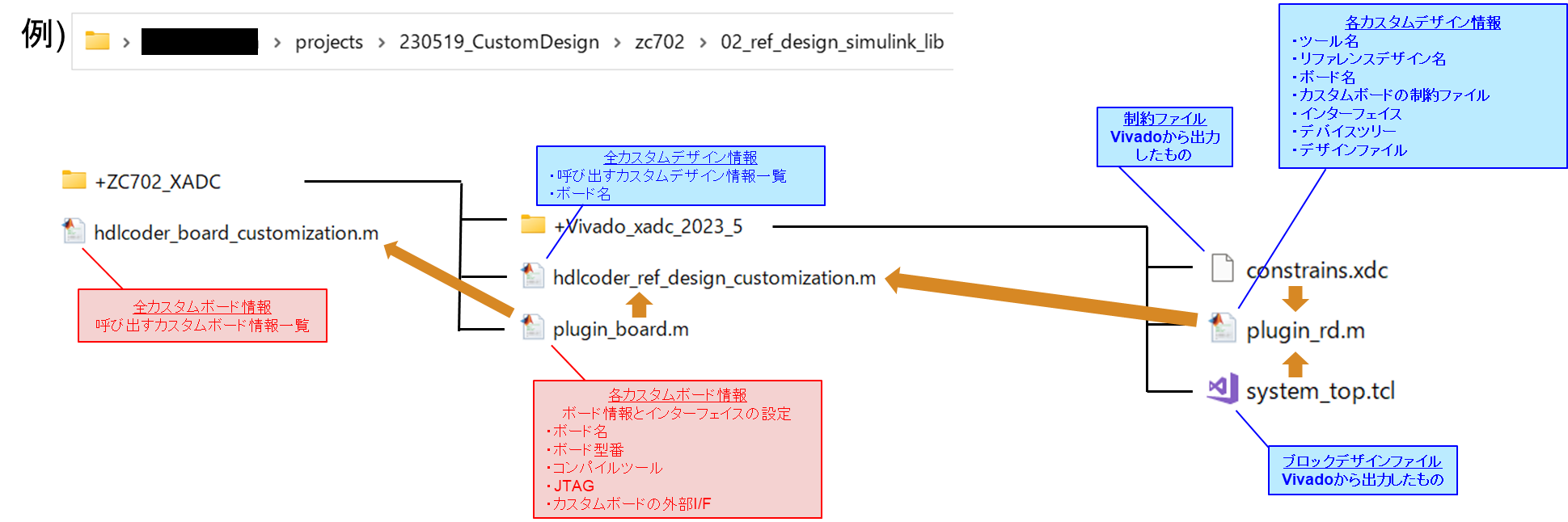

ボード登録ファイルは4つのファイルから構成されます。

下記のフォルダ構成にしてそれぞれのファイルを配置してください。

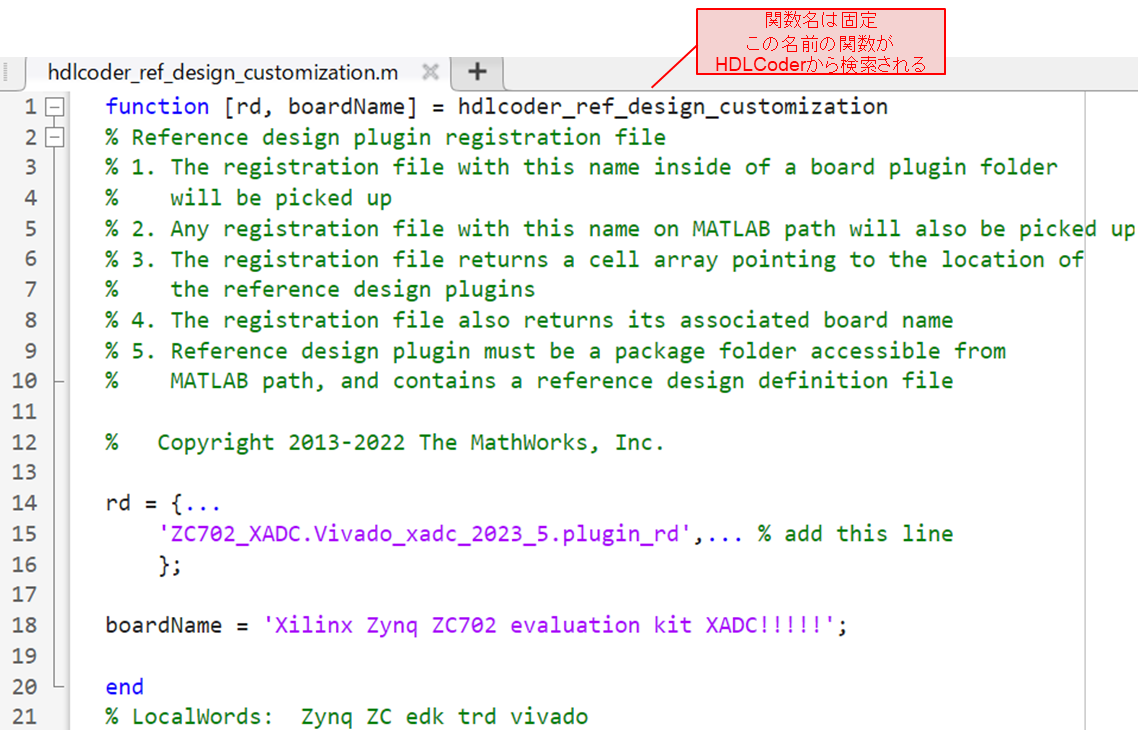

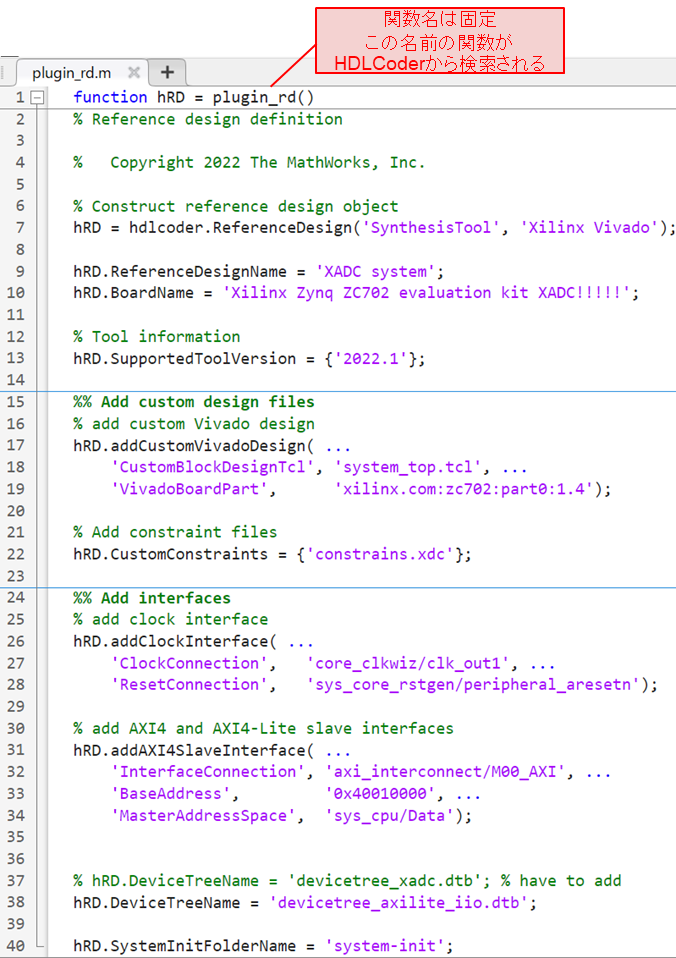

各ファイルの記述は下記のとおりにしました。

BoardNameはほかと区別出来る名前を付けてください。

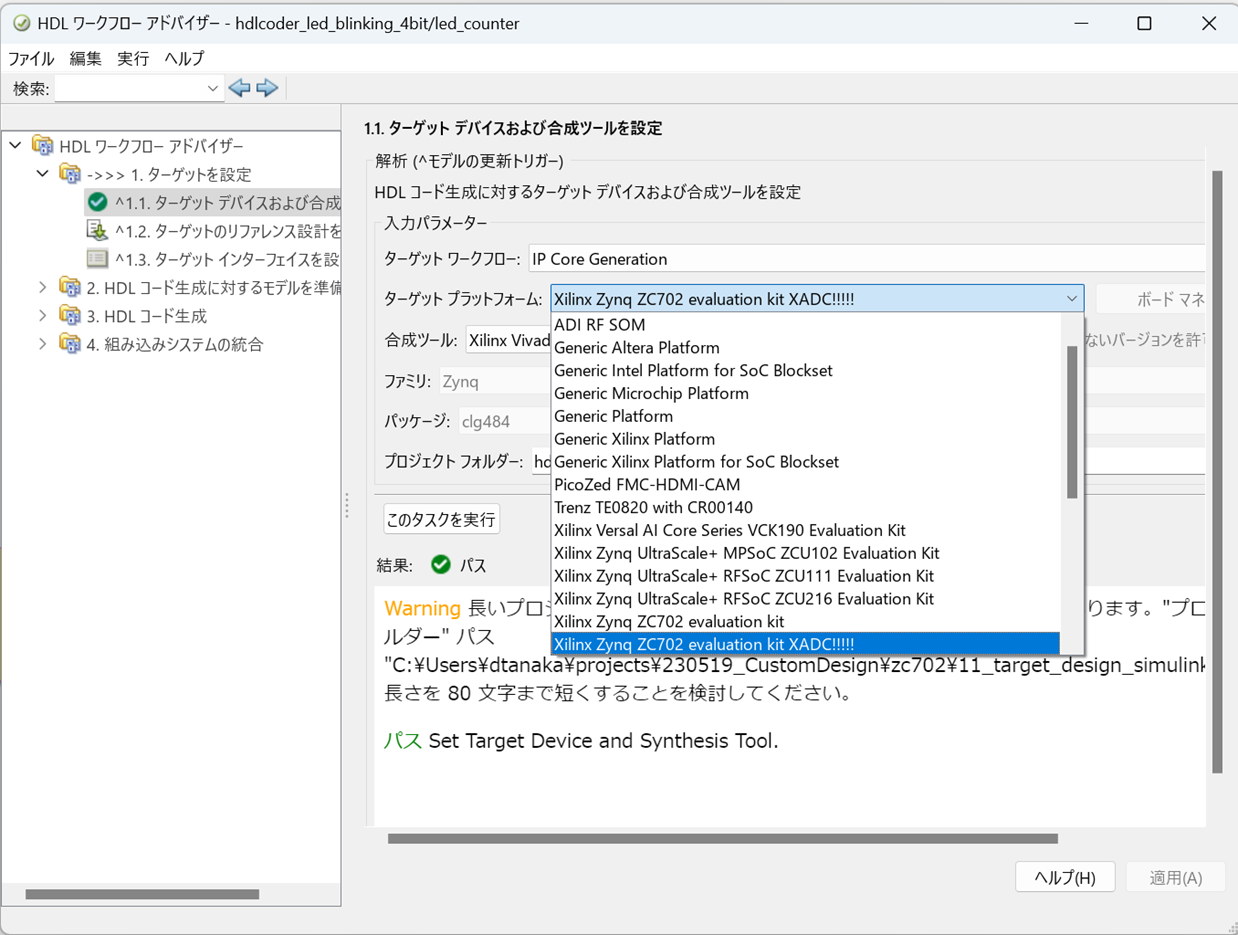

ここまでできれば取り込みが出来ます。上手くいっていればHDL Coderのワークフローアドバイザーにおけるターゲットプラットフォームから下記の通り自分の追加したカスタムデザインの選択肢が出るはずです。

続いて、次回はPS側のイメージを作成する手順について解説出来ればと思います。

更新履歴

2023/11/20 初版