目的

最近、リサンプリング(レート変換)をFPGAに効率的に実装するテクニックを知ったので、備忘録がてらまとめておきます。

この記事は実装上の嬉しさにのみ言及しており、原理については記載しておりません。そちらについては専門書をご覧ください。

背景

ワイヤレスや、音声信号処理のアプリケーションにおいて、レート変換をしたい、というときが有るかと思います。例えば、ワイヤレスのアプリケーションにおいて、ADコンバータではサンプリング周波数が10GSPSであっても、実際に変調されたベースバンド信号のレートが低い場合、レートを下げて処理することでリソース消費量を減らしたい、といったことが有るかと思います。この時、単純に間引きをしてしまうとエイリアシングが発生してしまうので、事前にフィルタを使って高い周波数成分を取り除き、そのあと間引きを行います。

こちらの記事が分かりやすいです。

https://edn.itmedia.co.jp/edn/articles/1208/10/news093.html

このような「フィルタ」+「間引き」が一体になった処理をデシメーションといいます。

さて、このような処理を実装するにあたって、高いレート変換比が必要であるとき、フィルタのタップ数が多くなってしまい、多くのリソースを消費してしまいます。

ソリューション

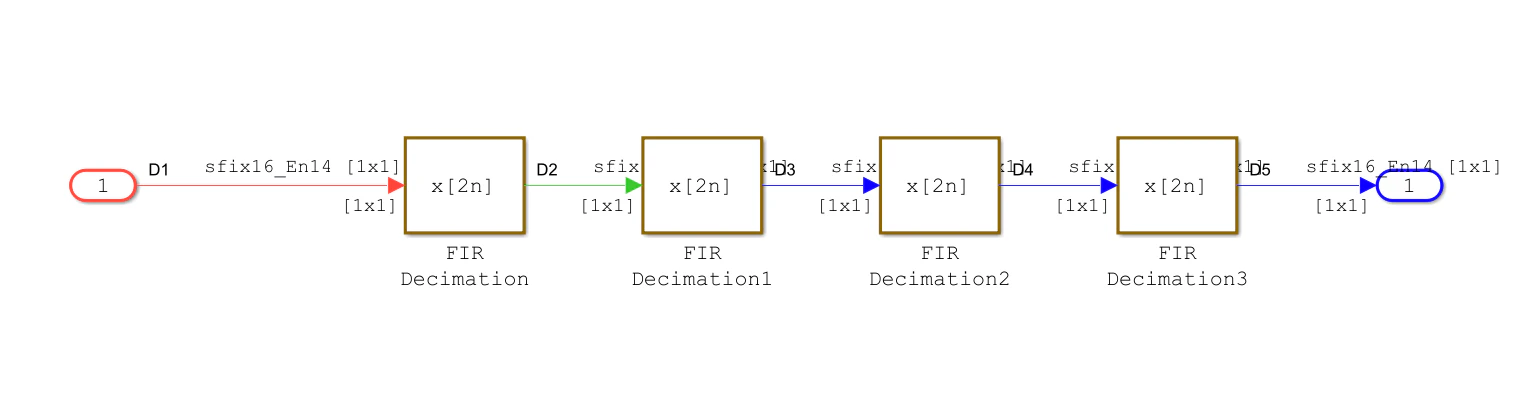

このような場合、フィルタを多段に分割することで、リソース消費量を大きく減らすことが出来ます。

例えば、サンプリングのレートを1/50にする場合を考えます。

この時、1ステージで1/50とするよりも、1/5⇒1/5⇒1/2とすることで、リソース消費量を減らすことが出来ます。

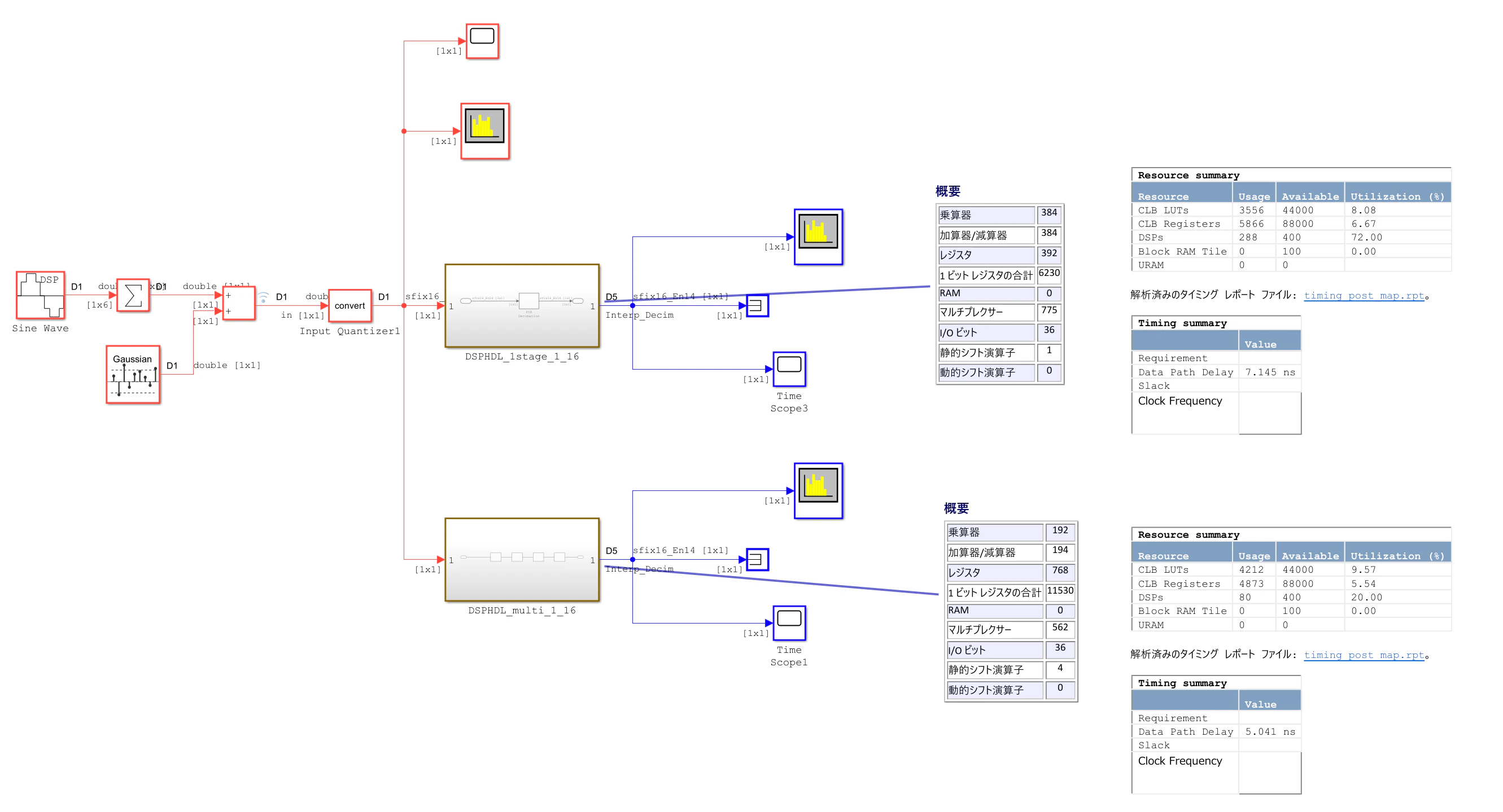

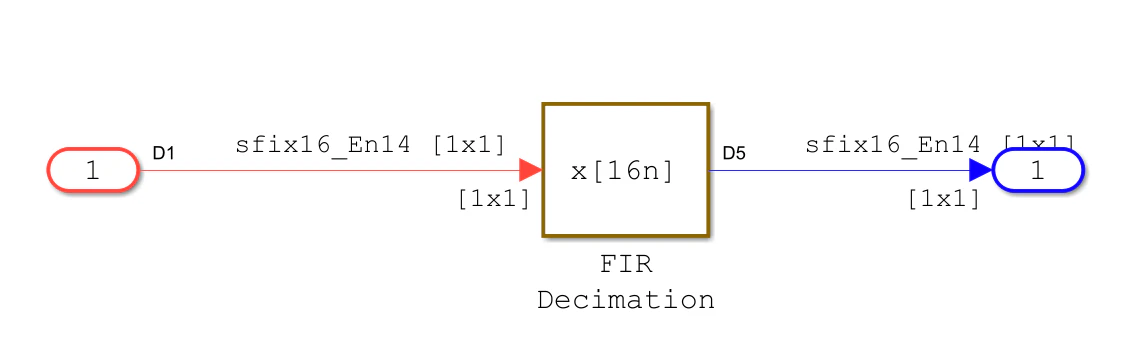

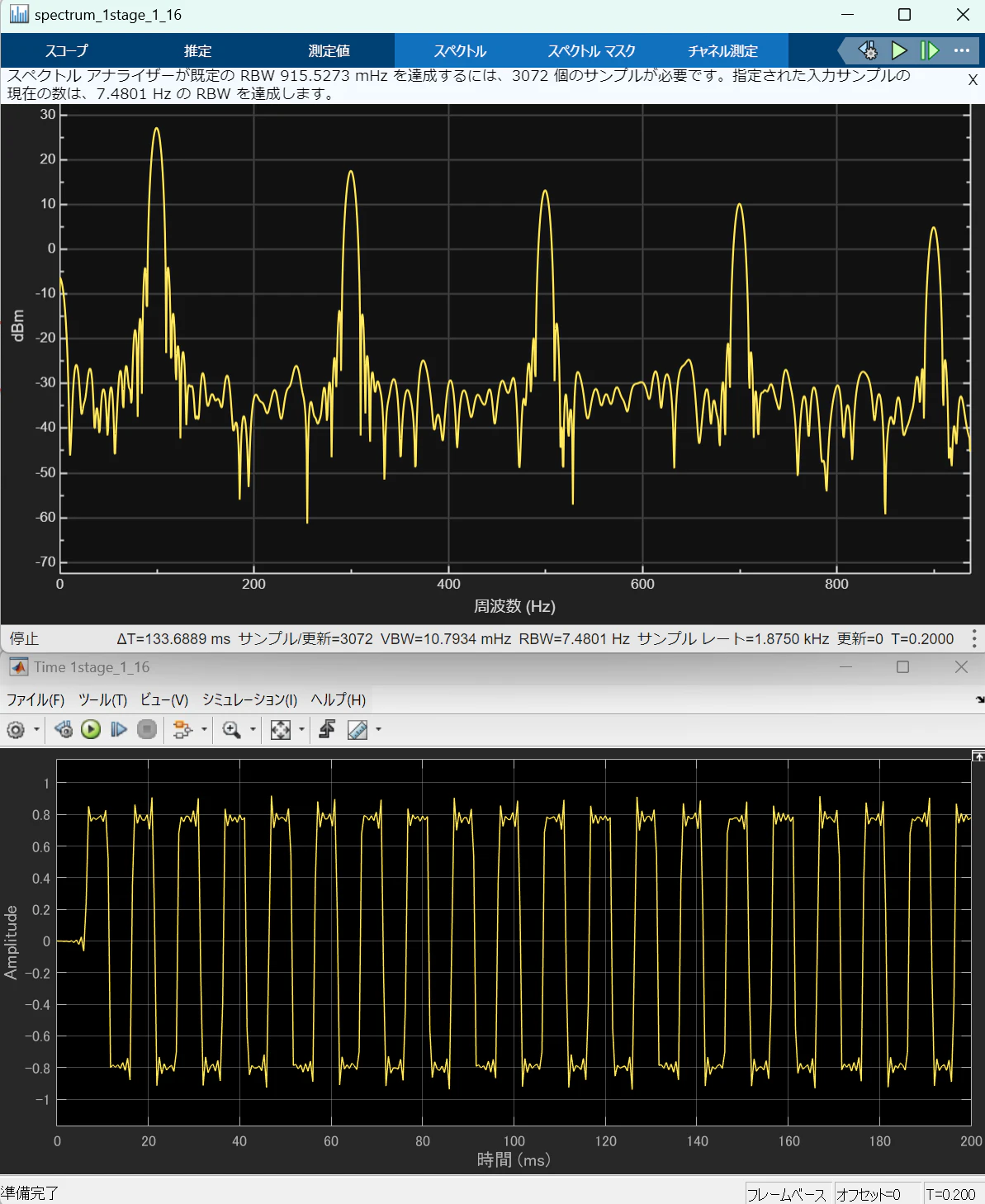

Simulinkにて、Decimationというブロックがあるので、こちらを使って単純比較してみました。

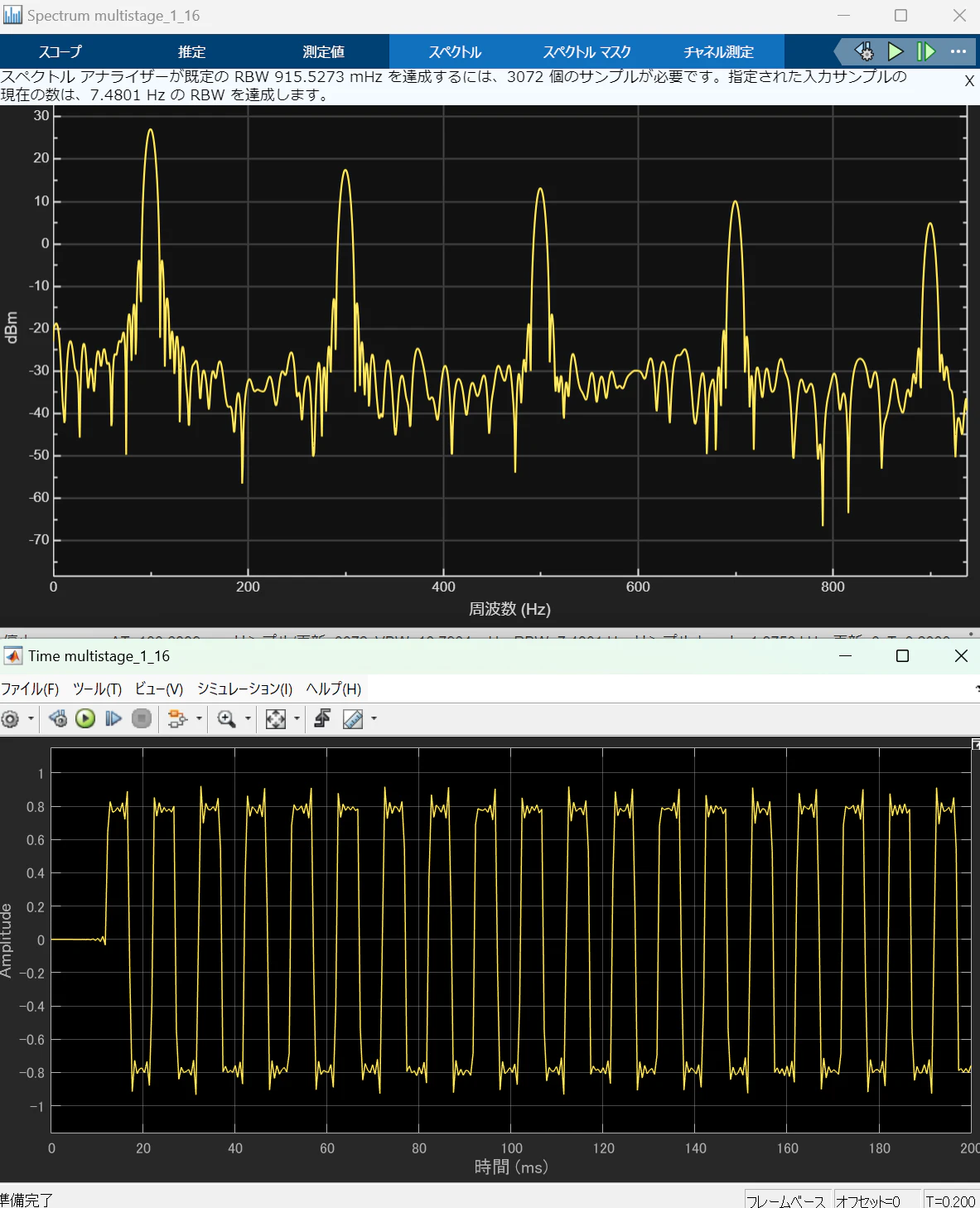

結果を見ると、なにも考えず縦に分割して繋いだだけでも、同じような特性が出ていることが分かります。

合成した結果を抜き出すと、下記の通りとなりました。

| Resource | Usage(1stage) | Usage(Multistage) |

|---|---|---|

| CLB LUTs | 3556 | 4212 |

| CLB Registers | 5866 | 4873 |

| DSPs | 288 | 80 |

| Block RAM Tile | 0 | 0 |

| URAM | 0 | 0 |

結果を見ると、特にDSPの消費量を大きく抑えられていることが分かりました。

一方、LUTの消費量は増大しているようです。DSPの代わりにロジックブロックが割り当たっているのかもしれません。