1. 概要

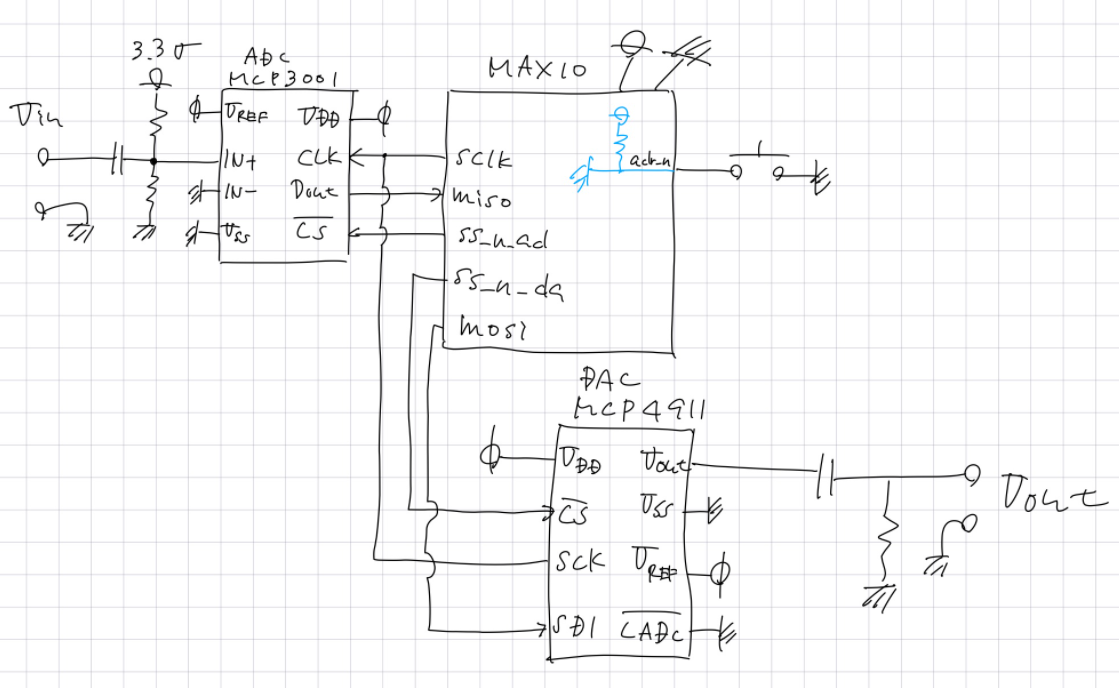

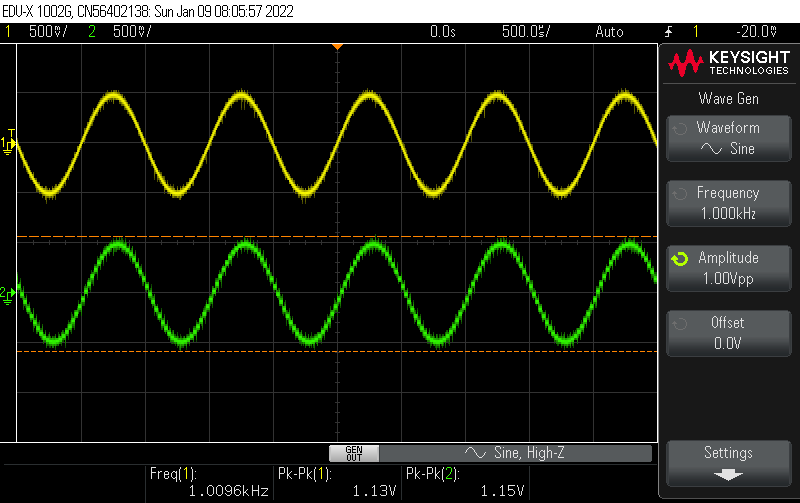

今度はADC MCP3001とDAC MCP4911とを同時に動かす。アナログ信号をAD変換してFPGAに取り込み、FPGAの内部では何もせずにDA変換して出力する。

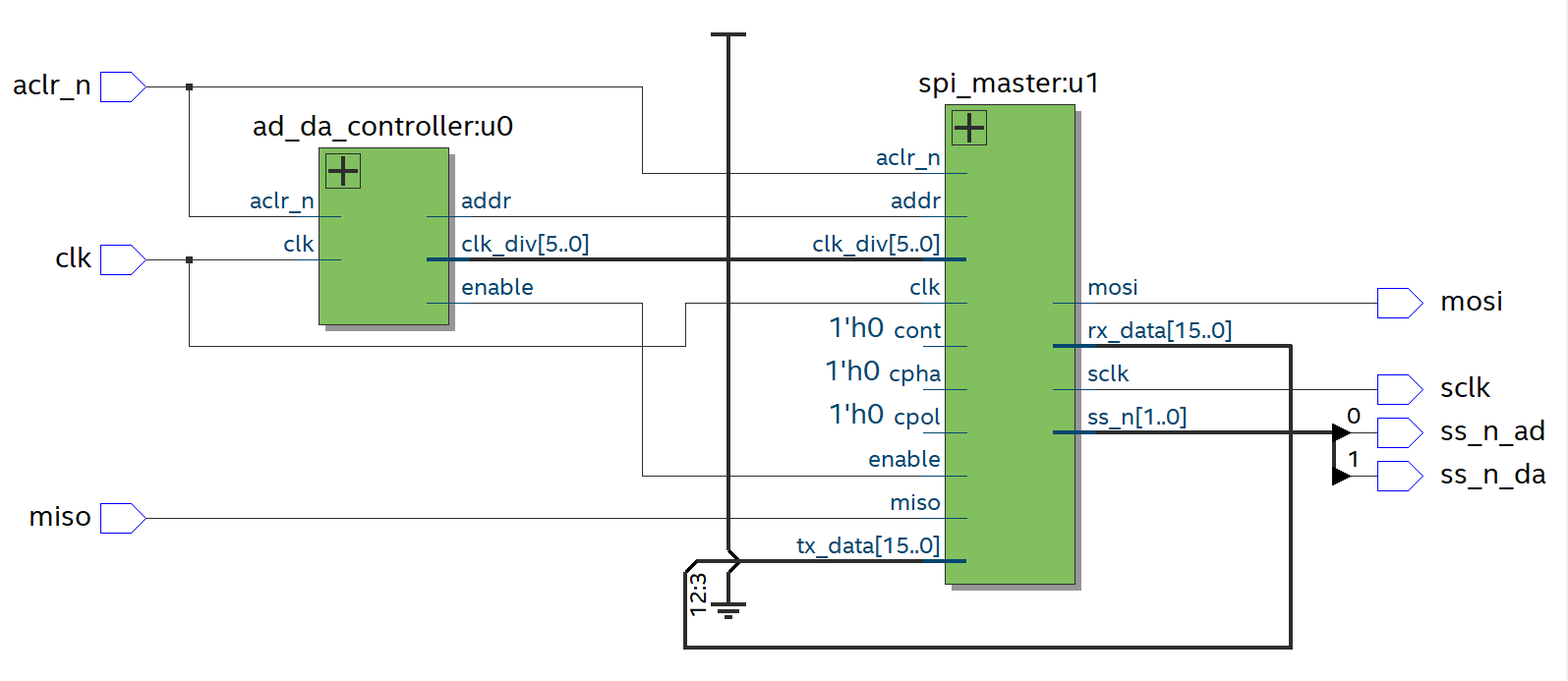

2. ADC MCP3001とDAC MCP4911とを同時に動かすためのVHDL

下のVHDLをコンパイルしてMAX10 FPGAに書き込む。

ファイル一式: https://github.com/ti-nspire/VHDL_for_Quartus_Prime/tree/main/AD_DA_MCP3001_4911_ver_2