Vitisの紹介

ザイリンクス社から、Vitis(ヴィティス)という、開発ツールが2019年10月に発表されました。

ソフトウェア技術者でも、FPGA開発を、、というのを目標に、開発されたツールで、Linux上のアプリケーションを記述する感覚で、設計できるのが特徴です。また、ハードウェア特有の動作の高速化もVitis上で設計できるため、今まで以上に一体感のあった、システム設計ができるのが大きな特徴になります。

Vitisプラットフォーム

Vitis自身はとても、便利な機能も多くて、使いやすいのですが、予め、プラットフォームというものを、用意しないと動作できないことになりました。

ザイリンクス社からは、自社製品のプラットフォームが提供されていますが、残念ながら、Ultra96はAvnet社製のため、後回しにされたようです。

ここでは、Ultra96向けプラットフォームの作り方をご紹介します。

プラットフォームは3種類用意する予定で、

1:BASE 本当に基本だけのプラットフォームの作成。とりあえずVitisプラットフォームの基本と、Vitisを動かしたい人向け

2:OOB Ultra96V2向けのWifi等ドライバーやアプリケーションを含んだバージョンの作成

3:OOB-AI 上記2の機能にVitis AIで動作するためのプラットフォームの作成

を用意する予定です。

今回は、BASE編でこれだけあれば、とりあえずプラットフォームができる、、というレベルで、Ultra96の機能はほとんど使っていません。

ただ、作り方の基本は学べると思っています。

必要な開発環境

VitisとPetalinuxが必要となります。私の方でも、開発環境の設定の仕方を記述しましたので、参考にしていただければと思います。

Ultra96の開発環境(Vitis2019.2版)

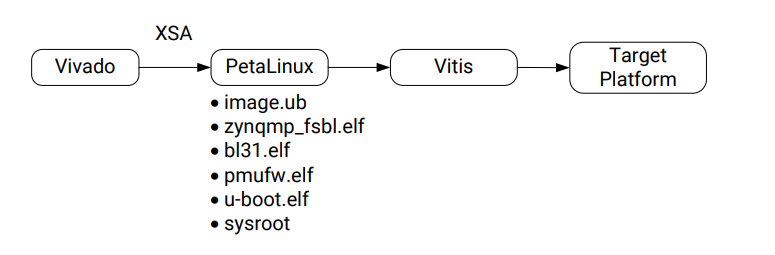

Vitisプラットフォームの作成手順

大きく分けて次の動作が必要になります。

1:Vivadoでハードウェアを作成する。

2:Petalinuxで、Linuxカーネルと、sdkを作る

3:Vitisで、プラットフォームをつくる

4:Vitisで動作チェック

Vivado での設計(ハードウェアの設計)

Vitisプラットフォームは以前のツールである、SDSoCの作り方とほぼ同等になります。

必要なものは決まっていて、それを最低限組みます。また、今回は行いませんが、追加のIP(設計)も可能で、

予め固定のハードウェアを最初からのせることも可能になっています。

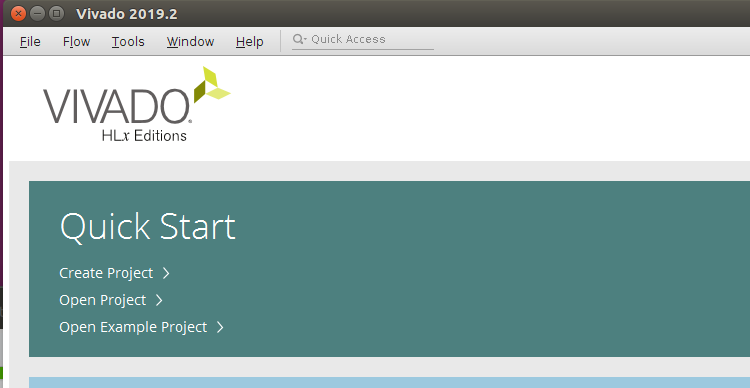

まずは、Vivadoを立ち上げます。 私は、コマンドプロンプトから立ち上げています。

vivado

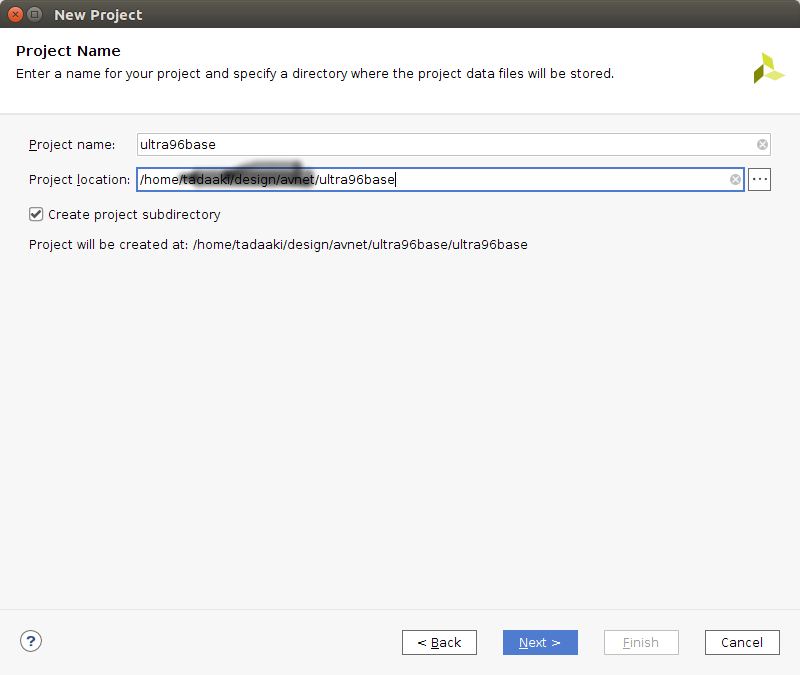

新規プロジェクトの作成

まずは、新規作成から、行います。Vivadoを立ち上げてから、Quick Start の Create Project で新しいプロジェクトを作ります。

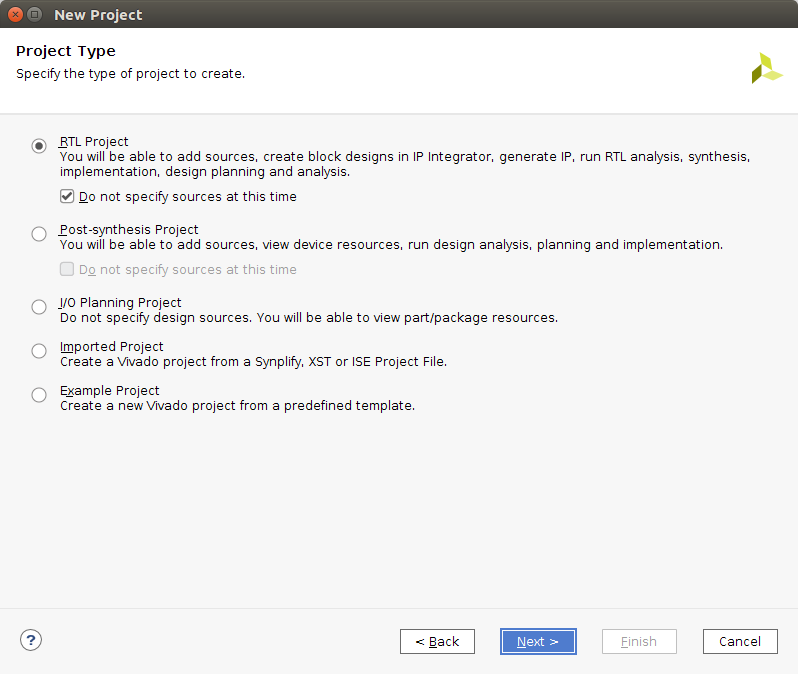

新規プロジェクトを作りましたら、Nextを押して、プロジェクト名を決めます。ここでは、Vitisで使いやすい名前にしておいたほうが、望ましいです。

次のProject Typeでは、RTL Projectを選択、Do not specify sources at this time にチェックを入れてNextです。

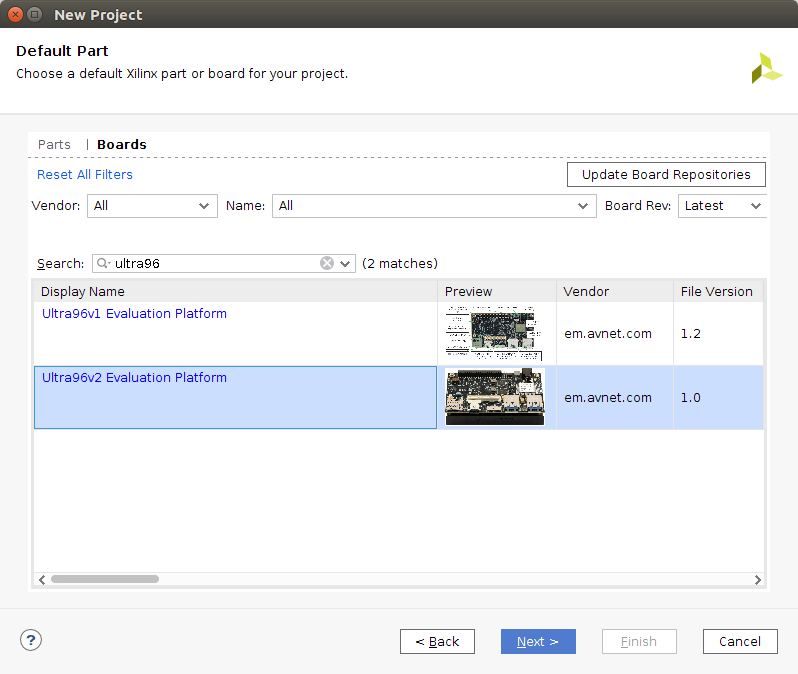

パーツまたは、ボードを選択します。

開発ツールのインストール時に、BDFファイルを設定している方は、Ultra96がボードとして、選択できますので、それを使うと便利です。

また、他のボードでも使えます。今回はUltra96V2を選択しました。

まず、Board タブを選択してから、Ultra96V2を探します。 Serch機能がありますので、Ultra96と打ってから、サーチをかけると簡単に見つかります。必要なボードをクリックします。

終わりましたら、Nextを押して、最後にFinishで、新たなプロジェクトが完成します。

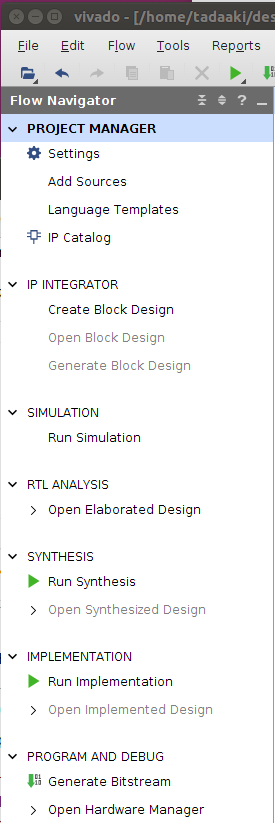

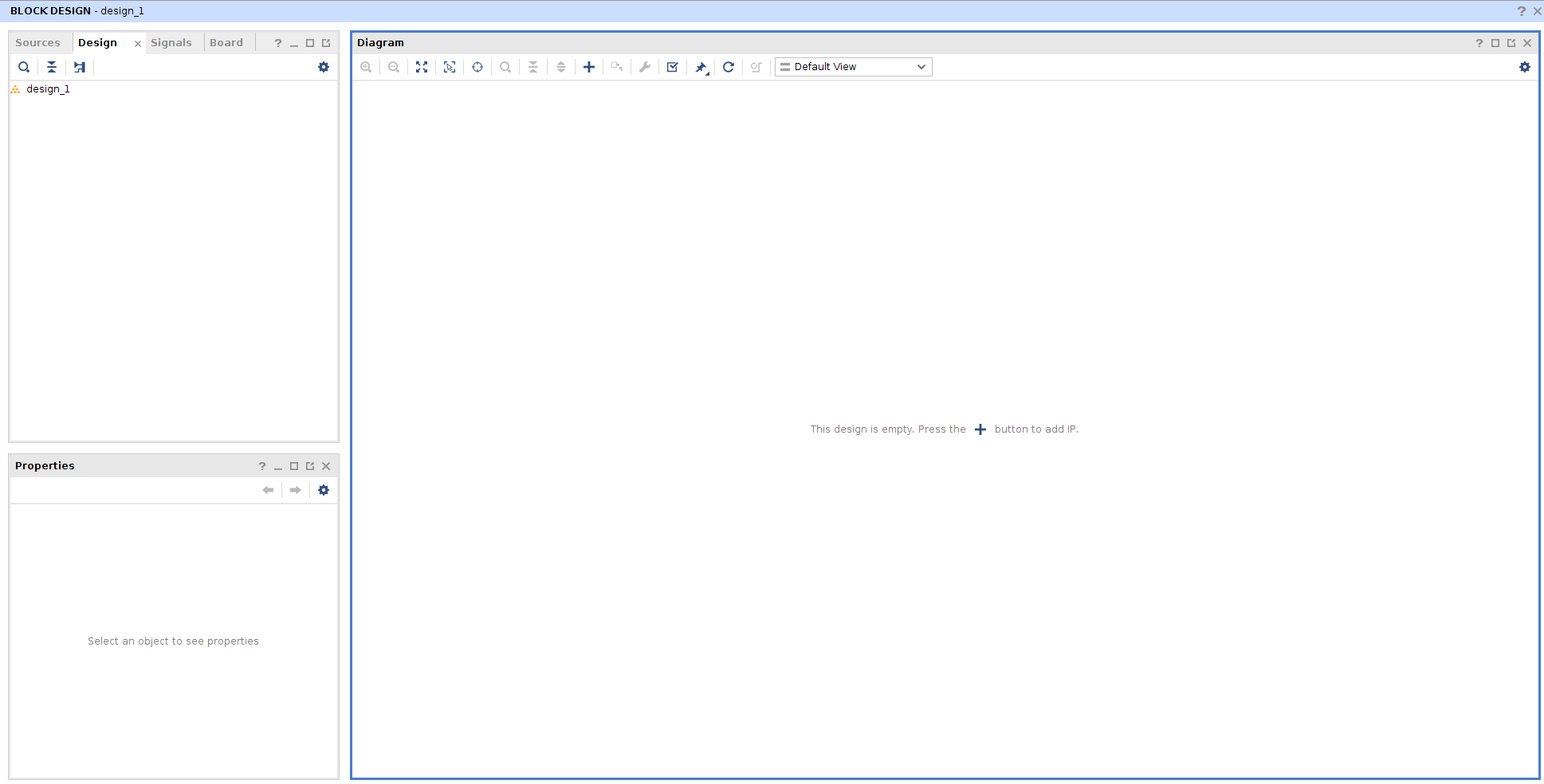

ブロックデザインの作成、設計

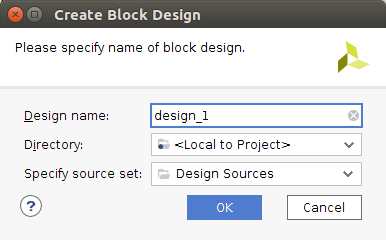

次に、ブロックデザインを作ります。

Flow Navigator→IP ITEGRATOR → Create Block Design から始めます。

次にブロックデザインの名前を決めて、OKです。デフォルトでも大丈夫です。

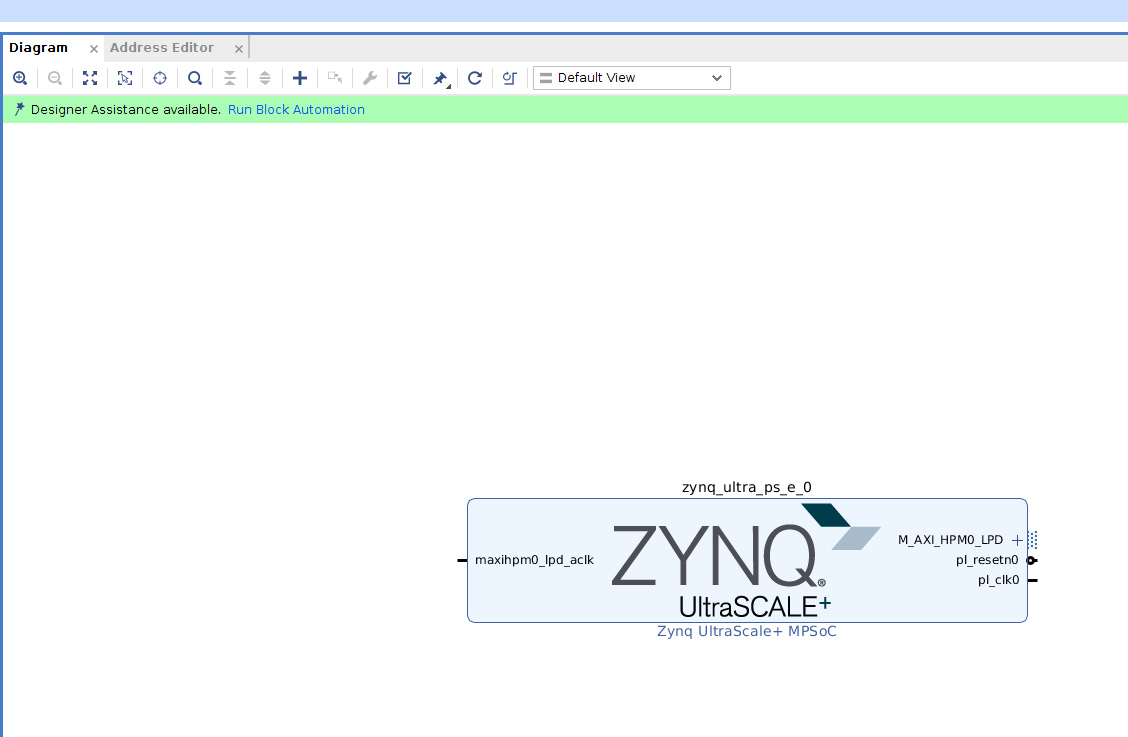

キャンパスができてきます。ここで、必要なブロックの追加、配線を行います。

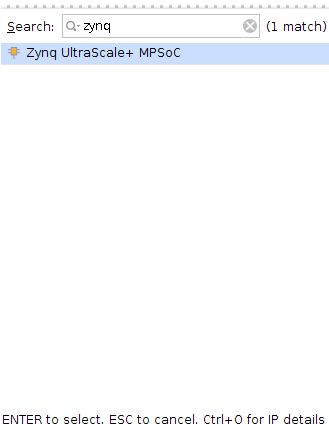

ブロックの追加は、+のアイコンを叩くか、キャンパス上で、マウスを右クリックすると、Add IPと出てきますので、それで選択します。

IP(ブロック)の数は多いので、検索を使うと便利です。ここでは、zynq と入力しまして、出てきたものに、ダブルクリックでキャンパスに置きます。

zynqが置かれましたら、緑のバーにある、Run Block Automation をクリックします。これで、Ultra96向けのZynq UltraScale+ MPSoCの基本的な設定を終わります。なにか聞いてきましたら、デフォルトでOKなので、そのままOKを押してください。

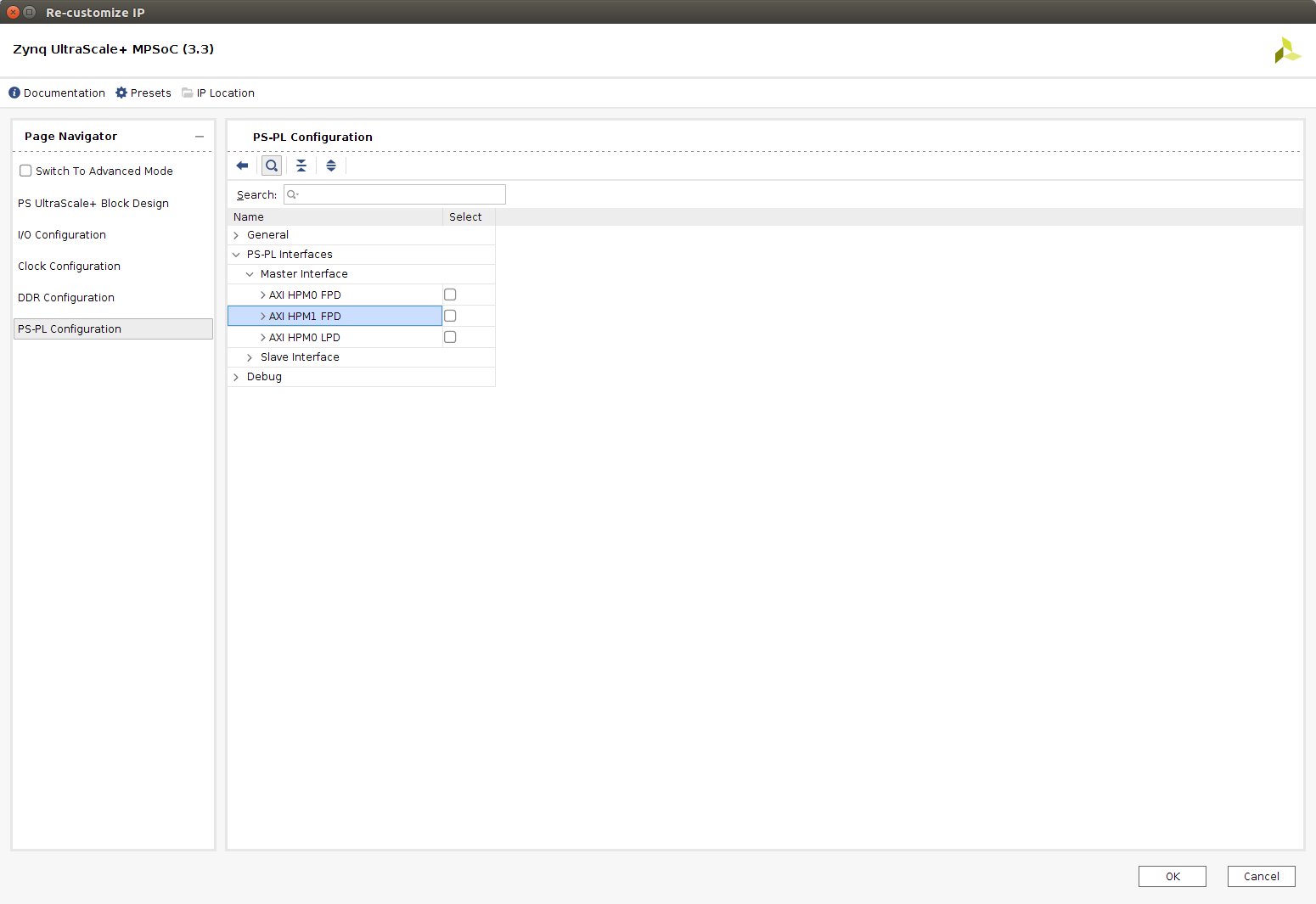

次に不要なAXIポートを削除します。

zynq_ultrascale_ps_eをダブルクリック、Page Navigatorで、PS-PL Configurationをクリックします。PS-PL Interfaces と Master Interfaceを展開して、AXI HPM0 FPD と AXI HPM1FPD のチェックを外して、OKを押します。

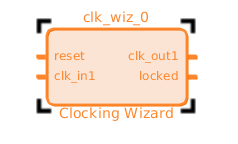

次に、クロックのブロックを追加します。

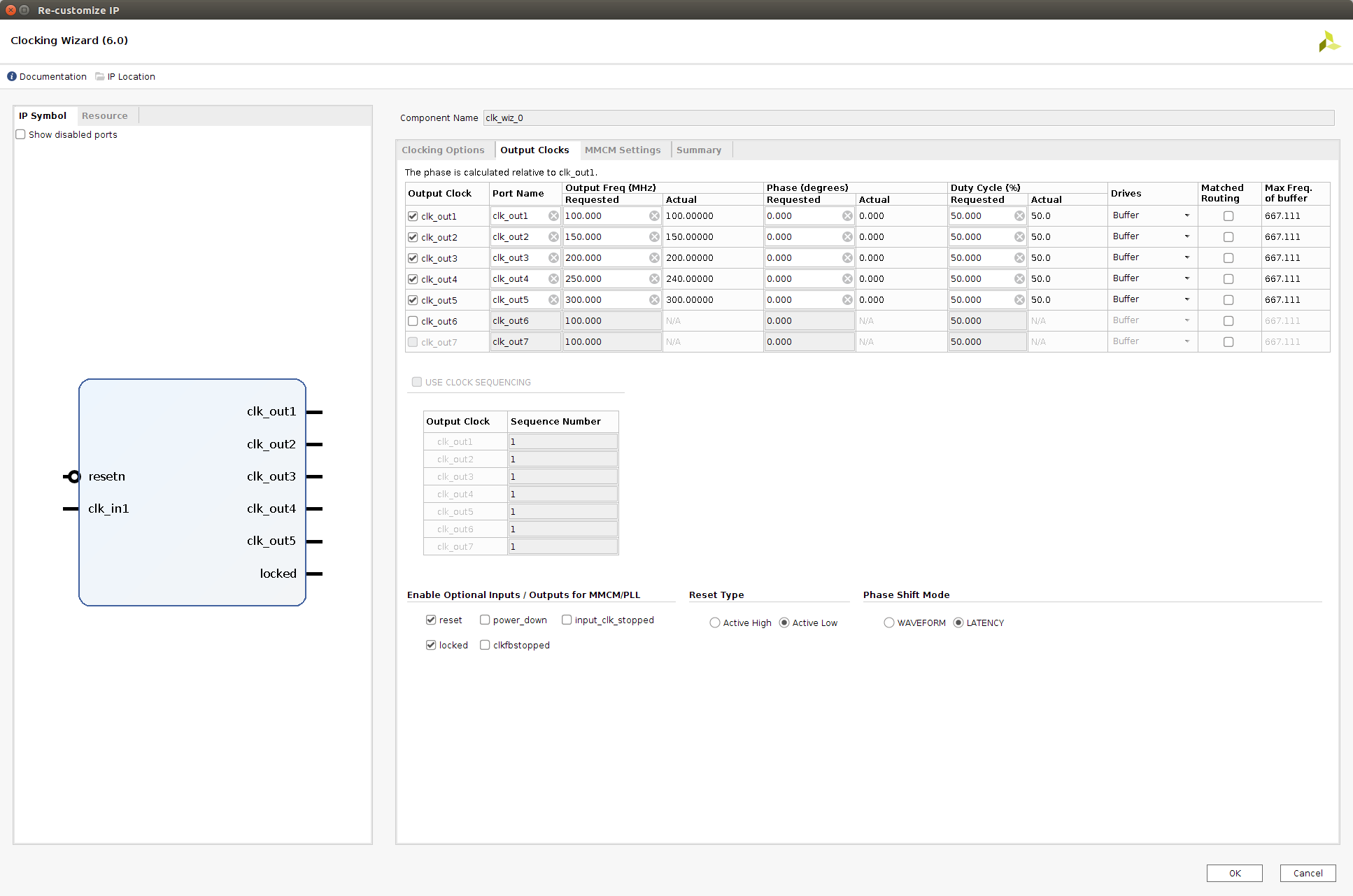

マウス右クリックのAdd IP(または+のアイコン)をクリックして、Serchにclock と入力 その中の Clocking Wizardを選択し、ダブルクリックします。この中にはPLLが入っており、クロックの変換を行ってくれます。出てきた、clk_wiz_0をダブルクリックして、出力周波数の設定を行います。

クロックは適当に設定します。Output Clockタブをクロックします。今回は5つ、100MHzから50MHz刻みで、300MHzまで出力設定しました。ここはお好みで大丈夫です。ただ、後で、Vitisでのクロックに影響してきます。

リセットの関係上Reset tpyeは、Active Lowにします。

そのほかはデフォルトでOKです。

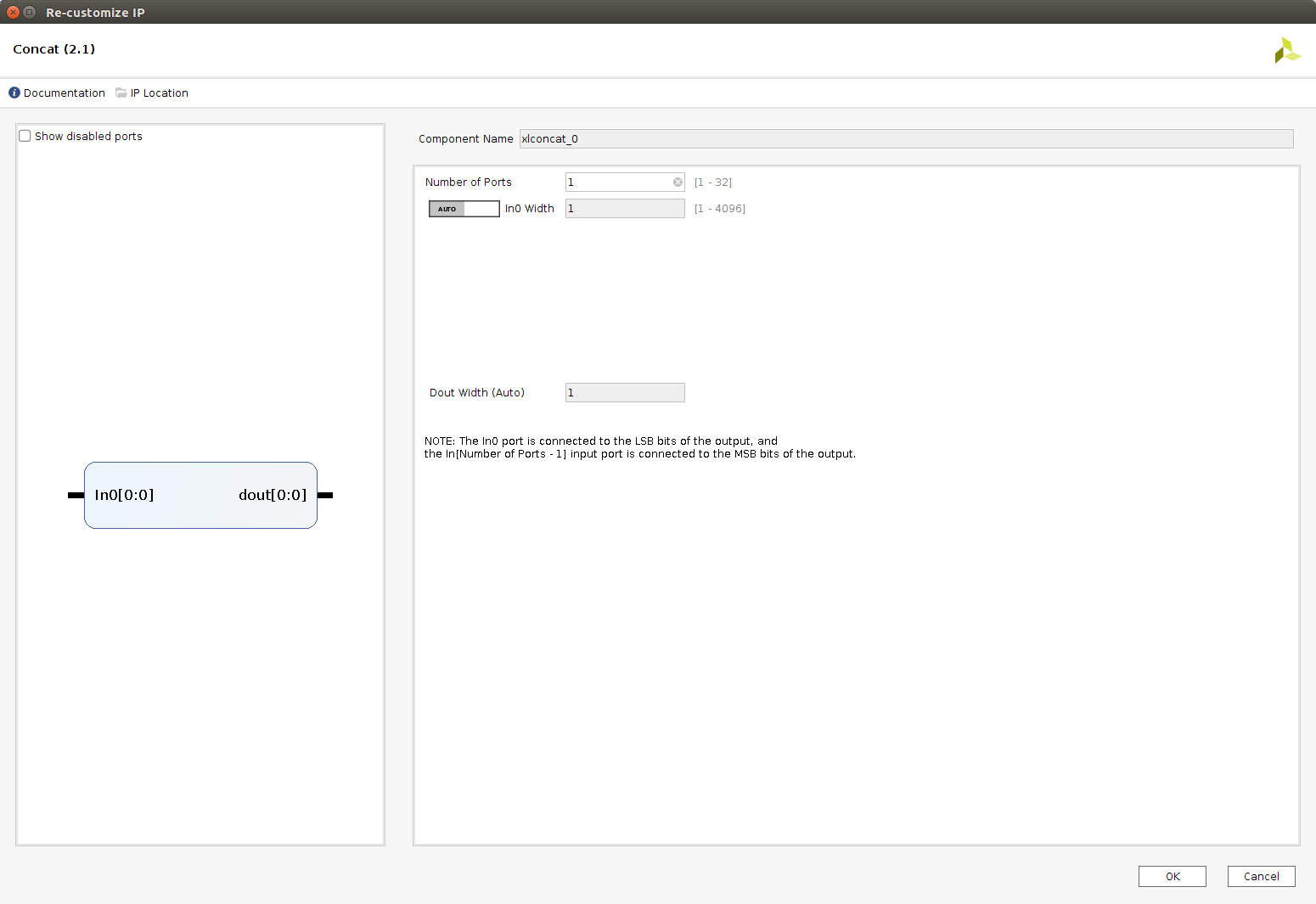

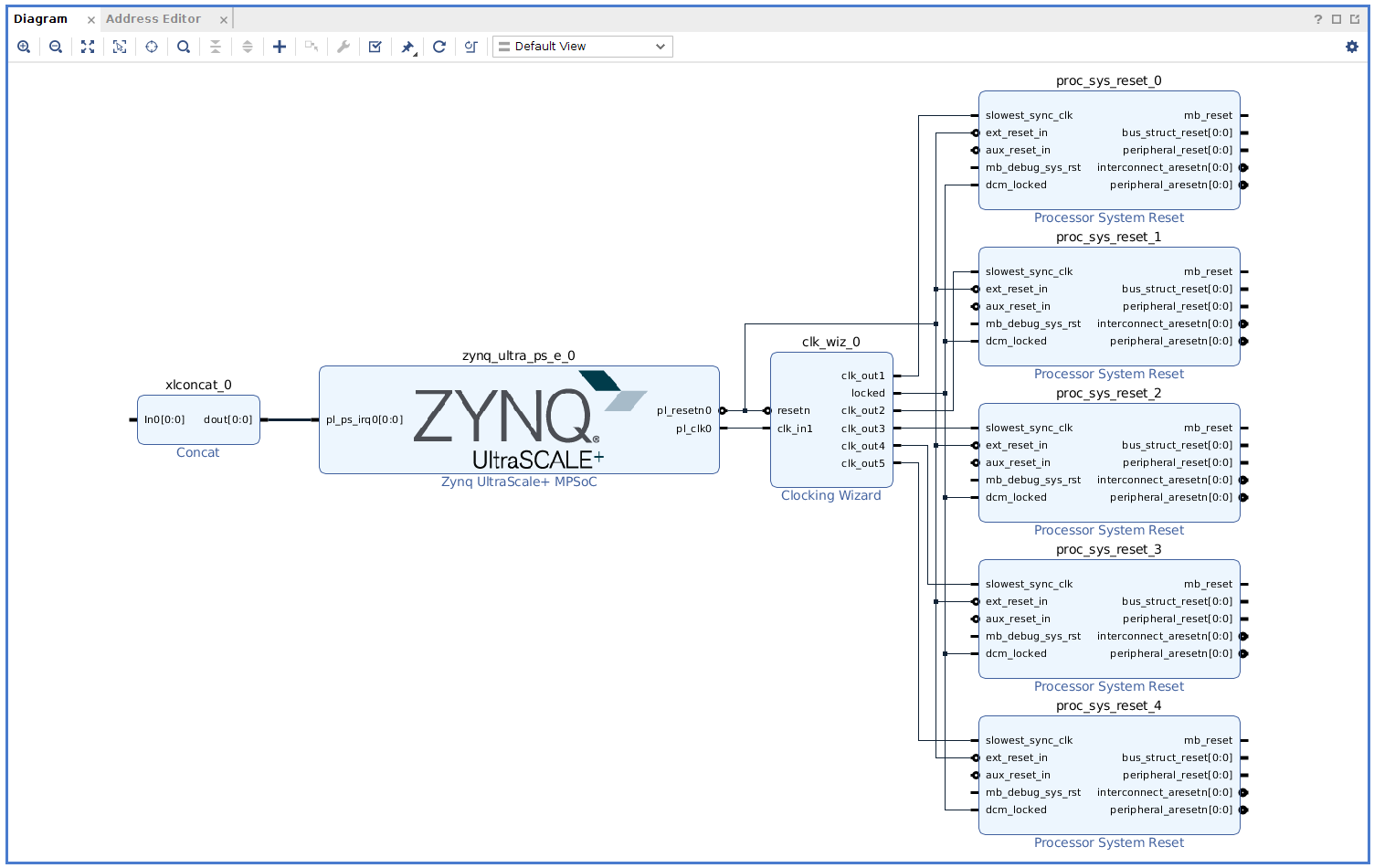

次に、リセットをクロックの数だけ設定します。Add IPをつかってseach で reset で見つかる、 Processer System Reset を選択します。今回はクロックを5つ設定したので、5個用意します。また割り込みの拡張のためConcatというIPも追加します。Concatはダブルクリックして、Number of Portを1にします。(図はConcatをダブルクリックして設定した時)

配線をします。

zynq_ultra_ps_e_0のpl_reset0とpl_clk0をそれぞれ、clkwiz_0のresetn、clk_in1に配線します。

clk_wiz_0の各クロック出力を、各Proc_sys_resetのslowest_sync_clkに配線します。

clk_wiz_0のlockedを各、proc_sys_resetのdcm_lockedに配線します。

zynq_ultra_ps_e_0のpl_reset0を各proc_sys_resetのext_reset_inに配線します。

xlconcat_0のdout[0:0]をpl_ps_irq[0:0]に配線します。

Vitis側で割り込みが行えるように設定します。

配線が終わり、Regenelate Layoutのアイコン  をクロックしたものが次のブロックになります。

をクロックしたものが次のブロックになります。

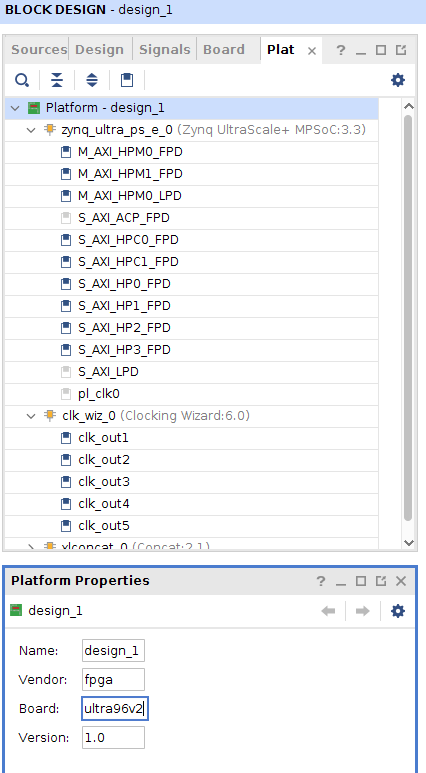

プラットフォーム(PFM)インターフェースとプロパティーの定義

Vitisで使えるインターフェースをここで、定義しておきます。

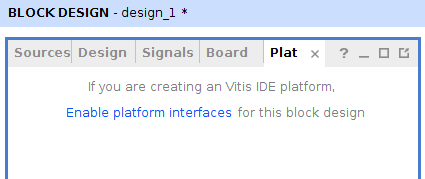

メニューの Window → Platform Interface をクリックして、プラットフォームの設定を行います。

Enable platform Interfaces をクリックして、プラットフォームを設定できるようにします。

Vitisのプラットフォームでわかりやすいようにboardの名前を変更します。

Platformを選択して、下の方のBoard:をUltra96v2に変更しました。

使えるインターフェース、ポートを定義します。各ポートはマウスの右クリックで、メニューがでます。ダブルクリックでも、Enable,Disenableの切り替えができます。

zynq_ultra_ps_e_0では、次のインターフェス、ポートをEnableにします。(それ以外はDienable)

M_AXI_HPM0_FPD

M_AXI_HPM1_FPD

M_AXI_HPM0_LPD

S_AXI_HPC0_FPD

S_AXI_HPC1_FPD

S_AXI_HP0_FPD

S_AXI_HP1_FPD

S_AXI_HP2_FPD

S_AXI_HP3_FPD

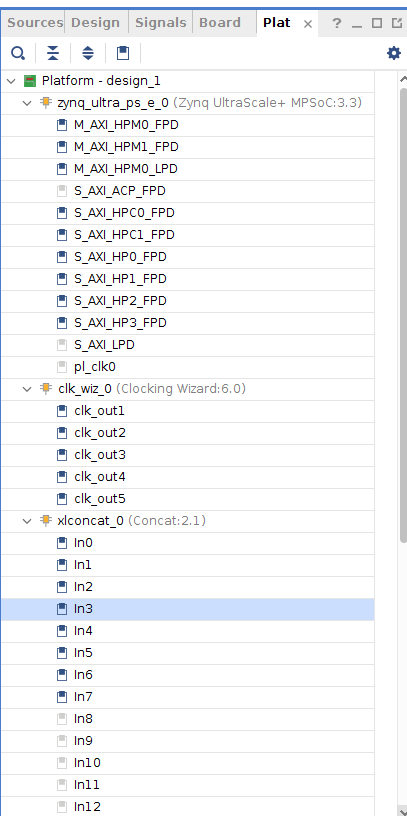

clk_wiz_0については全部Enableにします。

xlconcat_0については、In0〜In7までをEnableにします。

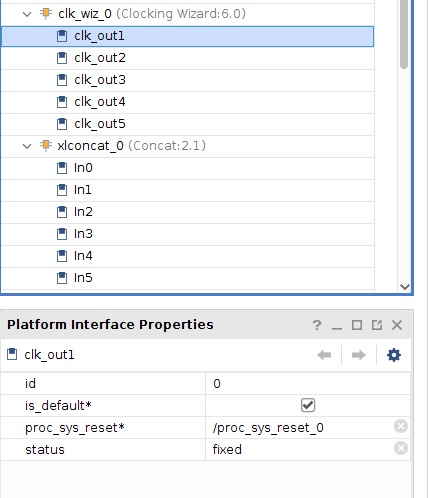

クロックにデフォルトを与えます。どこかひとつのクロックをデフォルトにする必要があります。

clk_out1を選択後、Platform Interface Properties の中の Optionsのタブをクリックして、is_defaultを選択します。また、idを0にします。Vitisで使用できる、デフォルトのクロックです。

次にXRT用の設定を行います。Tclコンソールにつぎのコマンドを入力します。TclコンソールはVivadoの下の方にTcl Consoleというタブがありますので、それをクリック、その中で、type a Tcl command here と薄くかいたボックスがありますので、そこに1行づつ入れていきます。

set_property platform.design_intent.embedded true [current_project]

set_property platform.design_intent.server_managed false [current_project]

set_property platform.design_intent.external_host false [current_project]

set_property platform.design_intent.datacenter false [current_project]

set_property platform.default_output_type "sd_card" [current_project]

Vilitate Design( のアイコン)をクリックして、間違えないかをチェックします。

のアイコン)をクリックして、間違えないかをチェックします。

OKが出たら、問題がありません。エラーが出たら、直してください。

ビットストリームの作成、XSAファイルのエクスポート(出力)

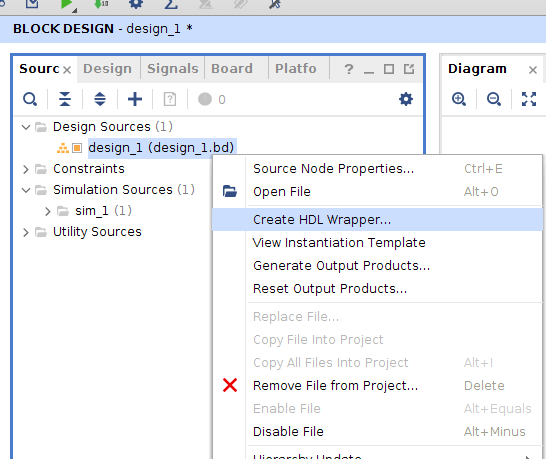

次に、最上位ファイルを作成します。Sourceタブの中のdesign_1を右クリック メニューから、Create HDL Wrapperを選択して、トップファイルを作ります。きかれたら、OKを押します。

その後、Flow Navigatorの Generate Bitstreamをクリックします。ここで、ビットストリームを作ります。

ダイアログがいくつか出ますが、Save Yes Okの順でクリックすれば大丈夫です。

ここで、数十分かかります。

最後に終わりましたら、Cancelを押してください。

次にエクスポート(出力)します。

現在のところ、TCLコマンドでの運用になります。(2020.May.2 訂正)

write_hw_platform -include_bit <Write Path>/ultra96base.xsa

ハードウェアの最後は出力したファイルのチェックです。TCLコマンドで行います。

validate_hw_platform <Write Path>/ultra96base.xsa

これで、ハードウェアの部分が終わりです。

Petalinux でのビルド

今度はLinuxシステムを設計します。

こちらでは、Ultra96の基本の機能と、Vitisで使われる、機能を作成します。

作るのは、BSPとSDKのファイルを作る必要があります。

Petalinuxの動作環境を整えた状態で、すすめてください。

プロジェクト作成とコンフィグレーション

まず、Petalinux用のプロジェクトを作成します。その後、ディレクトリーに移動します。

petalinux-create -t project -n petalinux --template zynqMP

cd petalinux

次に、各種設定を行います。ここで、Vivadoで作成したファイルを取り込みます。ディレクトリーはXSAファイルのある場所に変更してください。ファイル名までは指定しなくていいです。

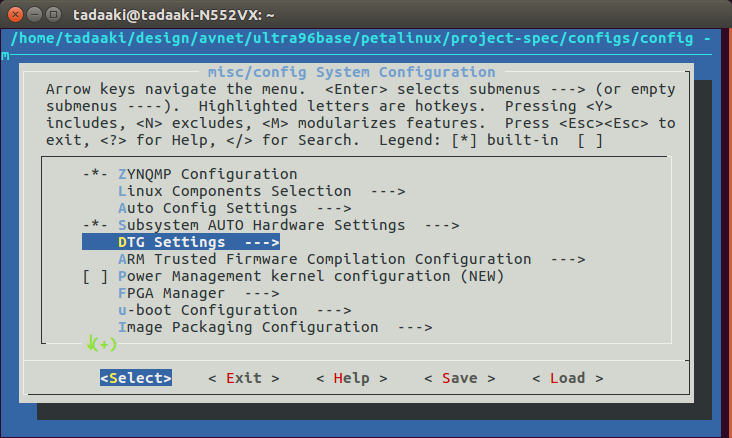

petalinux-config --get-hw-description=../ultra96base

少し時間が経つとコンソールによるメニュー形式が出てきます。キーボード上の矢印で項目を移動してください。

ここで、いくつかの設定をします。

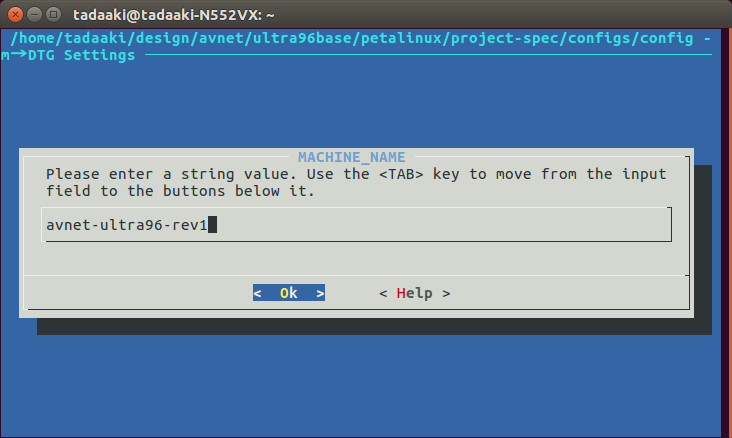

まずは、MACHINE NAMEの設定です。 DTG Settngs → MACHINE_NAME を選択して、 avnet-ultra96-rev1 に書き換えてください。全部ではないのですが、Ultra96のすでに入っている設定が反映されます。終わりましたら。OKにカーソルを合わせ、次にExitでトップ画面に移ります。

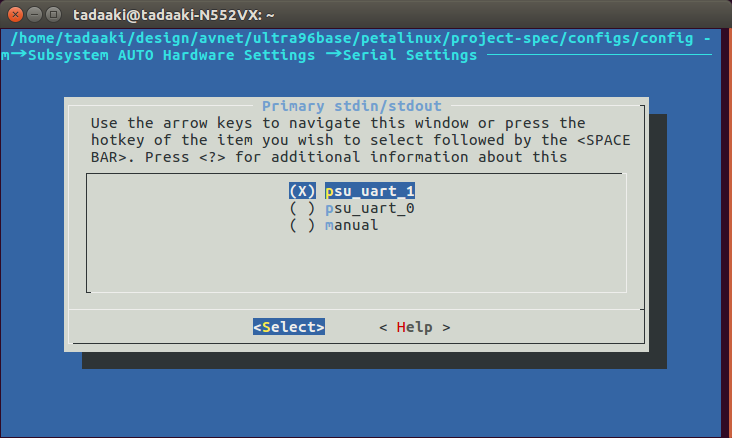

Uartの設定をUltra96向けに変更します。これは、Ultra96のUARTがBluetoothにも使われているため、そこを正しく設定するためです。メニューのトップから、Subsystem AUTO Hardware Settings → Serial Settings を設定、その後、psu_uart_1に設定します。スペースバーを押すと設定が終わります。

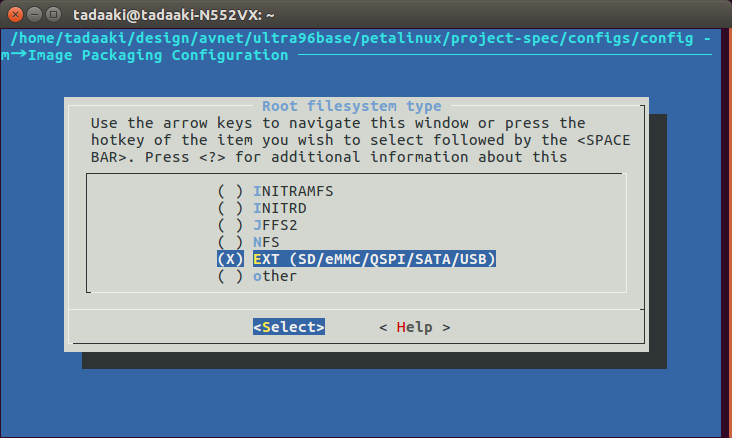

次にシステムを増やすために、SDカードの記録方法を指定します。トップメニューから、Image Packageing Configuration → Root filesystem type からEXT(SD/eMMC/QSPI/STAT/USB)を選択します。

ここではSelect後Exitを2回、その後、保存しますかを聞いてくるので、Yesを押します。ここで、すこし時間が取られます。

次に、XRTを使えるようにするため、追加ファイルを設定します。次のファイルを編集します。./ project-spec/meta-user/conf/user-rootfsconfig 適当なエディターを使ってください。 geditなら標準でついてきます。

ファイルは次のようになります。

# Note: Mention Each package in individual line

# These packages will get added into rootfs menu entry

CONFIG_gpio-demo

CONFIG_peekpoke

CONFIG_xrt

CONFIG_xrt-dev

CONFIG_zocl

CONFIG_opencl-clhpp-dev

CONFIG_opencl-headers-dev

CONFIG_packagegroup-petalinux-opencv

デバイスツリーを編集します。 ./project-spec/meta-user/recipes-bsp/device-tree/files/system-user.dtsi

を次のように編集してください。これはZynqシリーズで、XRTドライバーが使えるようにするためです。

/include/ "system-conf.dtsi"

/ {

};

&amba {

zyxclmm_drm {

compatible = "xlnx,zocl";

status = "okay";

};

};

次に先ほど設定したファイルを有効視します。

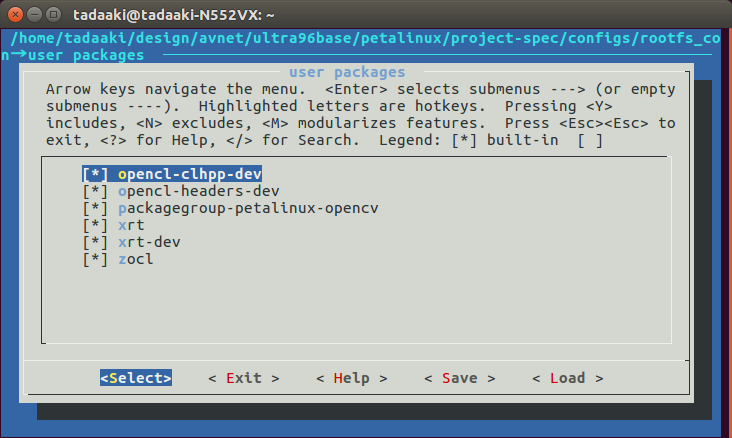

petalinux-cofing -c rootfs を実行して、有効なファイルを設定します。

petalinux-config -c rootfs

その後、user packages を選択して、出ているプログラムをすべて有効にします。

2回Exitで、セーブして、Yesで保存します。

DMA転送用のメモリーを確保します。カーネルの操作をします。

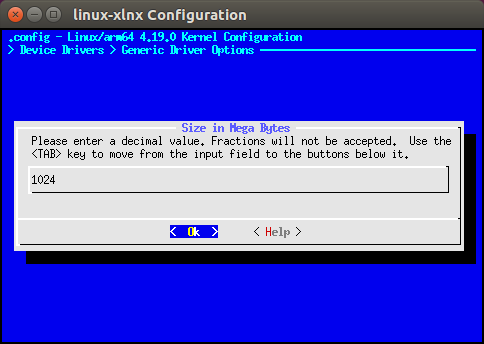

petalinux-config -c kernel

Device Drivers→ Generic Driver Options→ DMA Contiguous Memory Allocator → Size in Mega Bytes

をクリックして、256を1024に変更します。

終了して、保存して、終わります。

ここまでで、コンフィグレーションの設定は終わりです。

ビルド

ここでは、2箇所ビルドをします。かなり時間がかかるところなので、気長に待ってください。

今回は行いませんが、ひとつ目のビルドが終わった時点で、Petalinux-packgeを使って、

BOOT.BINファイルを作成して、SDカードにコピーすれば、Ultra96が動作できます。

petalinux-build

cd images/linux

petalinux-build --sdk

cd ../../..

おわりましたら、sdk.shができています。

これは、自己解凍のファイルです。

これを解凍して、Vitisのプラットフォーム作りのsysrootにします。

次のようにしました。

mkdir pfm

./petalinux/images/linux/sdk.sh

出力パスを聞いてきますので、したい場所を指定します。

私は[save full path]/pfm にしました。

この場所は覚えておいてください。

ブートに使うファイルのコピーを行います。

mkdir boot

cd petalinux/images/linux

cp image.ub zynqmp_fsbl.elf pmufw.elf bl31.elf u-boot.elf ../../../boot

cd ../../..

BIFファイルの作成

BIFファイルはSDカードを作るときに必要となります。

これは、テキストファイルをそのまま作成します。boot/linux.bif として作成します。

/* linux */

the_ROM_image:

{

[fsbl_config] a53_x64

[bootloader] <zynqmp_fsbl.elf>

[pmufw_image] <pmufw.elf>

[destination_device=pl] <bitstream>

[destination_cpu=a53-0, exception_level=el-3, trustzone] <bl31.elf>

[destination_cpu=a53-0, exception_level=el-2] <u-boot.elf>

}

Vitisプラットフォームの作成

今まで作成したファイルを元にして、Vitisのプラットフォームを作成します。プラットフォームはVitisが作成します。

cd ./pfm

vitis -workspace wksp1

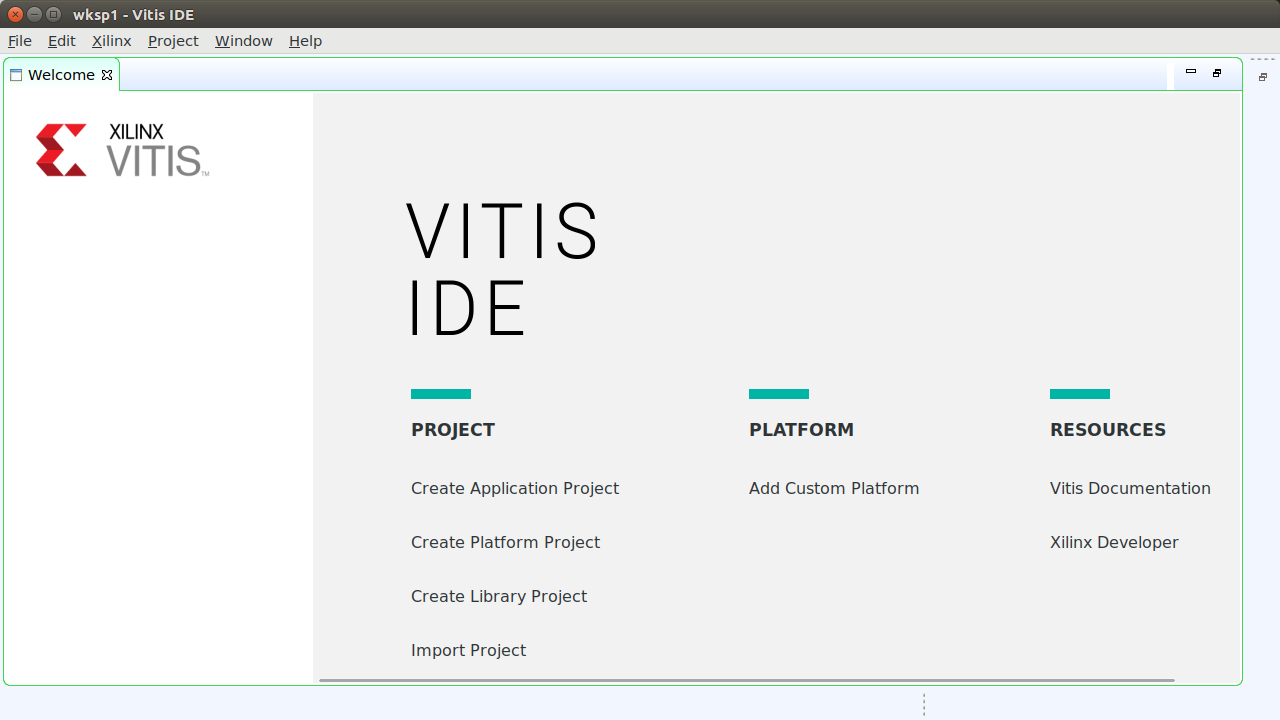

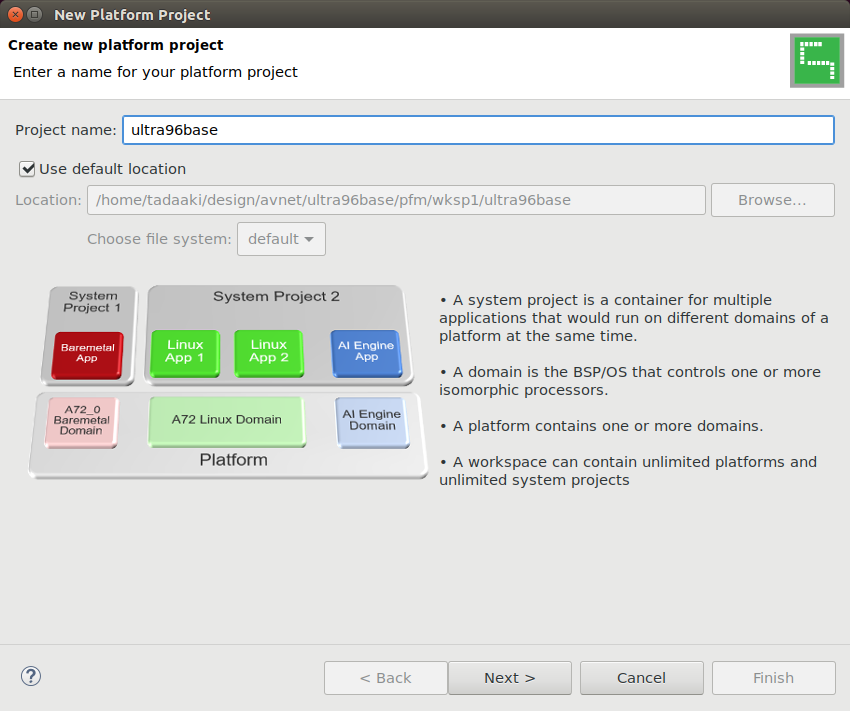

Vitisが立ち上がりましたら、Create Platform Project を選択します。(またはメニューから File → New → Platform Project でもいいです)

次の画面でプラッフォフォーム名を入れます。場所も指定できます。今回はultra96baseにしました。

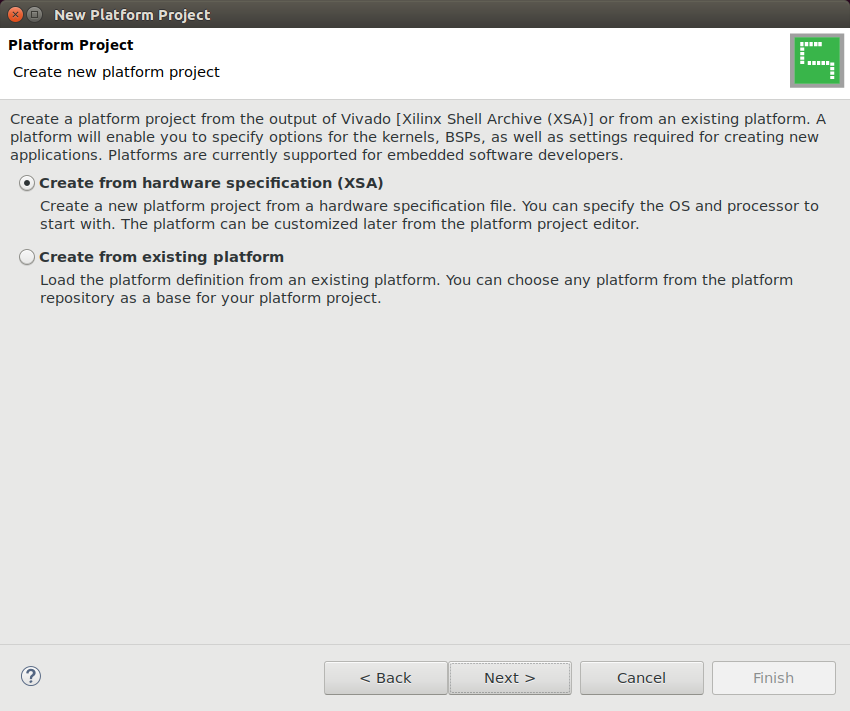

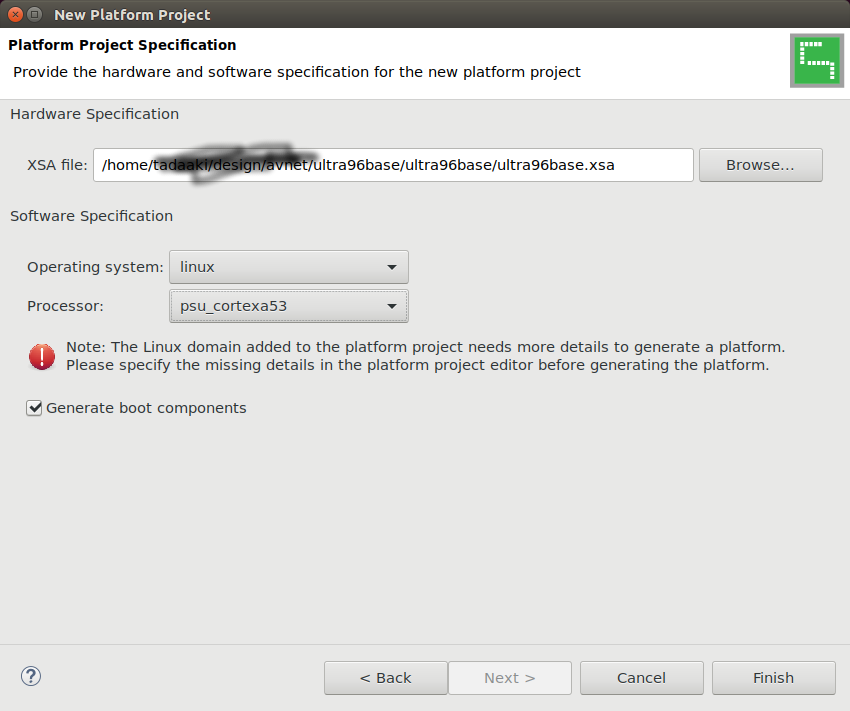

次にどこから、プラットフォームを作るのか聞いてきます。

今回はXSAから作成するので、Create from hardware specification (XSA) を選択、Nextを押します。

Vivadoで作成した、xsaファイルを指定します。Operating system は、Linuxで、Processorは psu_cortexa53に選択します。

まだ、ファイルが足りないので、ビックリマークは赤いままで、大丈夫です。 設定したら、Finishを押します。

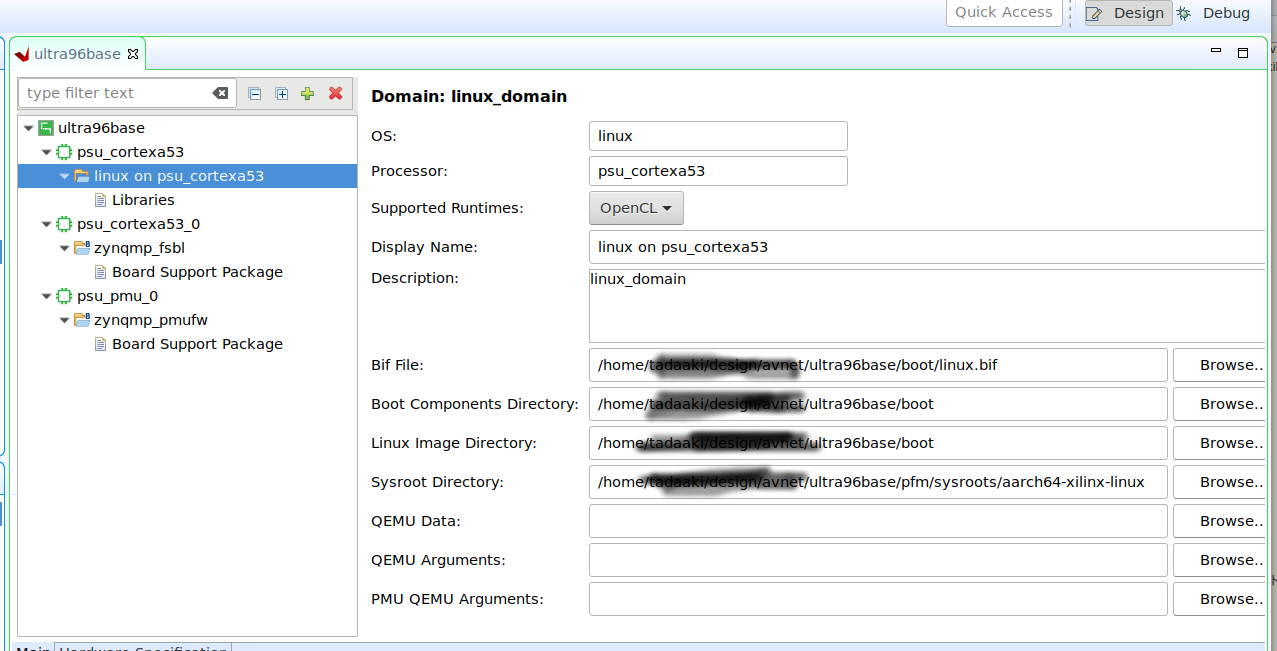

次の画面が出ると、作成されました。linuxとzynqmp_fsblとzynqmp_pmufwがあることを確認してください。

linuxについてはまだ設定ファイルが足りないので、更に追加していきます。

linux on psu_cortexa53を選択して、エラーをなくします。Bifファイルは、linux.bif を、Boot ComponentDirectoryと Linux image Directoryには bootディレクトリーを Sysrootディレクトリーには、sysroots/aarch64-xilinx-linuxをそれぞれ指定します。

その後、トンカチアイコン をクリックして、ビルドします。

をクリックして、ビルドします。

ここは、インデックスファイルを作っているらしく、時間がかかります。

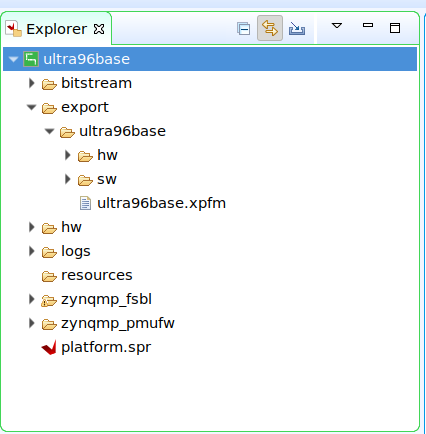

少し待つとビルドがおわり、exportのフォルダーにプラットフォームのデータが作成されます。

これで、ultra96向けプラットフォームが作成されました。

テストアプリケーションの作成

試しにできたかを確認します。

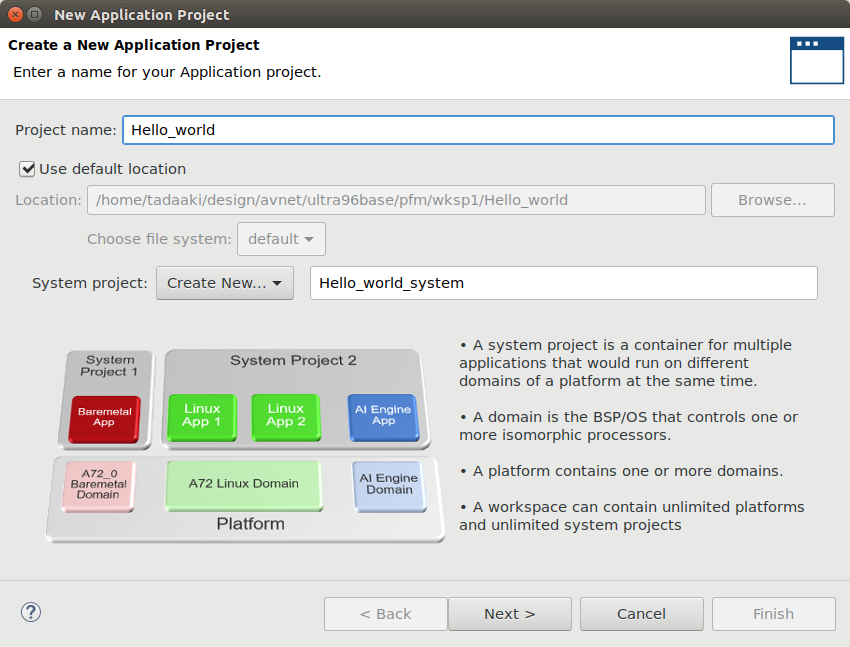

Vitisのメニューから File→New→Application Projectを選択します。

プロジェクトネームを適当に入れます。今回はHello Worldにしました。Nextをクリックします。

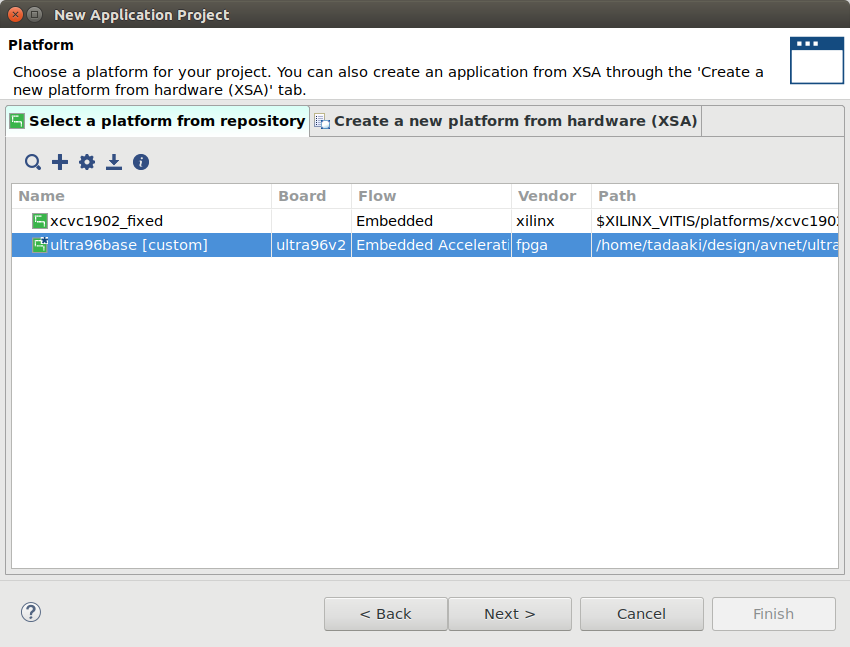

次に、プラットフォームを選択できますので、選択します。ultra96baseです。Nextを押します。

次はsysroot等を聞いてきますが、今回はそのままNextです。

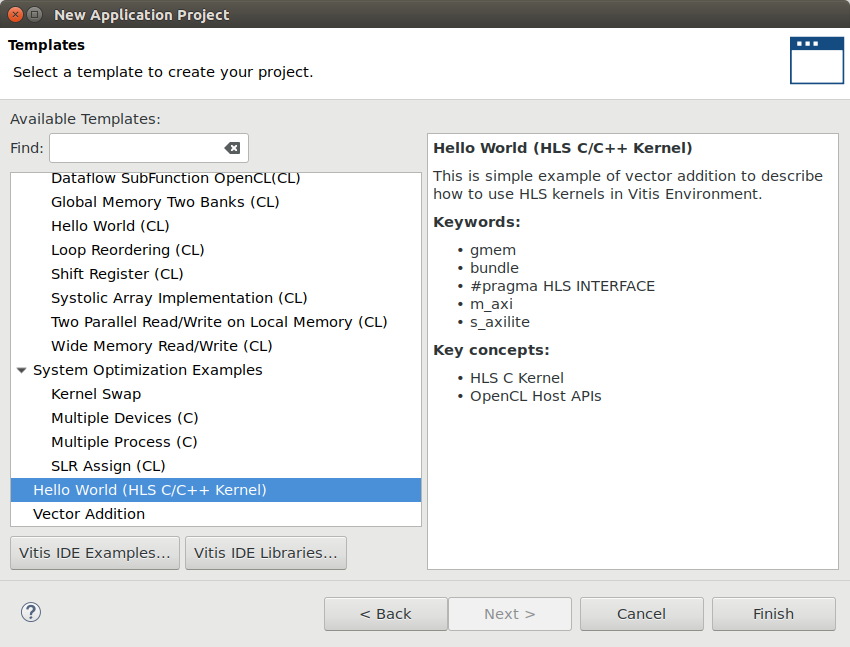

その後、お試しをいたします。Exampleを試します。

まだ、Exampleを取り込んでない場合は、取り込むとダウンロードできます。

ビルドを行います。トンカチアイコンの右側の三角印 から、Hardwareを選択します。

から、Hardwareを選択します。

その後、SDcardの中に必要なファイルができます。

Linux用のSDカードを用意してください。

Vitisでできたファイルは SDカードのFATの領域にコピーします。(フォルダー名は適宜変えてください)

cp ./Hardware/sdcard/* /media/$USER/boot

またPetalinuxで作ったrootfs.tar.gzをSDカードのEXTフォルダーに入れます。(フォルダー名は適宜変えてください)

sudo tar xzvf <petalinux path>/images/linux/rootfs.tar.gz -C /media/$USER/rootfs

その後、Ultra96で実機テストを行います。USB-UARTを接続してください。

ID:root PW:root でUlatra96でLoginします。

その後、次のコマンドで実行可能です。

cd /run/media/mmcblk0p1

export XILINX_XRT=/usr

./Hello_world.elf vadd.xclbin

TEST PASS が通りまして、動作を行っています。

次の展開

今回はプラットフォームの作成を流すだけでした。

途中で、QEMUにも挑戦したのですが、まだ情報が足りてないです。また別の機会に載せたいと思います。

次は、Wifi含めた、Ultra96のプラットフォーム作りを考えています。

参考文献

Vitis 統合ソフトウェア プラットフォームの資料 アプリケーション アクセラレーション 開発

[FPGAの部屋 Ultra96-V2 の Vitis アクセラレーション・プラットフォームの作り方1]

(https://marsee101.blog.fc2.com/blog-entry-4717.html)

[FPGAの部屋 Ultra96-V2 の Vitis アクセラレーション・プラットフォームの作り方2]

(https://marsee101.blog.fc2.com/blog-entry-4718.html)

[FPGAの部屋 Ultra96-V2 の Vitis アクセラレーション・プラットフォームの作り方3]

(https://marsee101.blog.fc2.com/blog-entry-4719.html)

[FPGAの部屋 Ultra96-V2 の Vitis アクセラレーション・プラットフォームの作り方4]

(https://marsee101.blog.fc2.com/blog-entry-4720.html)