Ultra96V2でとりあえずLinuxを動かす

本記事では、自分用のメモとしてAvnet社製のUltra96V2でVivadoでHW Componentを作成から、Linux上でvaddサンプルプログラムを動かすまでを記載します。

使用するOSとツールのバージョンは以下の通りです。

- Ubuntu 20.04.3

- Vivado 2021.1

- Vitis 2021.1

- PetaLinux 2021.1

また、以上のツールのインストール方法はここでは記載しませんので、適宜Xilinxホームページから落としてきてください。

ちなみに、フローについては以下のチュートリアルを参考にしています。

チュートリアルに倣い、フォルダー構成は以下の通りにします。

- ultra96v2

- ultra96v2_platform

- ultra96v2_plnx

- ultra96v2_pkg

上記フォルダーの説明は以下のとおりです。

- ultra96v2_platform : Vivadoの作業用フォルダ

- ultra96v2_plnx : PetaLinuxの作業用フォルダ

- ultra96v2_pkg : Vitisの作業用フォルダ

なお私はXilinxのツールやUltra96V2は愚か、Qiitaの記事を書くのはこれが初めてになりますので所々不備があるかと思いますが、その際はご指摘いただけると幸いです。

VivadoでHW Componentの作成

BDFファイルの導入

まず最初にBoard Definition Files (BDF) を落とします。

上記サイトからDownload ZIPを押してBDFを落とします。

落としたbdf-master.zipを<Vivadoインストールフォルダ>/Vivado/2021.1/data/boards/board_files/に解凍します。

Vivadoプロジェクトの作成

Vivadoを起動します。起動したらCreate Projectを押してultra96v2_platformフォルダ上にプロジェクトを作成します。

最初のページはNextを押して飛ばします。次のページではプロジェクト名とプロジェクトフォルダの指定を行います。

project名はultra96v2とします。Create project subdirectoryのチェックを外しましょう。

Project TypeではRTL Projectを選択します。Do not specify sources at this timeとProject is an extensible Vitis Platformのチェックをつけます。

ボードの選択になります。Ultra96-V2 Single Board Computerを選択します。

プロジェクトを作成したら、左のFlow NavigatorのIP INTEGRATOR -> Create Block Designを選択します。

デザイン名はultra96v2とします。

Zynq Ultrascale+ MPSoC IPの追加

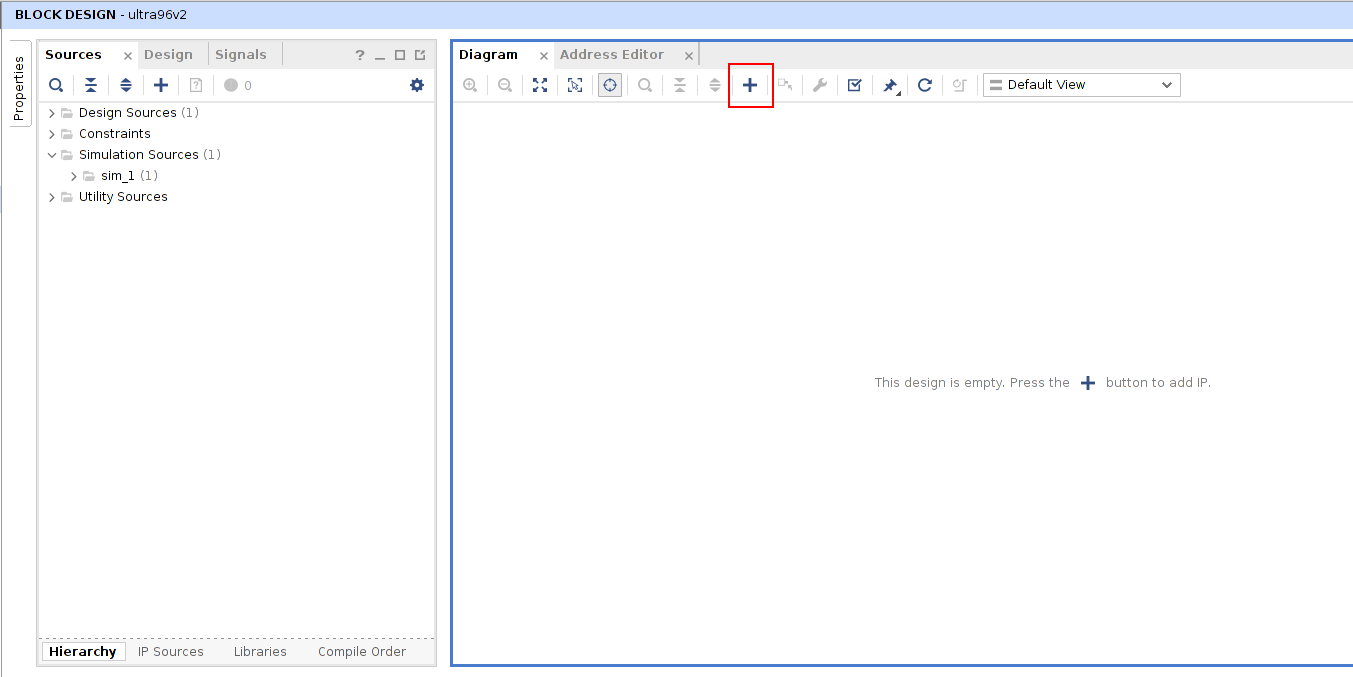

このような画面になると思いますので、+ボタンを押してIPを追加していきます。

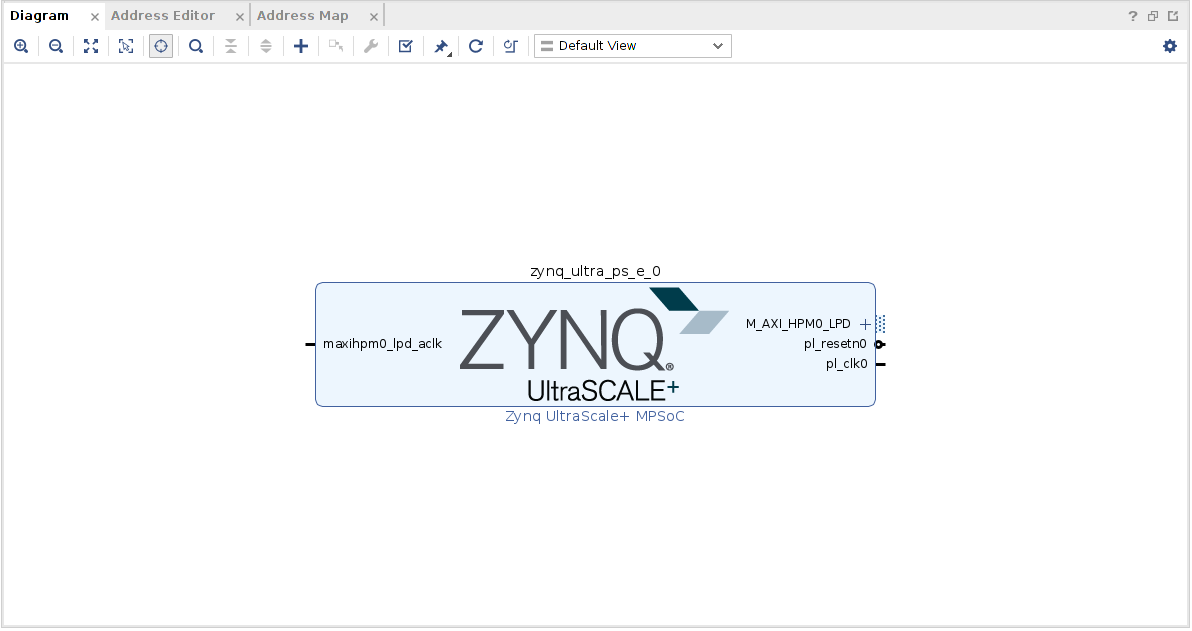

zynqと調べればZynq UltraScale+ MPSoCというのがヒットしますので、選択します。

すると、Diagram上にZYNQのIPが追加されると思いますので、次にこちらの設定を行っていきます。

I/O Configration

ここで参考にするのは主にUltra96V2の回路図になります。

以下のページのドキュメント -> Ultra96-V2 Rev1 Schematicが回路図になります。

Diagram上のZYNQのIPをダブルクリックして設定ウィンドウを開きます。

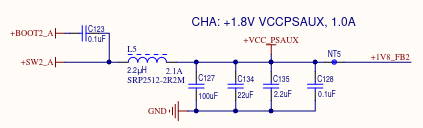

まずMIOの電圧設定を行います。回路図p.10を見るとPS部のIO電源としてはVCC_PSAUXが使用されているようです。

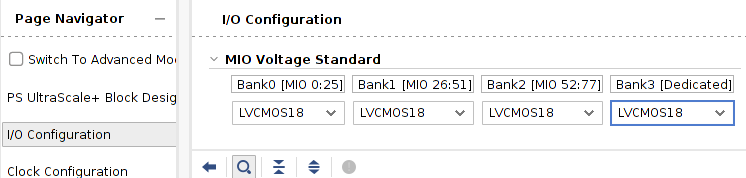

p.15の回路図を見るとVCC_PSAUXは1.8Vとのことですので、I/O Configurationを選択して以下の図の通りLVCMOS18を選択します。

それでは次にペリフェラルの設定を行っていきます。流石に回路図をいちいち掲載するのは面倒なので、結果だけ示します (使用しているペリフェラルを設定していくだけです)。ちなみに40、60ピンヘッダーに接続されているペリフェラルに関しては設定を行いません。必要最低限の設定を行いたいと思います。

SD

Low Speed -> Memory Interfaces -> SDの設定です。SD0とSD1を使用していますので、以下の通り設定を行います。SD0、SD1共にSlot TypeはSD 2.0となりますので設定を変更します。IOピンに関しても図の通り設定を行います。

UART

Low Speed -> I/O Peripherals -> UARTの設定です。図の通りIOの設定を行います。

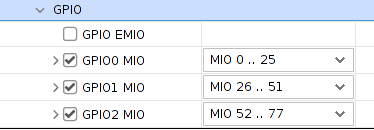

GPIO

Low Speed -> I/O Peripherals -> GPIOの設定です。図の通り有効化します。

USB

High Speed -> USBの設定です。GT Laneの設定を変更します。

USB Resetの設定をどうすればいいかは情報を見つけられませんでしたが、デフォルトのBoot Pinで動作しましたので、変更は加えません。詳しい方いましたら情報ください。

Display Port

High Speed -> DisplayPortの設定です。

Clock Configuration

次にクロック設定を行います。

Input Clocks

Input Clocksの設定では、GT Laneのリファレンスクロックのみを設定します。

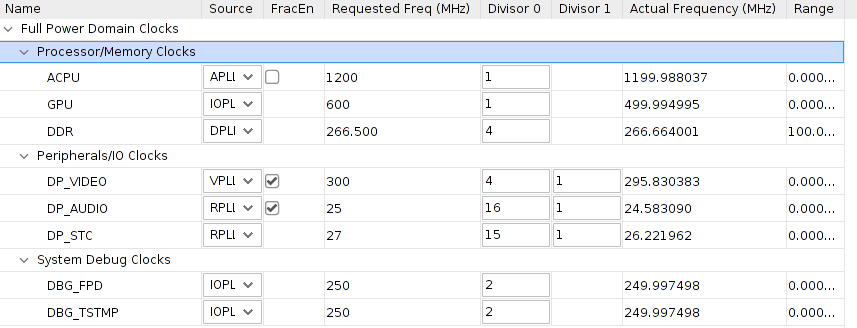

Output Clocks

こちらの設定は自動設定ではなかなか上手く設定してくれませんでしたので、手動で設定を行います(bspのプラットフォームを参考にした)。基本はRequested FreqとActual Frequencyを一致させることが目標です。

まずEnable Manual Modeにチェックを入れます。

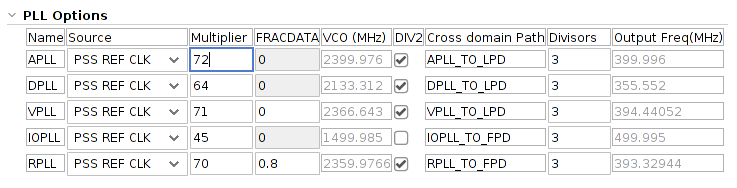

PLL

Low Power Domain Clocks

Low Power Domain Clocks -> Peripherals/IO Clocksの設定を図のように変更します。

Full Power Domain Clocks

Full Power Domain Clocksは以下の通り設定を変更します。

Advance Clocks

DDR Configuration

DDRの設定は以下の通り変更をします。tRC等のタイミングの設定はどうしたら良いかわからなかったのでデフォルトのままです。情報持っている方いたら教えてください。

PS-PL Configration

PS部とPL部を繋ぐインターフェース部の設定になります。割り込みを一つ追加します。

Zynq IPの設定は以上になります。OKを押しましょう。

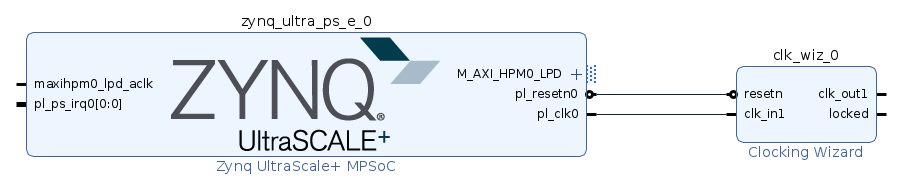

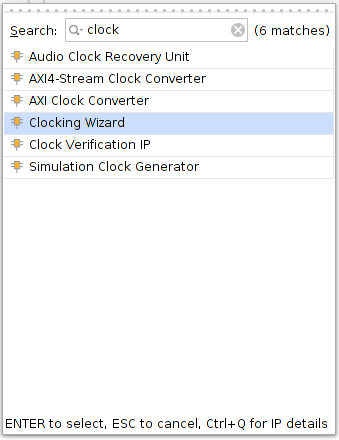

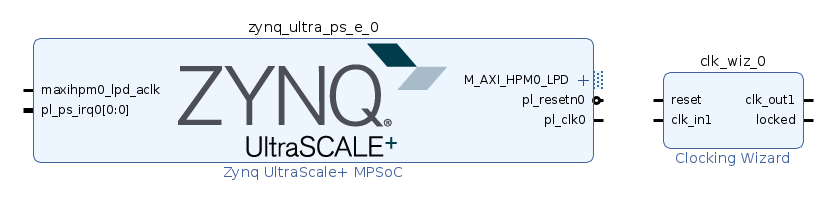

Clocking Wizard IPの追加

次にデザインのクロックの設定を行います。Clocking Wizard IPを追加します。

今回はテストプログラムであるvaddを動作させるだけですので、出力クロックは1つだけ設定します。

周波数は300MHzとしておきます (特にこだわりは無い。動くかな?)。

また、リセットの極性を合わせるためReset TypeをActive Lowに設定します。

Processor System Reset IPの追加

Clocking Wizardで出力したクロックに同期したリセット信号を生成します。Clock Exportで必要とのことです(具体的にはわからない)。

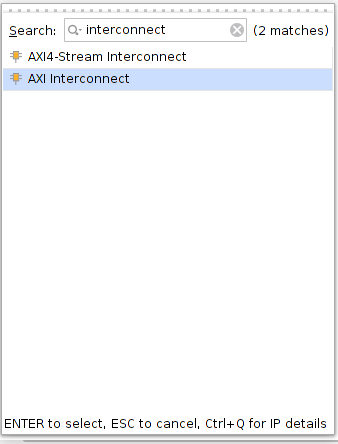

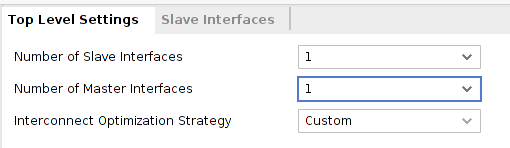

AXI Interconnect IPの追加

このIPは後述するAXI Interrupt Controller IPとの接続ために用います。

Master Interfaceの数を1つにします

配線します。

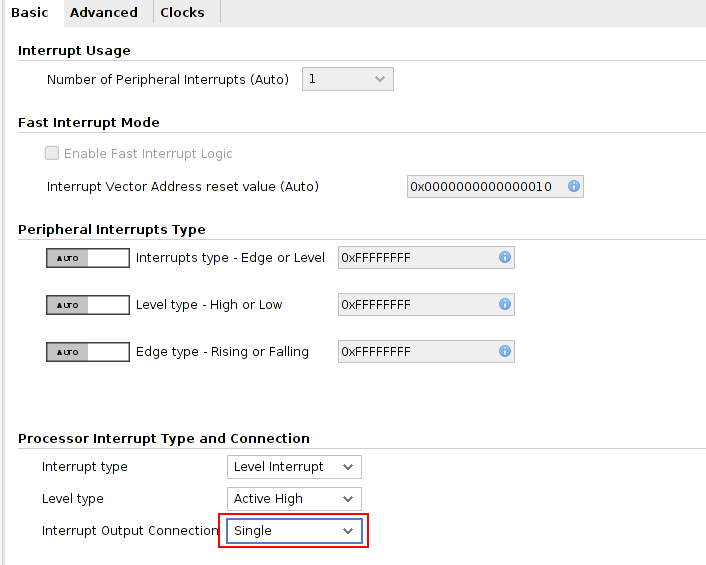

AXI Interrupt Controller IPの追加

カーネル -> プラットフォームへの割り込みのため、AXI Interruput Controller IPを追加します。なお、カーネルとプラットフォーム間の割り込みの対応付けはV++リンカーが自動で行ってくれるみたいです。

Interrupt Output ConnectionをSingleに設定します。

配線します。

忘れていましたが、maxihpm0_lpd_aclkとclk_out1を接続します。

Platformの設定

Platform Setupを開きます。

AXI Portの設定を行います。SP Tagはスレーブインターフェースに対して記述するようです。V++(Vitisのコンパイラ)の設定でこれらのインターフェースが選択できるようにこちらのTagを命名する必要があるようです。ユーザー定義ですので、適当に命名しました。

次に、プラットフォーム <-> カーネル間のクロック設定を行います。ここで設定できるクロックはProcessor System Reset IPを用いて同期リセットを生成したクロックのみになります。

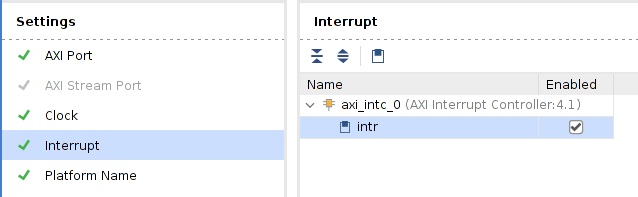

次にInterruptの設定を行います。

Platform Nameは適当に入力しておきます。

以上の設定が終わったらDiagramに戻り、Validationを行います。

すると、このようにAXI Intterupt Controllerのintrポートに何も接続されていないとWarningが出ますが、これは後にV++のリンカーが勝手に接続してくれますので、問題無いとのことなので無視。

XSAファイルのエクスポート

次に、Design Sources内のultra96v2を右クリックしてCreate HDL Wrapper...をクリックします。

次にBlock Designの生成を行います。Flow NavigatorのGenerate Block Designを選択します。

Systhesis OptionsをGlobalに変更し、Generateボタンを押します。

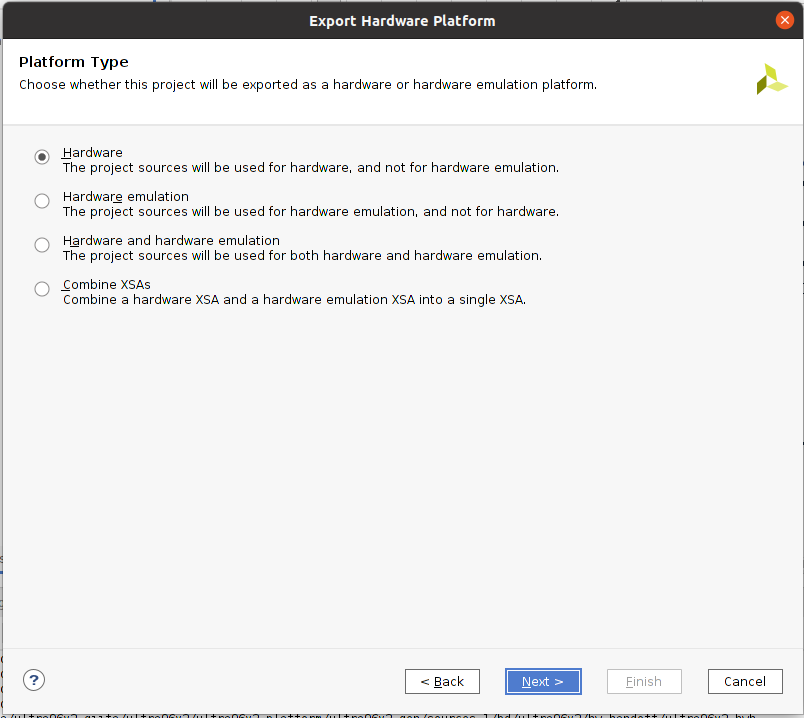

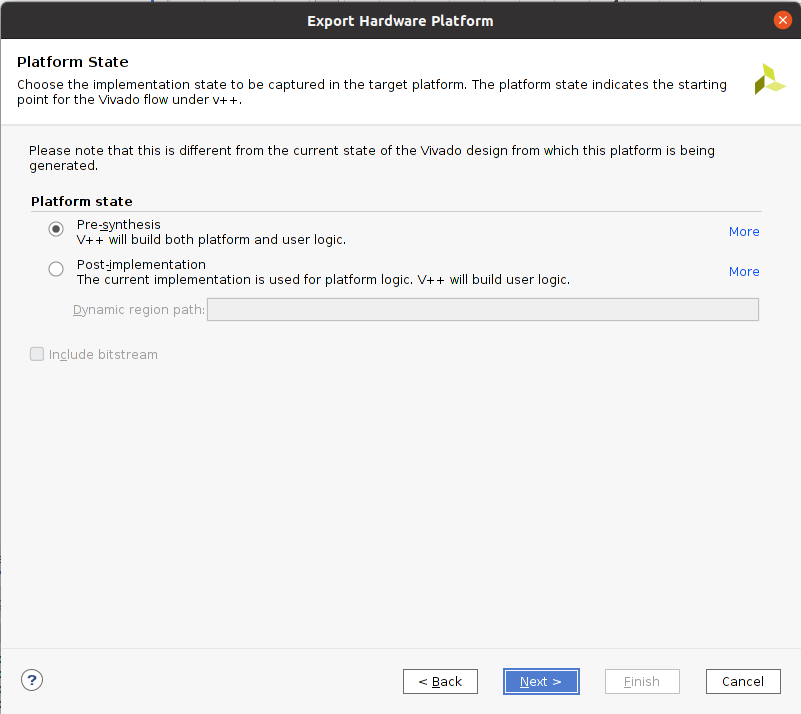

終わったらメニューバーからFile -> Export -> Export Platform...を選択します。

Platform TypeはHardwareを選択します。

Platform StateはPre-synthesisを選択します。

ここは何も変更しません。

こちらも特に変更は加えません。

Finishを押します。

するとプロジェクトの作業フォルダにultra96v2_wrapper.xsaが生成されているはずです。

以上でVivadoのHW Component作成は終わりです。

次の記事

本記事は以上までとなります。次はPetaLinuxを用いてLinuxカーネルの構築を行いたいと思います。