はじめに

G.W.の課題の FPGA 開発として手始めに組み合わせ回路である AND 回路を作ってみました。

開発環境は以下のとおりです。

- FPGA: GW1NR-LV9QN88PC6/I5

- EDA: Gowin V1.9.8.09 Education Edition (Windows)

- OS: Windows11

Verilog ファイルの作成

メニューバーの File > New > Verilog File から top.sv というファイル名で作成しました。内容は以下のとおりです。

// top.sv

module top (

input IN_A,

input IN_B,

output OUT_C

);

// Tang-Nano-9Kの基板上に実装されているLEDは不論理なので反転する

assign OUT_C = ~(IN_A & IN_B);

endmodule

物理制約ファイルの作成

メニューバーの File > New > Physical Constraints File から top.cst というファイル名で作成しました。内容は以下のとおりです。

// top.cst

IO_LOC "IN_A" 79; // PIN79_IOT12B_1V8

IO_PORT "IN_A" IO_TYPE = LVCMOS33 PULL_MODE = DOWN;

IO_LOC "IN_B" 80; // PIN80_IOT12A_1V8

IO_PORT "IN_B" IO_TYPE = LVCMOS33 PULL_MODE = DOWN;

IO_LOC "OUT_C" 16; // PIN16_IOL26B_LED6

IO_PORT "OUT_C" IO_TYPE = LVCMOS33 PULL_MODE = UP;

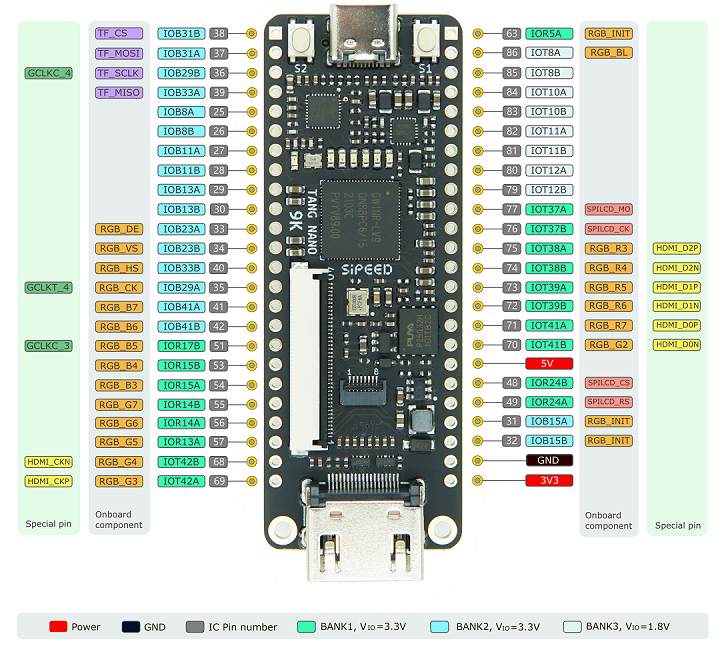

ピン番号はピン配置図から選択しました。ピン配置図は次のURLからダウンロードすることができます。

https://dl.sipeed.com/shareURL/TANG/Nano%209K/2_Schematic

コネクタとFPGAのピン対応は次のようになっています。FPGAの79番がコネクタJ6の9番ピンに、FPGAの80番がコネクタJ6の8番ピンに対応していることが分かります。

LEDは次のようにFPGAの16番がLED6に対応しています。

メーカーサイト (https://wiki.sipeed.com/hardware/en/tang/Tang-Nano-9K/Nano-9K.html) のピンマップも参考にしてください。

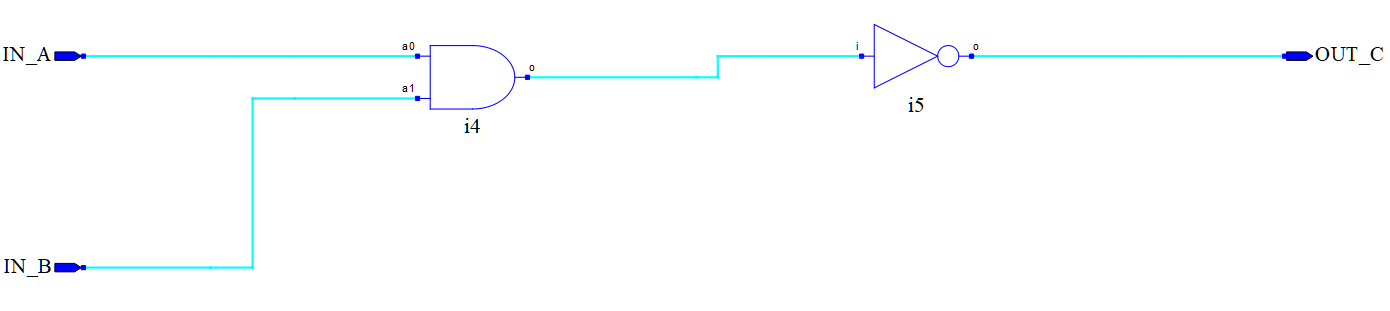

回路図の確認

問題なく回路が組めていれば、メニューバーの Tools > Schematic Viewer から回路図ビューワーを開いて、回路図を確認することができます。今回のHDLで生成された回路は次の通りです。意図した回路になっていることが確認できました。

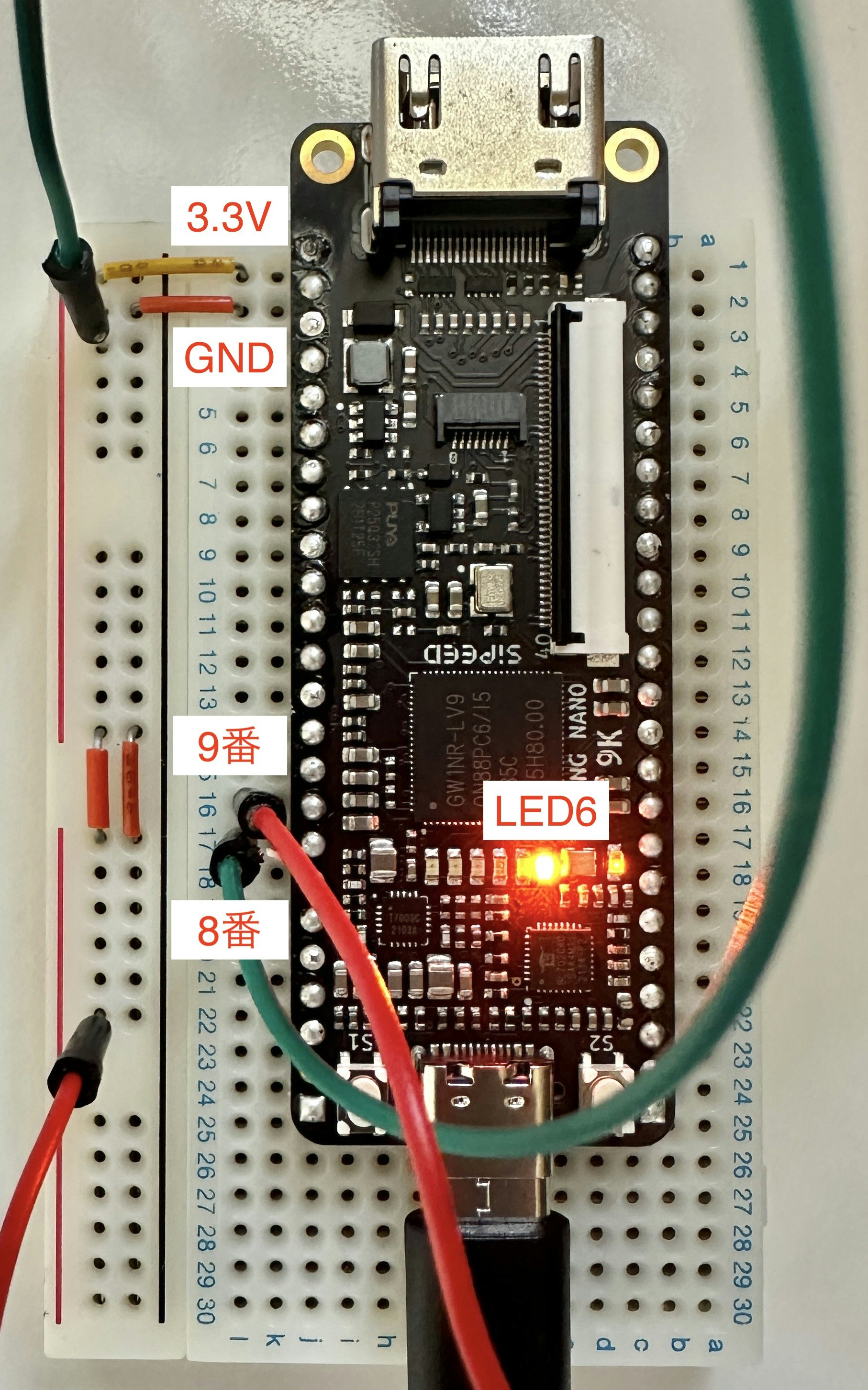

動作確認

ビットストリームを生成してFPGAに書き込んで動作を確認しました。写真はFPGAから供給される3.3Vを8番、9番ピンに入力してANDを取った結果、LED6が点灯している様子です。入力のどちらもHiでないと消灯することも確認しました。

おわりに

入門としてごく簡単なものですが、意図した通りに動くと楽しいですね。また、このようなデバイスと開発環境が2,500円程度で手に入るということに感動しました。

参考文献

[1] CQ出版社. 2500円ボードで始めるFPGA開発 Vol.2. Interface. 2022, 12月号, 別冊付録1