前回は Arria 10 SoC でサンプルのベアメタルアプリを動かすところまで紹介しました。

- Arria 10 SoC のベアメタル開発におけるハマりポイント

今回はその際に気づいた Early Release IO 機能について触れていきます。

Early Release IO vs Full Configuration

Early Release IO は Arria 10 などの少し大きな規模の FPGA にかかるコンフィグ時間が ARM のブートに影響するのを最小限に抑えるための機能です。前回も紹介した通り Arria 10 SoC は SDRAM コントローラが FPGA 側にあるので ARM だけ動かす場合にも FPGA をコンフィグしてあげる必要があるのですがコンフィグにかかる時間がもったいないので必要最低限の回路だけコンフィグして先に ARM を立ち上げようってコンセプトのものです。(その反対? が Full Configuration で一度にすべての領域をコンフィグします)

必要最低限の回路ってなんだ? って思った方もいると思いますが、「必要最低限の回路 = SDRAM コントローラの回路」と考えていただければ支障はないです。(本当はもう少しありますが)

提供されるハードウェアのサンプルではデフォルトでこの設定が有効なのでこの機能が不要な場合には無効にする必要があります。

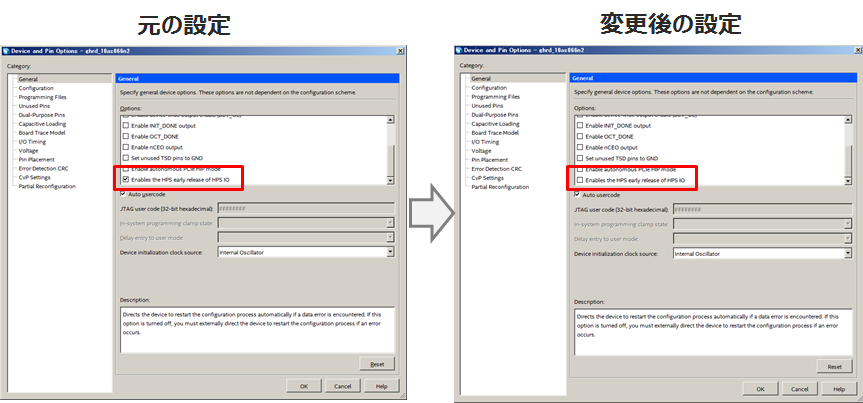

Quartus Prime 側の設定

Early Release IO は Quartus 側と Platform Designer(旧Qsys) の 2つの設定があります。こちらが Quartus 側の設定です。

Assignments -> Device -> Device and Pin Options -> General に設定があります。

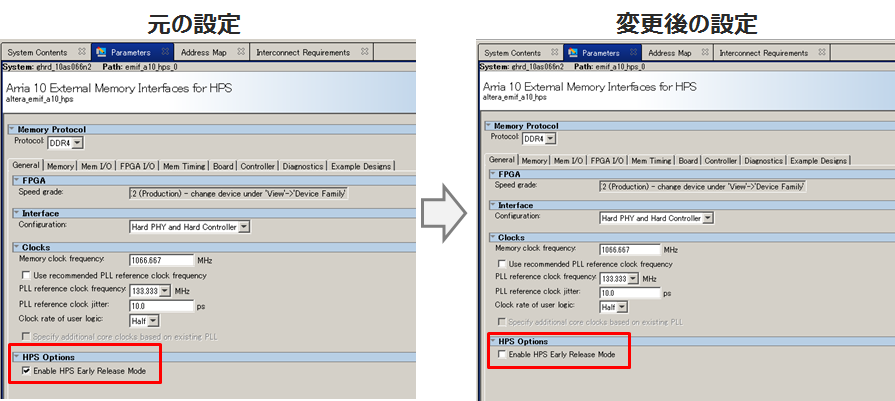

Platform Designer(旧Qsys) 側の設定

こちらが Platform Designer 側の設定です。 HPS(ARM) ではなく SDRAM コントローラ側 (Arria 10 External Memory Interface IP for HPS という IP)に設定があるので注意です。

それぞれチェックを外したら FPGA をコンパイルしましょう。(Platform Designer の再ジェネレートも忘れずに)

コンパイルが完了すると Early Release IO が OFF になった FPGA デザインデータが生成されます。

RBF ファイルの生成

U-Boot から FPGA のコンフィグを実施する場合、FPGA のデータは RBF ファイルを使用します。

Early Release IO の場合は2つの RBF、Full Configuration の場合は RBF は1つのみです。

RBF の生成方法に関しては下記にも手順が掲載されているので併せて確認してみてください。

https://rocketboards.org/foswiki/Documentation/A10GSRDCompilingHardwareDesignLTS

・Early Release IO の場合

$ quartus_cpf -c --hps -o bitstream_compression=on output_files/ghrd_10as066n2.sof output_files/ghrd_10as066n2.rbf

--hps オプションをつけるのがミソです。GUI では hps のオプションが用意されていないので注意です。このコマンドで以下2つの RBF ファイルが生成されます。

・ghrd_10as066n2.periph.rbf - SDRAM コントローラを含む IO 部のコンフィグデータ

・ghrd_10as066n2.core.rbf - その他 FPGA のコア部のコンフィグデータ

・Full Configuration の場合

$ quartus_cpf -c -o bitstream_compression=on output_files/ghrd_10as066n2.sof output_files/ghrd_10as066n2.rbf

こちらは通常通り。

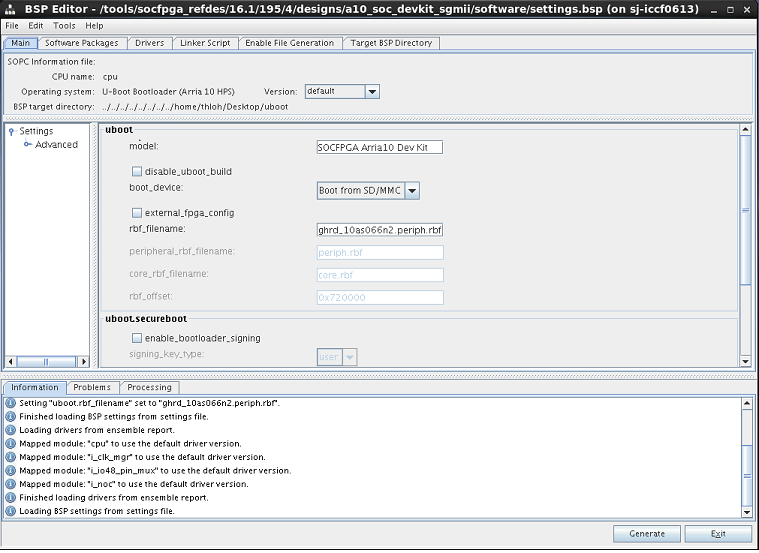

U-Boot の生成

続いて U-Boot の生成です。HPS(ARM)の初期化は U-Boot が実施するので作り直したデータを元に U-Boot を作り直します。

U-Boot の生成方法に関しては下記にも記載があるので併せて確認してみてください。

https://rocketboards.org/foswiki/Documentation/A10GSRDGeneratingUBootAndUBootDeviceTree

残念なのが U-Boot のビルドは Linux ホストのみとなっていることです。Cyclone V SoC の Preloader/U-Boot は Windows ホストでもビルドできるのでぜひ Arria 10 SoC でもサポートしてもらいたかった部分ですが仕方ないですね、、、

Early Release IO の場合

rbf_filename には xxx.periph.rbf の方を指定します。下の方にグレーアウトされてはいるもののいかにも入力して欲しそうなウィンドウがあるのですが、こちらは常にグレーアウトになっているというフェイントをかけてきますのでご注意ください。

Generate を実行してプロジェクトを生成し Make を実行すれば U-Boot が生成されます。

Full Configuration の場合

こちらの場合は rbf_filename に通常の RBF を指定すれば OK です。

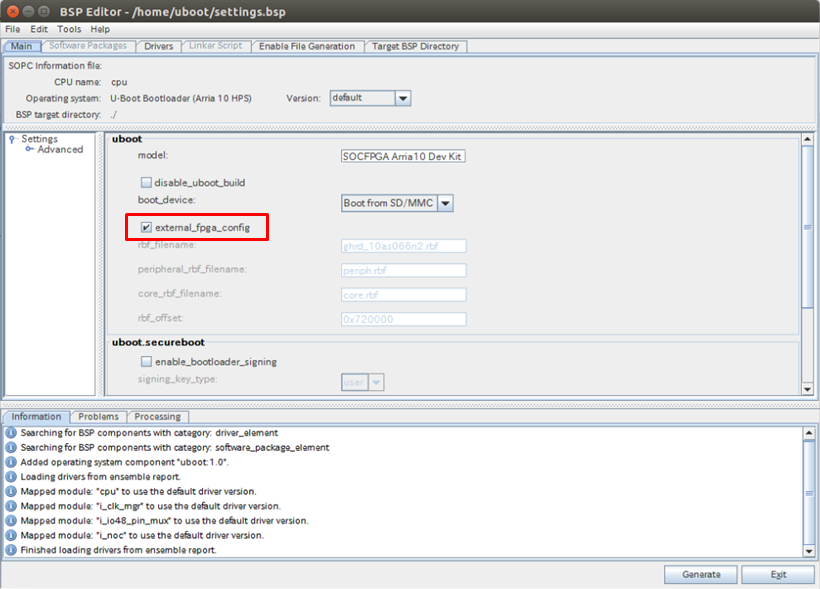

SOF ファイルを使用してベアメタルアプリを DS-5 からロードする場合には?

この時 FPGA は JTAG 経由でコンフィグすることが想定されるため External Config のオプションを有効にして U-Boot を作ります。このオプションを使用しない場合、U-Boot の実行時に RBF ファイルを FPGA に流し込もうとしてしまい、SD カードが挿入されていない場合は読み出しエラーになってしまいます。(SD カードが挿入されていたとしてもせっかくJTAGで書き込んだ SOF データが上書きされることになるので要注意です)

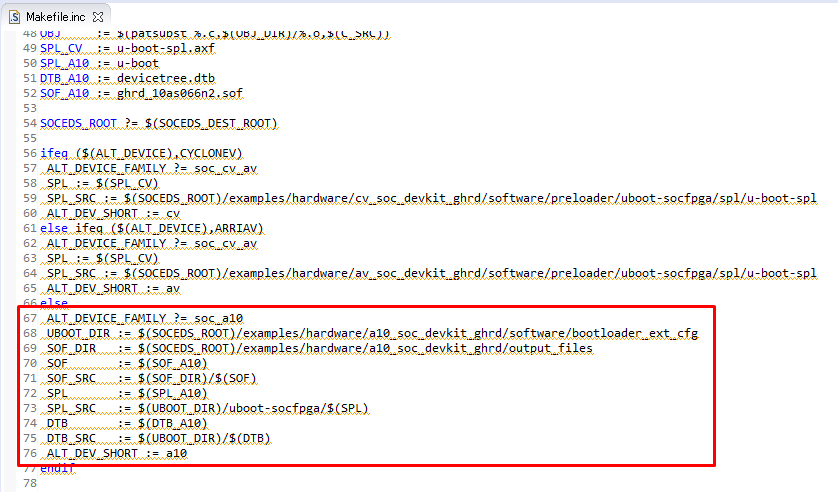

ベアメタルアプリのサンプルプロジェクト内にある Makefile.inc を見るとデフォルトでは SoC EDS のインストールディレクトリから U-Boot のデータをひっぱってきているのでこれを適切に差し替えます。(ここでも External Config を有効にした U-Boot を使用していることが見て取れますね)

DS-5 でのデバッグ時には JTAG から SOF ファイルを書き込んであげることをお忘れなく。そうしないと U-Boot のログも出力されません。

まとめ

上記の通り Arria 10 SoC では FPGA のコンフィグ時間が ARM の起動に与える影響を最小限に抑えるための Early Release IO 機能が搭載されます。各種設定方法さえ理解すれば怖いものではないですね。

また、U-Boot から RBF を使用して FPGA をコンフィグすることが前提になっていますので、DS-5 を使用したベアメタル開発をする場合には External Config のオプションを有効にした U-Boot を作成する必要があります。このあたりを理解せずに実施しようとするとエラーが出ても何が悪いのかわからずということもあるかと思うのでこの記事を参考にしていただけると幸いです。