EBAZ4205を使ったZYNQの勉強をしています。

はまったところの解決策を中心に書きます。

vivado側

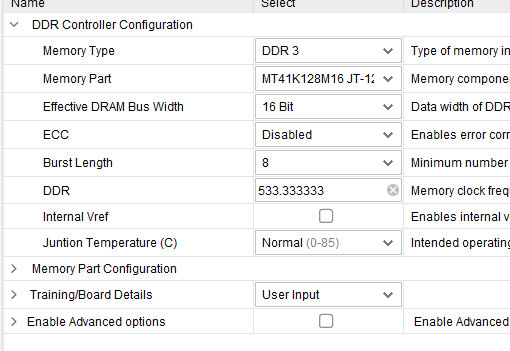

大全のP.272から進めます。EBAZでの変更点。

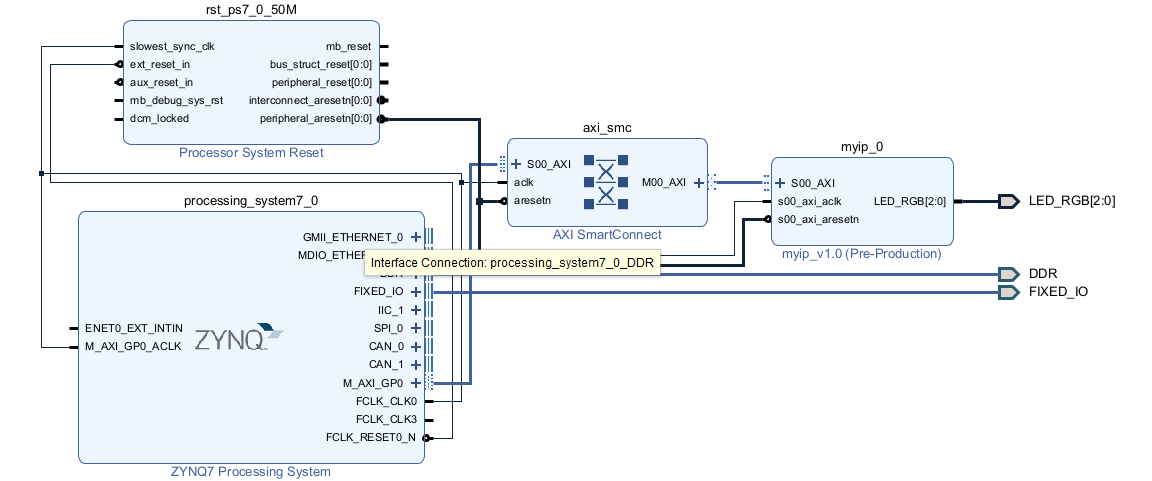

・全体のブロック図

Regenerate Layout をするとすっきりした配線になる気がする。

vivado側は、大全の内容で問題なく作業できると思います。

vitis で はまったところ (ver2022.2,2023.2,2024.2で確認)

・vivadoで生成したxsaを使って作ったplatformプロジェクトをコンパイルしました。参考書と同じ手順で行いましたが、myipのコンパイルで複数エラーが発生。

・内容はCソースのファイルが存在しないというエラーのようです。

・AMDのコミュニティーでも同じエラーが報告されていました。

https://adaptivesupport.amd.com/s/question/0D54U00006l9xEpSAI/vitis-202222-cannot-build-platform-having-customer-ip?language=ja

・私の環境ではvivado2022,2023,2024のバージョンで同じエラーとなりました。

修正方法

・最善の方法ではありませんが、以下の手順で修正しました。

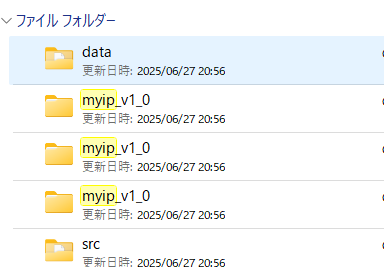

- vitisで生成されたフォルダ内でカスタムIP名で調べ、該当のフォルダを抽出する

私の環境では「3フォルダ」見つかりました。

- 該当フォルダ➡src➡makefile の2行を以下のように書き換えます。

変更前

LIBSOURCES=($wildcard *.c)

OUTS = $(wildcard *.c)

変更後

LIBSOURCES=$(wildcard *.c)

OUTS = $(addsuffix .o, $(basename $(wildcard *.c)))

意味としては、現在のディレクトリにあるすべてのC言語ソースファイル(.c)に対応して、

オブジェクトファイル(.o)のリストをOUTS変数に格納する指示(より明示的に)になります。

ベースアドレスの考え

zynqのようなPSとPL一体のSoCを初めて勉強したので、このベースアドレスの考え方が最初わかりづらかったです。

PLとPSをAXIバスで接続してPSから制御する場合、PSからアクセスするレジスタアドレスは、このベースアドレスを基準として考えるようです。

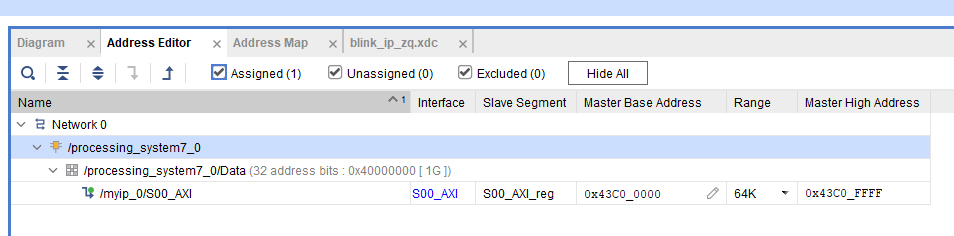

vivadoのblock diagram の「address editor」に今回作成したIPと接続したAXIバスのアドレスが記載されています。

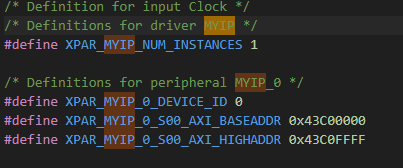

同様に、vitisにxsaファイルを渡してplatformを作成する際に、xparameters.hが生成されますが、この中にも同じアドレスがマクロ定義されています。

自作IPで自動生成されたAXI slave のRTLを確認すると、slv_reg0~slv_reg3まで4つのレジスタグループが作られていました。演習ではslv_reg0を指示通り使いました。

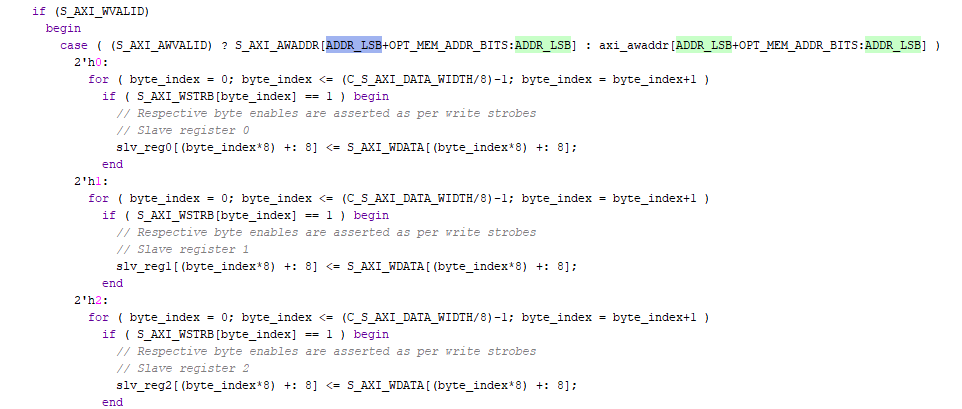

自動生成されたAXI slave のRTLの以下のcase分より、[3:2]のビットでどのレジスタを使うかを選択しています。

つまりアドレスの下位が0x00ならreg0、0x04ならreg1、0x08ならreg2、0x0Cならreg3と4バイト境界でアドレスを区切っているようです。

ベースアドレスが 私の例では 0x43C00000なので、reg0へのアクセスはそのまま0x43C00000、reg1へのアクセスは0x43C00004、reg2は0x43C00008、reg3は0x43C0000C といった具合になるようです。

マイコン畑で育った私は、レジスタアドレスはユーザーマニュアルに全て載っているのが当たり前!と思っていました。

ZynqのPLのようなベースアドレスだけ決めて、あとはそのアドレスからのオフセットで他のレジスタが決まるのは、難しいですね。

今日はここまで