ポリフェーズフィルタ(Poly Phase Filter)とは

信号処理、通信システムなどにおいて使用されるFIRインターポレーションフィルタやFIRデシメーションフィルタをFPGA やASICに実装する際に、ポリフェーズフィルタとすることで、フィルタの回路規模、消費電力などを削減できます。

MATLAB + DSP System Toolboxに、ポリフェーズフィルタへ係数変換機能があったので、それを使用して設計を行い、HDL Coderでコード生成を行ってFPGA実装を行ってみました。

ポリフェーズ分解

どのように係数変換が行われるかは、こちらの記事「ポリフェーズフィルタの基本を知る」に仕組みが書いてあるので参照してください。

FIRデシメーションフィルタからポリフェーズフィルタへの係数変換

MATLAB + DSP System Toolboxでデシメーションフィルタの設計は以下のようにして行いました。

Fpass = 0.45; % Passband Frequency

Fstop = 0.55; % Stopband Frequency

Apass = 1; % Passband Ripple (dB)

Astop = 60; % Stopband Attenuation (dB)

h = fdesign.decimator(4, 'Lowpass', 'fp,fst,ap,ast', Fpass, Fstop, ...

Apass, Astop);

Hd = design(h, 'equiripple', ...

'MinOrder', 'any', ...

'StopbandShape', 'flat', ...

'SystemObject', true);

上記を実行すると間引き数4のデシメーションフィルタが設計されます。

Hd =

dsp.FIRDecimator のプロパティ:

DecimationFactor: 4

NumeratorSource: 'Property'

Numerator: [-0.0024 -0.0021 0.0068 0.0167 0.0111 … ]

Structure: 'Direct form'

この係数Hd.Numeratorをポリフェーズフィルタの係数に変換します。

ppCoef = polyphase(Hd)

ppCoefは4x12の行列データ(4 = デシメーションファクター)となって出てくるので、これを複数のフィルタブロックの係数パラメータとして設定します。

フィルタ特性の確認

次のコマンドを実行してポリフェーズフィルタの周波数特性や係数情報などを確認します。

polyphase(Hd);

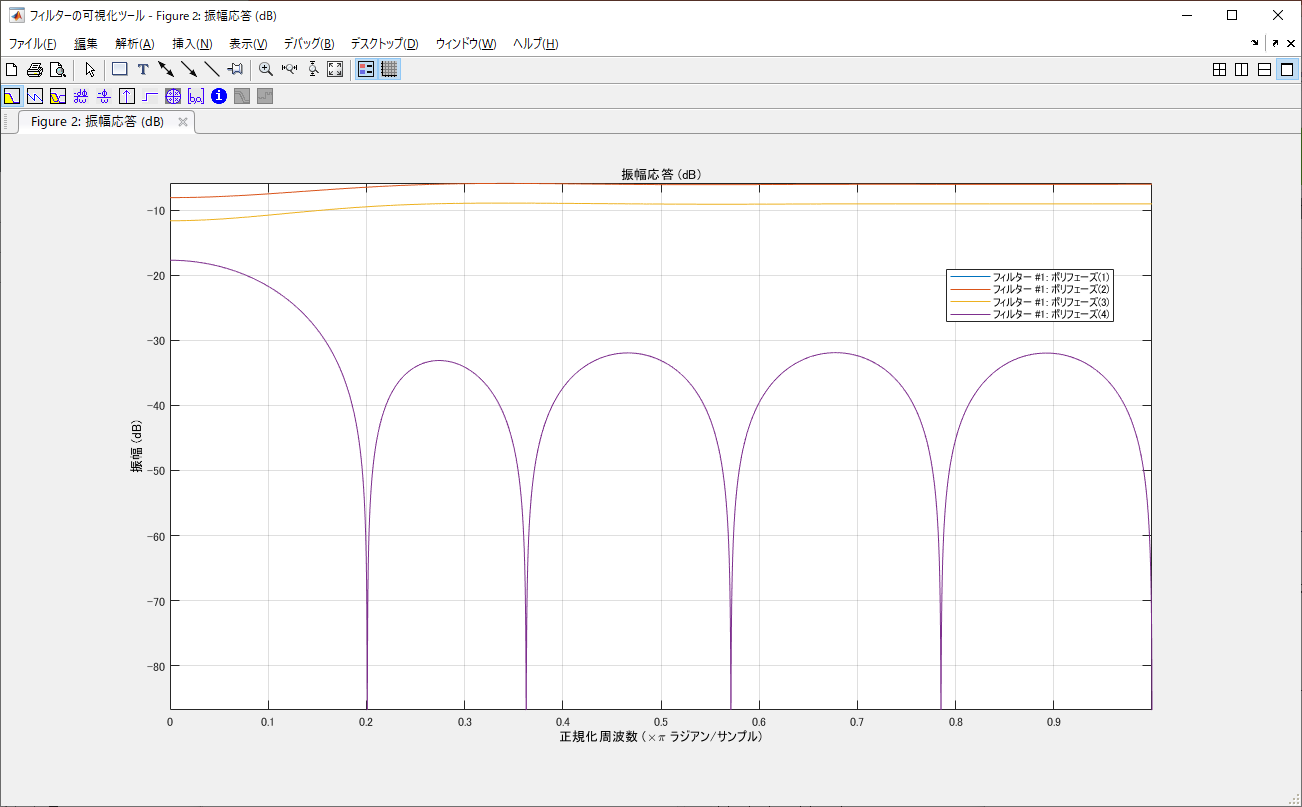

こちらはポリフェーズになった4つのフィルタ特性

4つのフィルタを並列接続すると、下図のポリフェーズ化する前のデシメーションフィルタの特性になります。

シミュレーションモデルの作成と動作確認

モデル全体は下図のようにチャープ信号入力、リファレンスモデル(FIRデシメーション)、ポリフェーズフィルタを比較できるように作成しました。

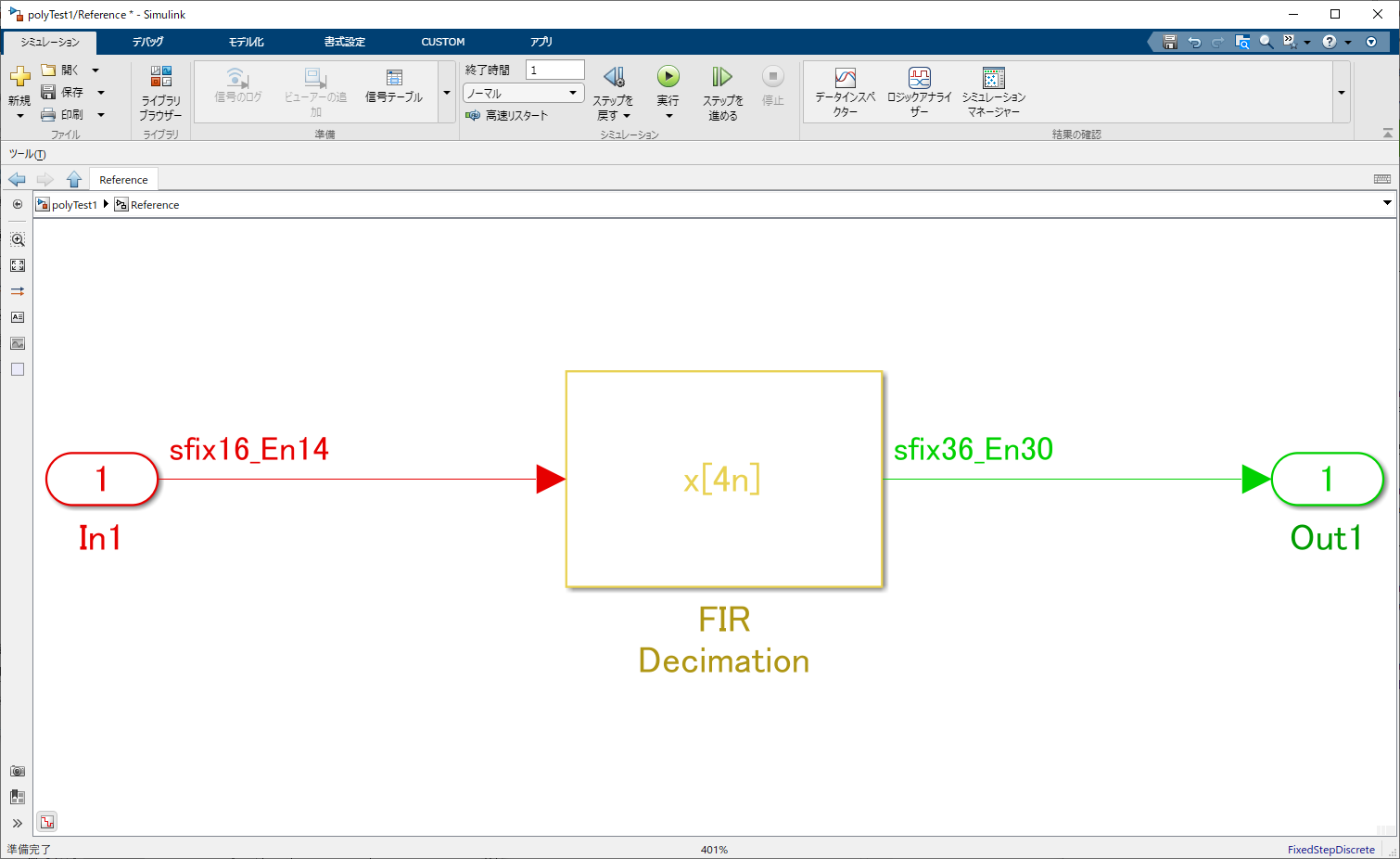

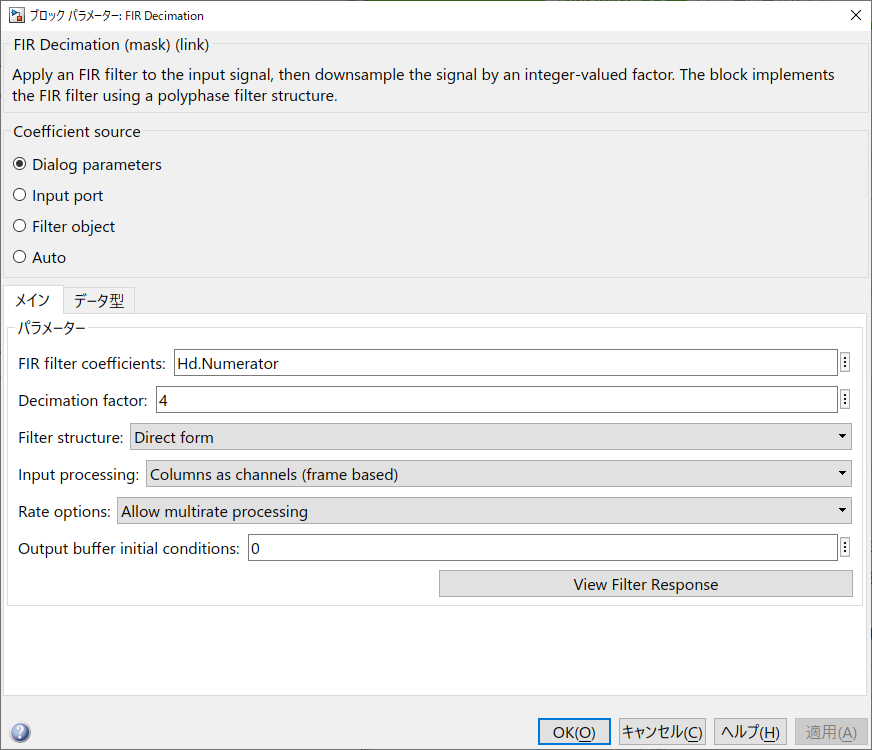

トップモデルでReferenceサブシステムとなっているのが下図のリファレンスとなるFIRデシメーションフィルタのモデルです。

フィルタの係数パラメータはdecimFilterDesign.mで計算した係数データが代入されています。

フィルタ係数はpolyphase関数で計算したポリフェーズフィルタの係数を、各フィルタで各行の係数を代入して使用しています。パラメータCoefficientsの値を ppCoef(1, :) とすることで、4x12行列データ ppCoefの1行目のデータだけがパラメータとして定義されます。

入力信号を1サンプルずつ遅延させた信号を4倍(デシメーションファクター)Downsampleして、それをシングルレートのFIRフィルタに入力します。

ここで使用しているDiscrete FIR Filter HDL Optimizedブロックは、HDL生成用に最適化されたブロックで、実装効率も良いとのこと。ただし、フィルタのタップ数によってレイテンシが発生します。2つ目のフィルタ出力のみに接続されているDelayブロック(Delay_timing_adj)は、フィルタごとに異なるレイテンシのタイミングを合わせるためのものです。

シミュレーションを実行してリファレンスモデルとポリフェーズフィルタに差異が無いことを確認します。  (上段がリファレンス、下段がポリフェーズフィルタ、中段がその差分)

回路規模の推定

リファレンスモデルからHDL CoderでVerilogコード生成してみます。

コード生成レポートを確認すると、

乗算器:43個

加算器:42個

になるとのこと。

次にポリフェーズフィルタからコード生成してみます。

乗算器:38個

加算器:47個

となったので、乗算器数が少し減りました。

FPGA実装

次はFPGAツールでコンパイルして回路性能を確認してみましょう。

こちらはリファレンスモデルから生成したHDLコードのVivadoでの論理合成結果。

ターゲットデバイスはKintex-7(xc7k325t-ffg676-2)に設定してあります。

下図はポリフェーズフィルタから生成したHDLコードの論理合成結果。

LUTは逆に多くなってしまっていますが、DSPブロックの使用個数はコード生成レポートどおり43個から38個に減っています。タイミングはFmax > 400MHz程度出ているようなので、とても良い結果が得られていると思います。

まとめ

MATLABを使ってポリフェーズフィルタの設計~FPGA実装を行ってみました。

FIRデシメーションを変換して、ポリフェーズフィルタで実装することで、LUTは少し多くなったものの、DSPブロックの使用個数削減の効果は確認できました。フィルタタップ数が多くなるともっと削減効果は出てくるものと思われます。