Qspice

業界では有名人らしいけど、この人がLTspice辞めてQspiceなる新しいシミュレータを作ったらしいので試してみた。

今回はC++とVerilogをシンボルとして定義できるのが新しい。

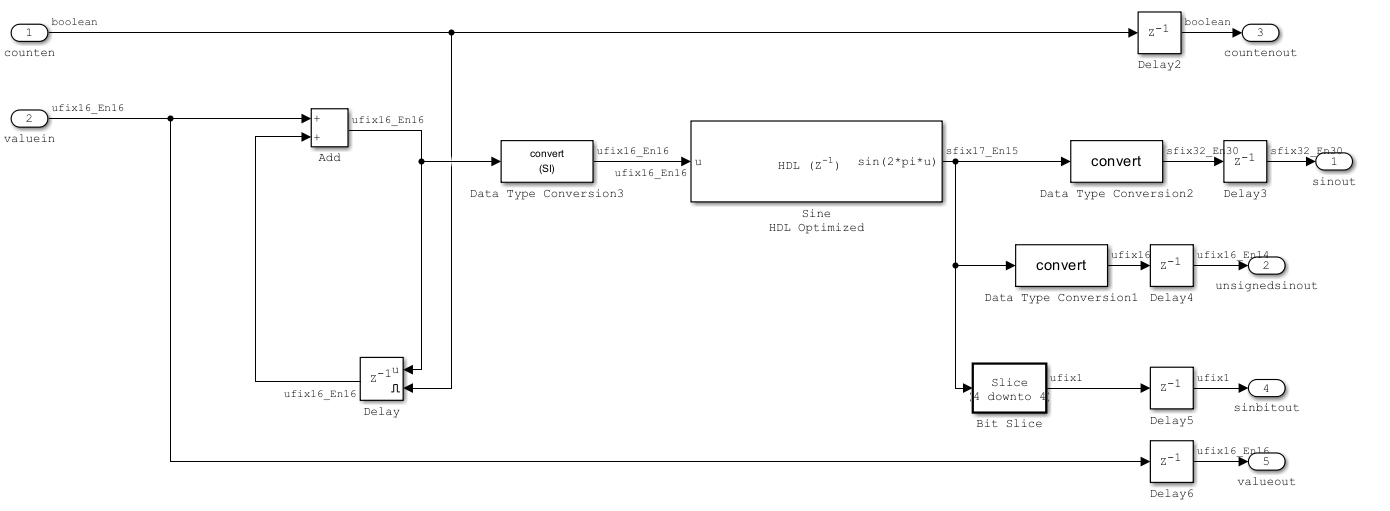

Spice系のシミュレータはビヘイビアモデルやデジタル回路との親和性が低かったけど、Qspiceは制御アルゴリズムやアナデジ混在のシミュレーションが容易にできるようになりそう。

VerilogシミュレーションはVerilatorのエンジンを使用

VerilatorはVerilogファイルを一旦マルチスレッドのC++に変換、コンパイルしてDLL化してシミュレーションするので、2つのシミュレータで連携するコシミュレーションなんかと比べて高速に動作するらしい。

Verilator自体はVerilog-A/AMSのサブセットも対応していますが、コンパイルオプションが必要で、Qspiceでは対応していませんでした。Verilatorの詳細は対応言語使用はこちら。

Verilog取り込み手順

早速だがVerilogを取り込んでシミュレーションしてみたので、その手順を説明する。

-

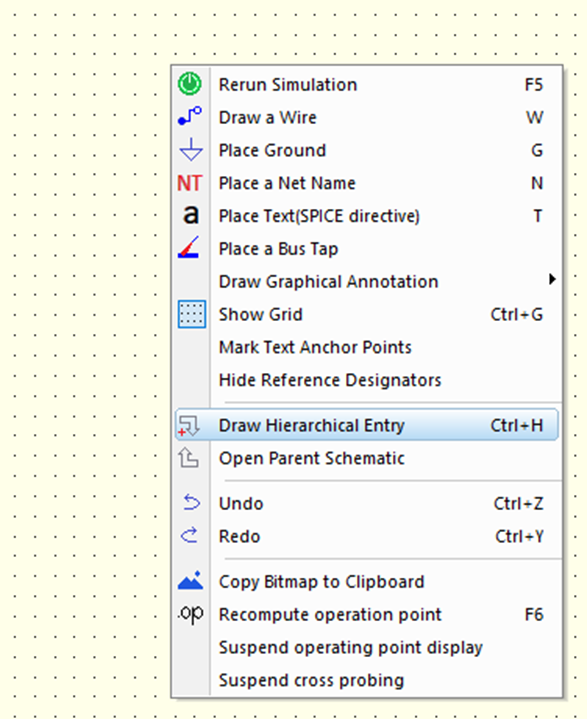

Schematicファイル上で右クリックして、メニューから「Draw Hierarchical Entry」を選択。左ドラッグすると灰色のボックスができる。

-

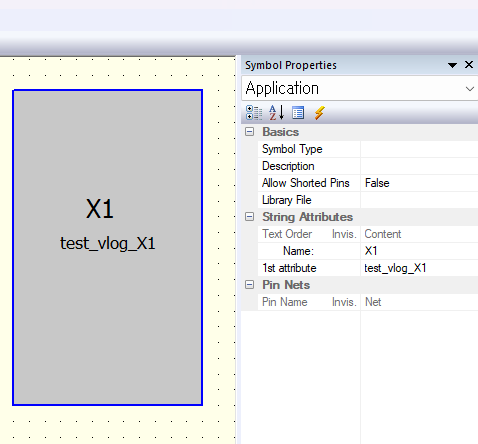

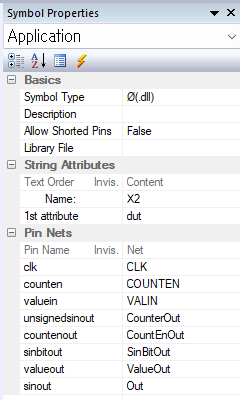

右上にプロパティが現れるので、Symbol TypeをØ(.dll)に設定。1st attribute(シンボル名X1の下に表示されている名前)をVerilogモジュール名と合わせる。

-

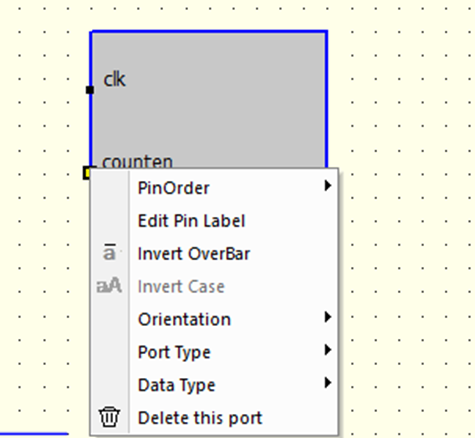

右クリックして、「Add Port」から入出力ポートを追加して、「Port Type」(入出力の極性)、「Data Type」(データ型)を設定する。

-

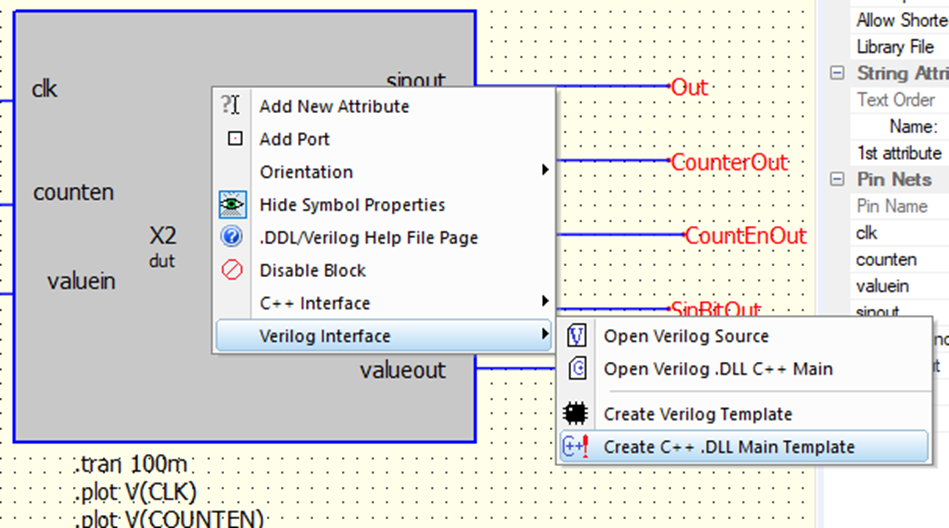

シンボル設定が終わったら、右クリックメニュー「Verilog Interface」⇒ 「Create C++ .DLL Main Template」を選択。C++のインターフェイスファイルが自動生成されるが、これは一切触らなくて良い。

-

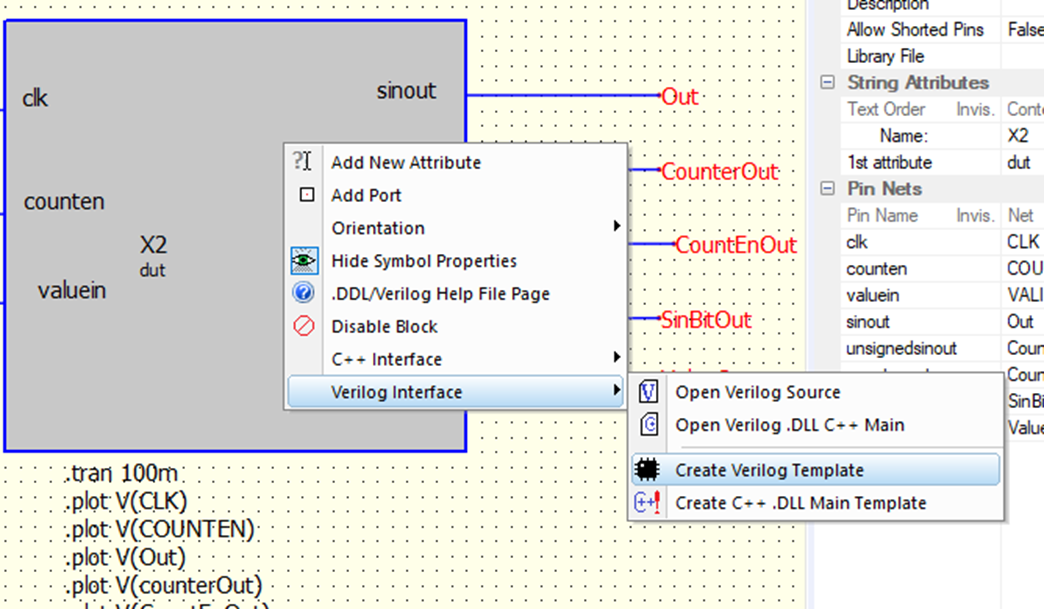

続いて同メニューから「Create Verilog Template」を選択。「Open Verilog Source」から既存ファイルを指定しても良いが、Schematic、C++、Verilogの整合性を担保するために、新規作成して既存ファイルからコピペしたほうが良いと思った。

-

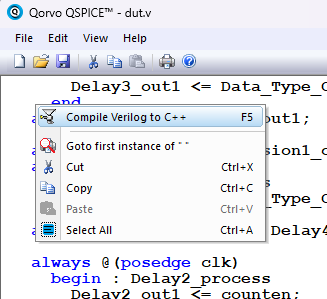

テンプレートにVerilogコードをコピペしたら右クリックでコンパイル(メニュー「Compile Verilog to C++」)する。

-

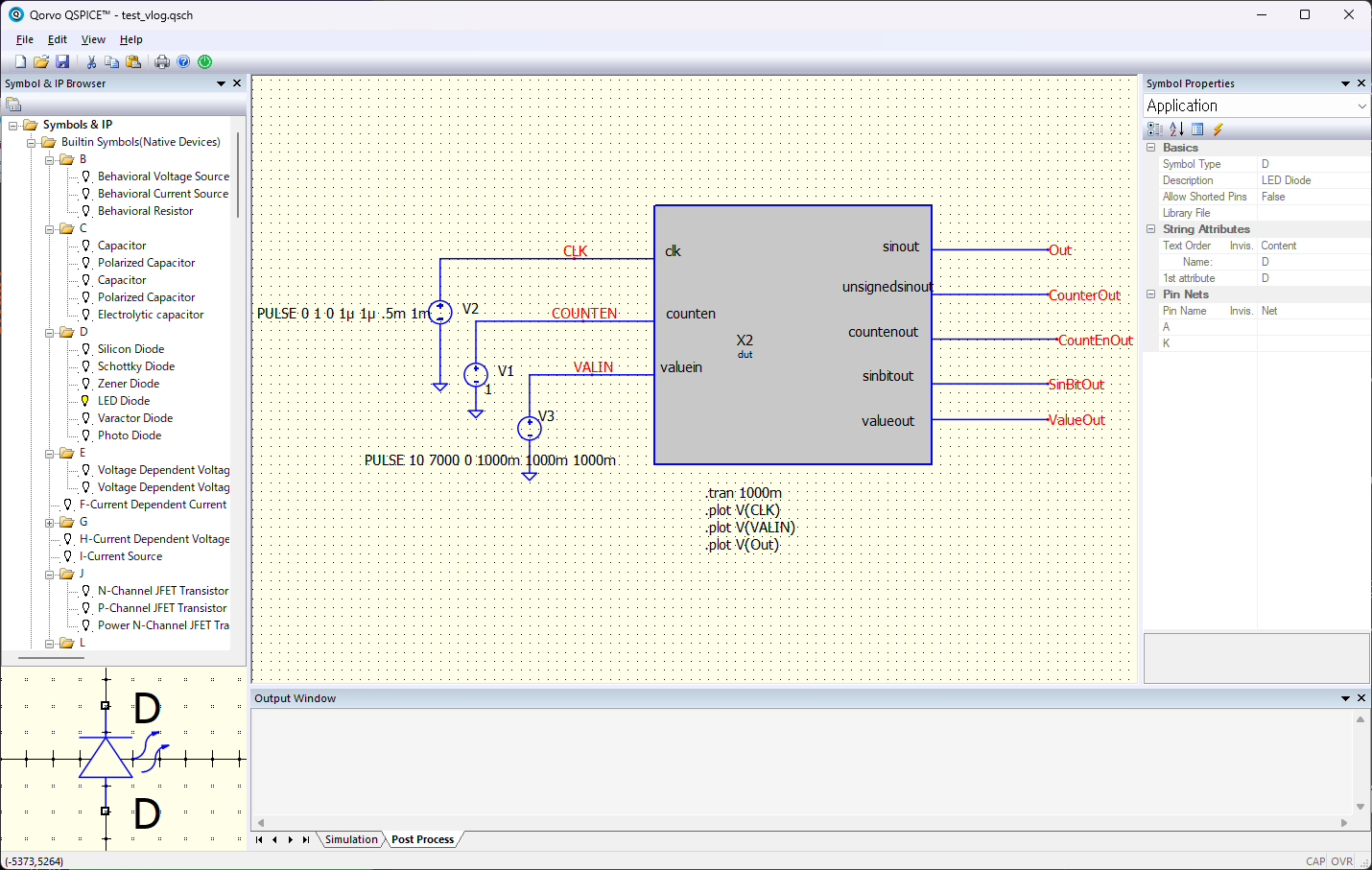

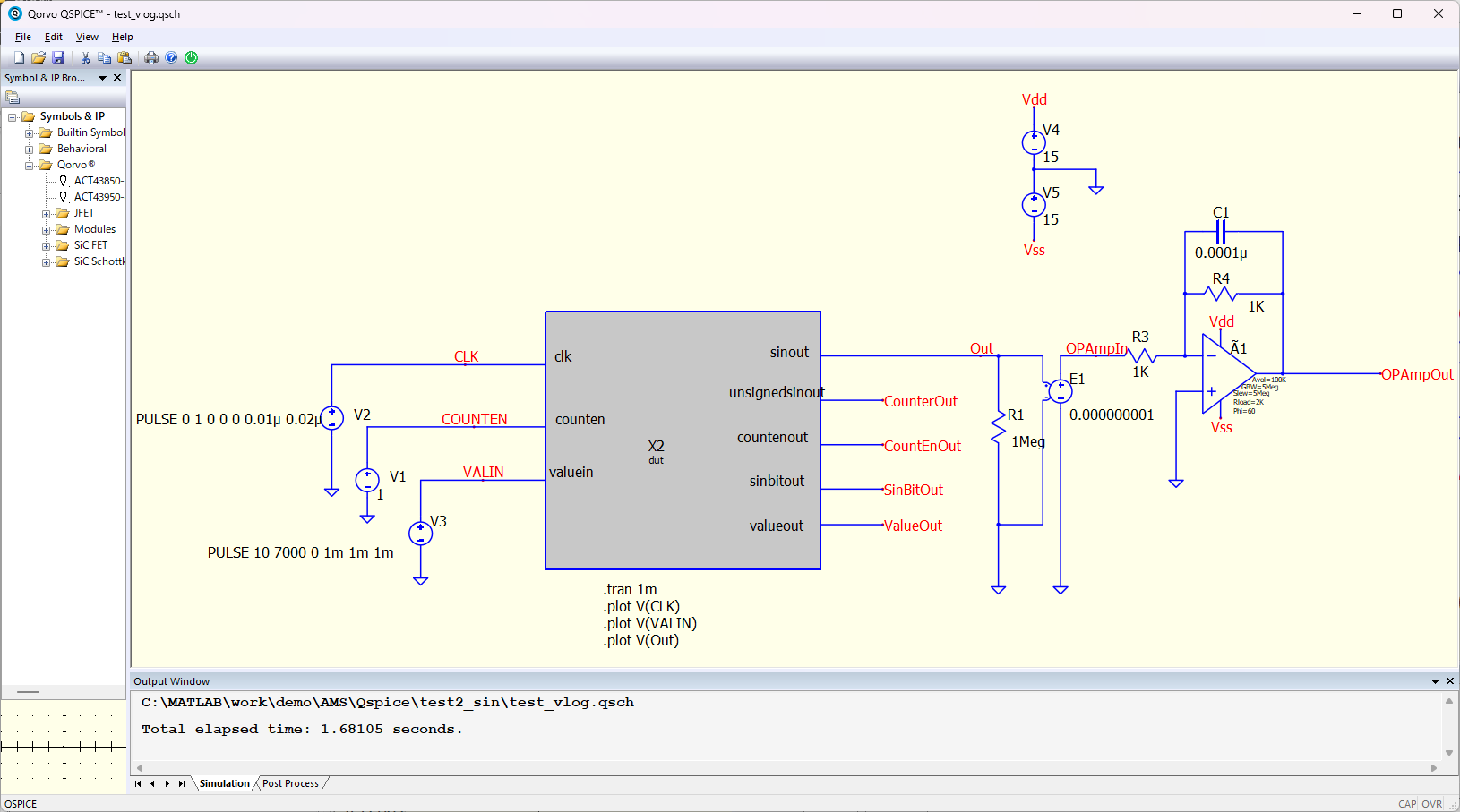

これでシンボルの設定は終了。あとは入出力の設定だが、デジタル回路にはクロックを入力する必要があるので、Voltage SourceにPulse信号の設定をしてクロック入力とした。あとはデジタル回路の出力にアナログ回路も追加して完成。

細かい説明は割愛するが、OPAmpを使ったローパスフィルタを追加した。

デジタル回路でSin波生成⇒アナログ回路でローパスフィルタという構成

-

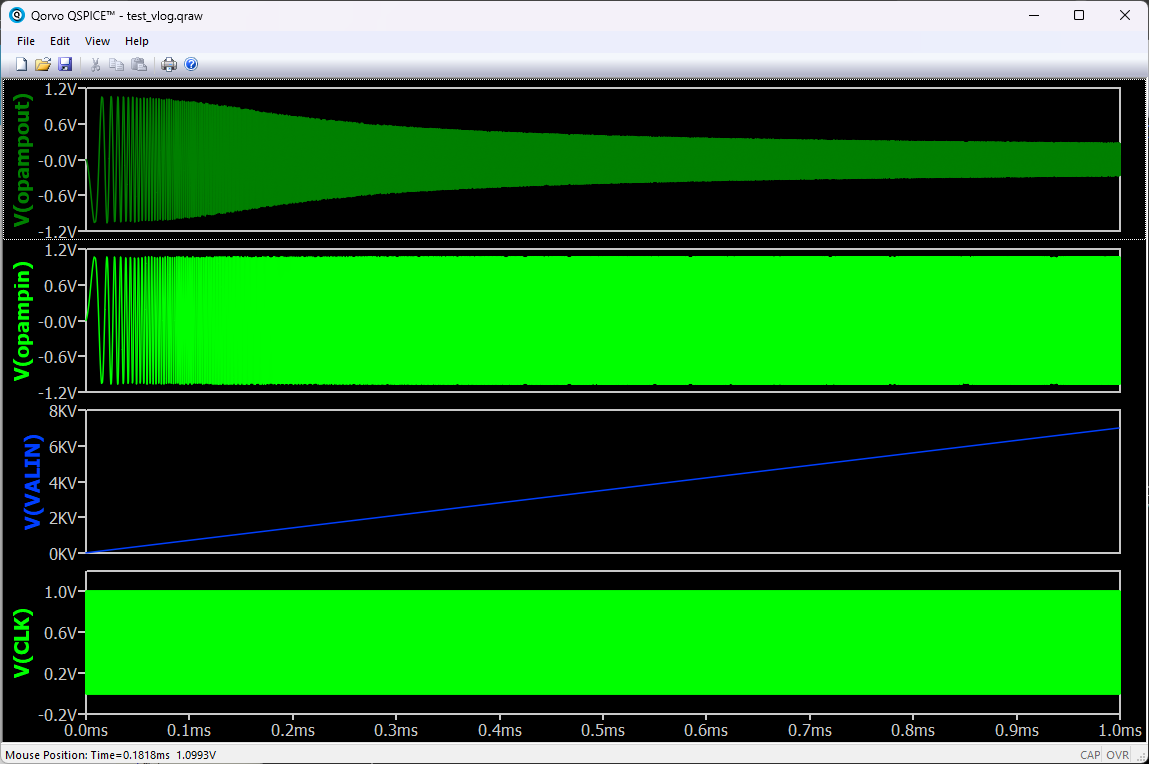

シミュレーション実行結果

下段から、クロック信号、Sin波生成デジタル回路の周波数入力値、OPAmpの入力、OPAmpの出力

所感

プラス

- すごく手軽かつフリーツールでアナデジ混在シミュレーションができるのは良い

- Verilog Interfaceブロックの設定は簡単だし、コンパイルやシミュレーションも軽い

- VerilogのエンジンVerilatorは実績があり信頼性高そうなのも良い

- C++も扱えるので回路におけるビヘイビアモデルを作成するのは簡単になりそう

- 階層化されたVerilogファイルに対応しており、同じパスにファイルを置いておけば自動的に読み込んでコンパイルしてくれる

マイナス

- データ型の設定で固定小数点データが扱えないので、例えば16bitデータなんかは0-65535の数値として出力され、アナログ回路との間に何かしら補正回路を入れる必要があった(今回の回路のVoltage Sourceがそれ)

- Bit Vector(任意のビット幅のデータ)で符号付きデータが扱えない。符号付き12bitとかよくあると思うが、それはビット幅拡張してshort(16bit)データとして扱う必要がありそう。今回はVerilog側で符号付き32bitにしてinteger(32bit)にして出力した

注意点

- データ型、特にBit Rangeを変更すると、ビット幅がおかしくなるバグがあるようなので、変更するときはポートを一度削除して、C++インターフェイスから作り直したほうが良さそう。

- VerilogはCase sensitiveなのだが、自動生成のC++インターフェイスは全て小文字で記述される。Verilogポートは全部小文字で記述するか、自動生成C++インターフェイスコードを修正するかどちらかの必要がある。

その他

おわり