⇒ 本記事に対応する最新回路図はこちらです

⇒ RETROF-16 部品実装(その1)はこちらです

⇒ RETROF-16 部品実装(その2)はこちらです

無条件HALT命令の実装/試験

ここからは、各々の機械語命令を一つずつ試験します。

具体的には試験をする機械語命令に必要な部品を実装後、手動でクロックを与え、基板上のLEDを見ながらその動きが正しいことを順次確認します。

まずは最も単純な命令である無条件HALT命令の実装/試験を行います。まず、74LS155(U26)とLED1を実装します。LED1は通常は常時点灯ですが、HALT命令を検出した時のみ消灯します。

無条件HAL命令の機械語コードは0C00(下位8bitは任意)ですから、これを主メモリ上の任意の番地(ここでは8000Hとした)に書き込み、その番地から1クロックずつ実行をします。結果は以下の通りとなります。

表中のΦはステージカウンタ(74LS163)の値を示します。他の略称は以下の通りです。

IR:インストラクションレジスタ(命令レジスタ)

PC:プログラムカウンタ

WR:ワーキングレジスタ(アドレス指定レジスタ兼被演算子レジスタ)

| Φ | アドレス バスの値 |

データ バスの値 |

IRの値 | 補足説明 |

|---|---|---|---|---|

| 0 | 不定 | 8000 | 不定 | PCの値がデータバスに放出される |

| 1 | 8000 | 8000 | 不定 | PCの値がWRに転写される |

| 2 | 8000 | 0C00 | 不定 | 実行すべき命令のコードが データバスに放出される |

| 3 | 0000 | 0000 | 0C | 命令コードの上位8bitがIRに 下位8bitがWRに転写される (WRの上位8bitはゼロクリア) |

| 4~9 | 同上 | 同上 | 同上 | |

| 10 | 同上 | 同上 | 同上 | LED1が消灯する これ以上STEPボタンを押しても Φの値は変化しない |

無条件分岐命令の実装/試験

RETROF-16は様々なアドレッシングモードを有しますが、この時点ではまだ「8bitリテラルアドレッシング」しか使えません。分岐命令は分岐先が00H番地~FFH番地に限定されます。ここでは0010H番地に0010H(10H番地に無条件分岐する命令)を書き込み、0010H番地から実行し、「無限ループ」が形成されることを1クロック単位で確認します。

尚、この命令の試験にはWRの値をPCに与える経路が必要です。74LS138(U25)と、ダイオードG5、G6の実装によりこの経路が形成されます。また他にもF22とF30の実装が必要です。

試験の結果が以下となれば正常です。

| Φ | アドレス バスの値 |

データ バスの値 |

IRの値 | 補足説明 |

|---|---|---|---|---|

| 0 | 不定 | 0010 | 不定 | PCの値がデータバスに放出される |

| 1 | 0010 | 0010 | 不定 | PCの値がWRに転写される |

| 2 | 0010 | 0010 | 不定 | 実行すべき命令のコードが データバスに放出される |

| 3 | 0010 | 0010 | 00 | 命令コードの上位8bitがIRに 下位8bitがWRに転写される (WRの上位8bitはゼロクリア) |

| 4~7 | 同上 | 同上 | 同上 | |

| 8 | 0010 | 0011 | 00 | データバスには**+1**された PCの値が表示される |

| 9 | 同上 | 同上 | 同上 | |

| 10 | 0010 | 0010 | 00 | データバスには上書きされた PCの値(分岐先)が表示される |

| 11~12 | 同上 | 同上 | 同上 | 以降はΦ0から無限に繰り返す |

実クロックでの無条件分岐命令の試験

OSC1を実装して、前項と全く同じ試験を実クロック(16.000MHz)で行います。手動クロック動作と実クロック動作の切替はSW25で行ないます。この試験の成否はオシロやロジアナがあれば完璧ですが、基板上のLEDの目視のみでも十分可能です。具体的には前項のプログラムに従った無限ループ中はアドレスバス監視用のLEDもアドレスバス監視用のLEDも殆どのステージで0010Hを表示します。データバスは稀に0011にもなりますので最下位のLEDも淡く光ります。IRのLEDは常に00Hを表示します。これらの状態を視認できれば、この試験は合格だと言えます。

| この時点で実装されているダイオード |

|---|

| D1、D2、F1~F4、F22、F30、F40~F44、G5、G11 |

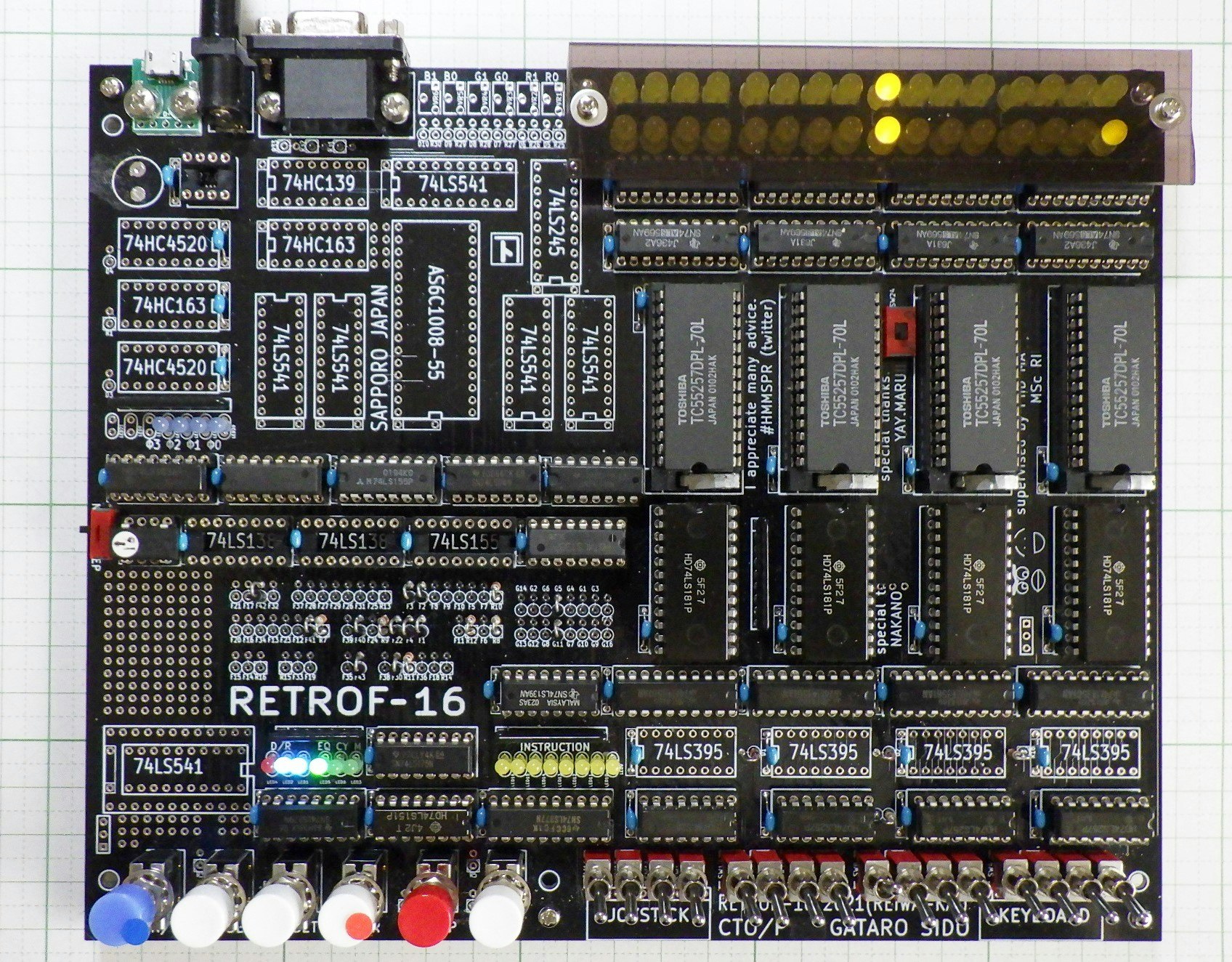

| この時点の基板外観 |

|

ロード命令の実装/試験

アキュムレータ(以下Acc)に任意の値をセットする試験です。この時点ではまだ「8bitリテラルモード」しか使えませんので、セットできる値も00H~FFHに限定されます。ここでは10(10進)を書き込みます。機械語命令コードは800AHで、これを0番地に書込み、0番地から実行します。

本試験は74LS395の実装が必要です。

試験の結果が以下となれば正常です。

| Φ | アドレス バスの値 |

データ バスの値 |

IRの値 | 補足説明 |

|---|---|---|---|---|

| 0 | 不定 | 0000 | 不定 | PCの値がデータバスに放出される |

| 1 | 0000 | 0000 | 不定 | PCの値がWRに転写される |

| 2 | 0000 | 800A | 不定 | 実行すべき命令のコードが データバスに放出される |

| 3 | 000A | 000A番地 の値 |

80 | 命令コードの上位8bitがIRに 下位8bitがWRに転写される (WRの上位8bitはゼロクリア) |

| 4~7 | 同上 | 同上 | 同上 | |

| 8 | 000A | Accの値 (不定) |

80 | データバスには**+1**された PCの値が放出される |

| 9~11 | 同上 | 同上 | 同上 | |

| 12 | 000A | 000A | 00 | データバスには更新された Accの値(=10)が放出される |

加算命令(10+20=30)の実装/試験

アキュムレータ(以下Acc)に任意の値を加え込む試験です。この時点ではまだ「8bitリテラルモード」しか使えませんので、ここでは20(10進)を加え込みます。この試験は先に前項の「Accに10をロードする命令」と組み合わせて行います。

| 番地 | 命令コード | ニモニック | 補足説明 |

|---|---|---|---|

| 0000 | 800A | LDS 10 | Accに10をセットする |

| 0001 | 8414 | ADDS 20 | Accに20を加える |

試験の結果が以下となれば正常です。

| Φ | アドレス バスの値 |

データ バスの値 |

IRの値 | 補足説明 |

|---|---|---|---|---|

| 0~12 | --- | --- | --- | 1つ目の命令の詳細は前項参照 |

| 0 | 000A | 0001 | 80 | PCの値がデータバスに放出される |

| 1 | 0001 | 0001 | 80 | PCの値がWRに転写される |

| 2 | 0001 | 8414 | 80 | 実行すべき命令のコードが データバスに放出される |

| 3 | 0014 | 不定 | 84 | 命令コードの上位8bitがIRに 下位8bitがWRに転写される (WRの上位8bitはゼロクリア) |

| 4~7 | 同上 | 同上 | 同上 | |

| 8 | 0014 | 000A | 84 | データバスには**+1**された PCの値が表示される |

| 9~11 | 同上 | 同上 | 同上 | |

| 12 | 0014 | FFFF | 84 | データバスには上書きされた PCの値(分岐先)が表示される |

最後のステップ(Φ=12)でのLEDの表示状態。

上段は加え込んだ値(10)を下段は加え込んだ結果(30)を表示している。

その他の演算命令の試験

同様の手順で他の演算の試験をします。まず、74LS181に与える演算コードを生成するダイオードマトリクスを構成する全てのダイオード(G1~G16)を実装します。

命令コードが異なるだけで試験手順は加算命令の試験と同じですので詳細は割愛します。命令コードの違いは以下の表を参照願います

|命令コード

(16進)|命令コード

(2進)|補足説明|

|---|---|---|---|

|80XX|10000000_XXXXXXXX|Accに00XXを格納|

|84XX|10000100_XXXXXXXX|Accと00XXを加算しAccに格納|

|88XX|10001000_XXXXXXXX|Accから00XXを減算しAccに格納|

|8CXX|10001100_XXXXXXXX|Accに00XXのビット反転値を格納|

|90XX|10010000_XXXXXXXX|Accと00XXのANDをAccに格納|

|94XX|10010100_XXXXXXXX|Accと00XXのORをAccに格納|

|98XX|10011000_XXXXXXXX|Accと00XXのXORをAccに格納|

|9CXX|10011100_XXXXXXXX|Accと00XXのXORの

ビット反転値Accに格納|