この記事は

自作CPU Advent Calendar 2024の12月25日最終日の記事です。

現在の進捗状況

リレーコンピュータを作ってる青兎 久遠(@Kuon_Aoto)です。

私が制作しているリレーコンピュータですが、形になってきたので、現時点での進捗状況をまとめます。

製作し始めたのは4年ほど前になります。途中、作業進まなかった時期もありましたが、やっと形になってきました。

まずは、こちらをご覧ください。

おーー!できたーーー!

— 青兎 久遠@2日目西2い11a (@Kuon_Aoto) October 31, 2024

ちゃんとインクリメントしてるーー!!!

嬉しい〜〜〜!#リレーコンピューター pic.twitter.com/E6rTqKl28N

インクリメントする回路を組むことができました。

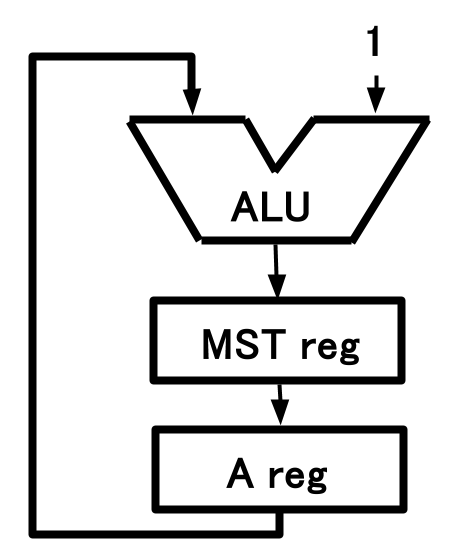

現状のブロック図にするとこのようになっています。

ALUの製作に2年、レジスタ基板に半年かかりました。

ALUの実装

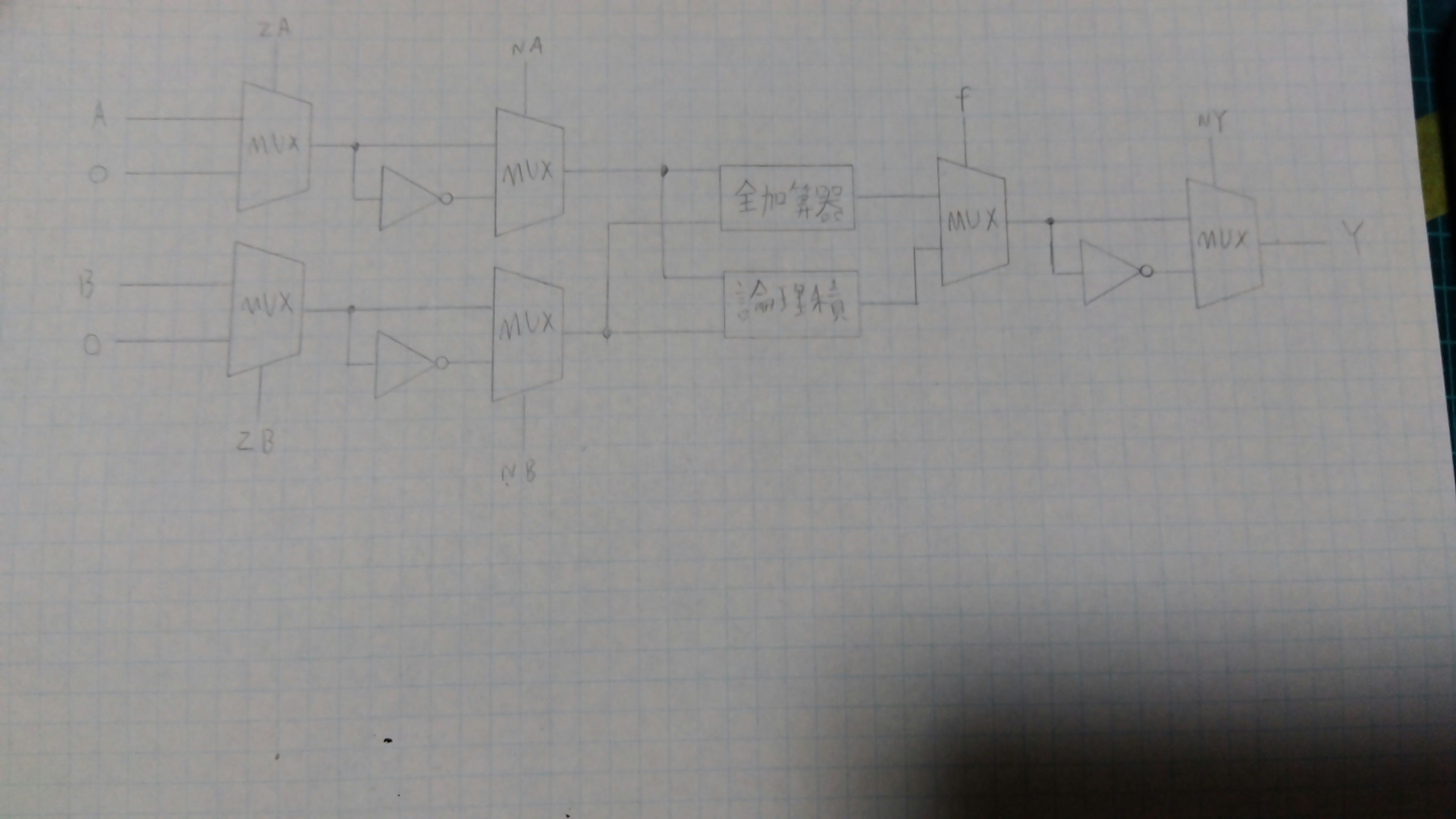

ALUの内容はO'Reillyから出ているコンピュータシステムの理論と実装を参考にしています。

これをリレーのみで組むとリレー132個必要になります。 内訳は以下の通りです。

全加算器:1bitあたり7個、7bit分計49個

半加算器:1bitあたり3個、1bit分計3個

論理積:1bitあたり1個、8bit分計8個

MUX:1bitあたり1個、48bit分計48個

NOT:1bitあたり1個、24bit分計24個

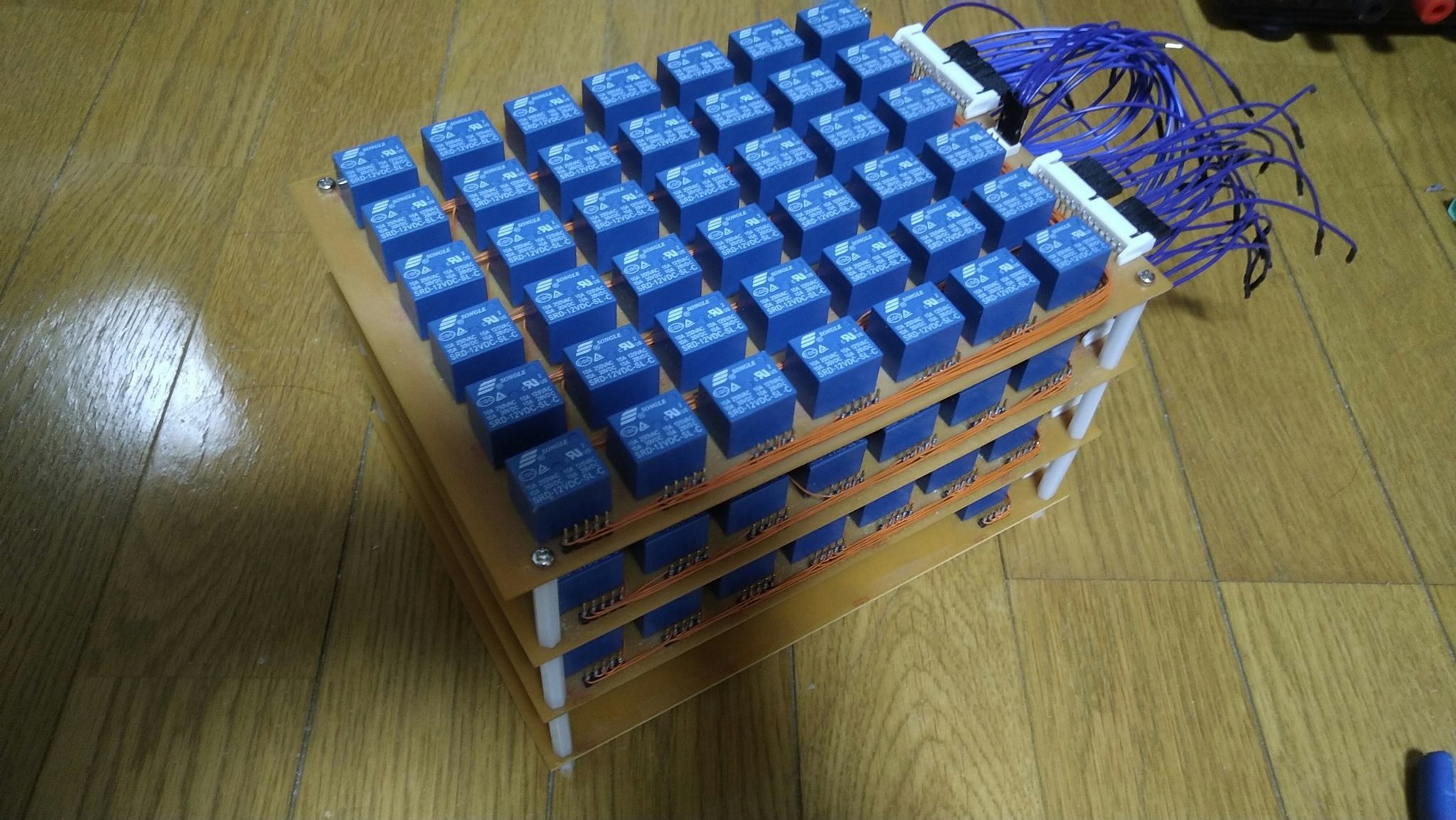

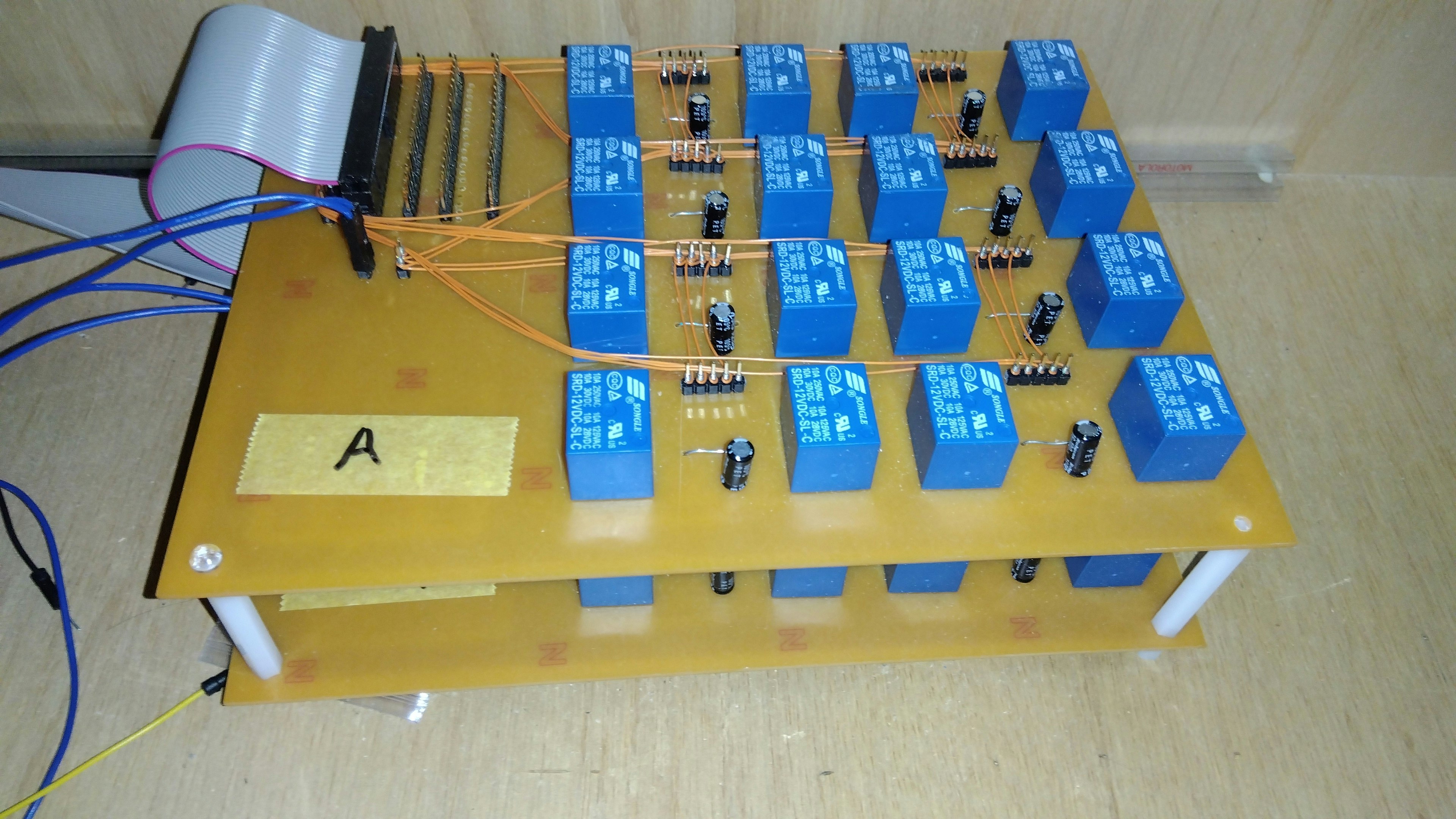

まず、一枚の基板にリレー42個載る汎用基板を作ました。

プリント基板はリレーの端子とピンヘッダを一対一に結ぶデザインにし、回路はすべてラッピングにて構成することにしました。プリント基板の利点を最大限利用しようと思いこのような実装方法にしたのですが、想像よりはるかに大変でした。特にラッピングツールが手動のものしか売っていないため、手動で行いましたが時間がかかります。

これに2年かかってました… それにリレーコンピュータにしては高機能すぎるんだと思います。

そして、基板間を繋ぐコネクタを16ピンを2つにしてしまったせいで、配線がごちゃごちゃになりました。もっと多くても良かった。

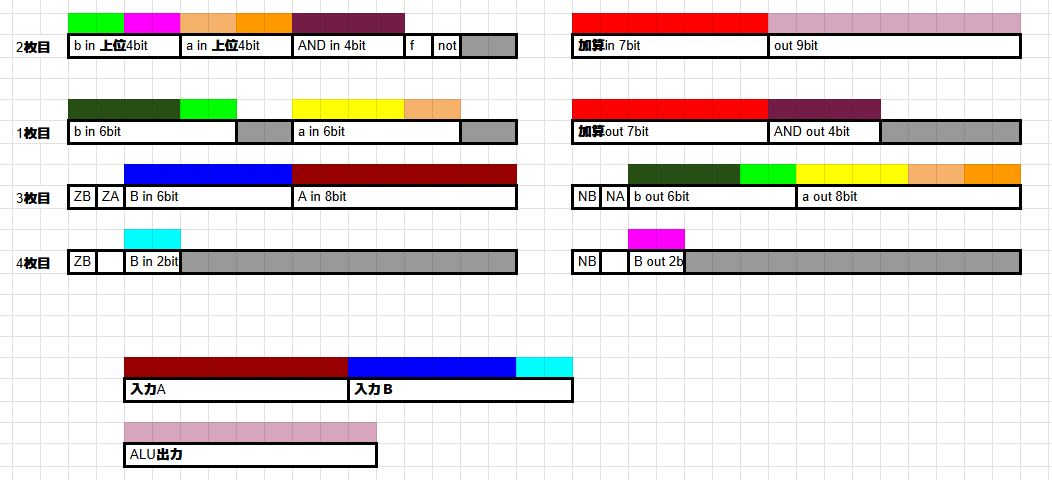

配線は以下の画像のように配線しています。同じ色のところを配線しています。

レジスタの実装

ALU同様汎用基板を作成し、そのほかはラッピングで実装することにしました。

通常、レジスタはD-FFを並べますが、リレーの使用数を削減したいので、マスター側を共通にし、レシーブ側を並べる設計にしています。

ALUの失敗を踏まえてレジスタ基板では、Dラッチは基板で配線しています。各Dラッチから基板間を繋ぐ端子までをラッピングで配線しています。そして、基板間を繋ぐ端子は40ピン×2載せました。

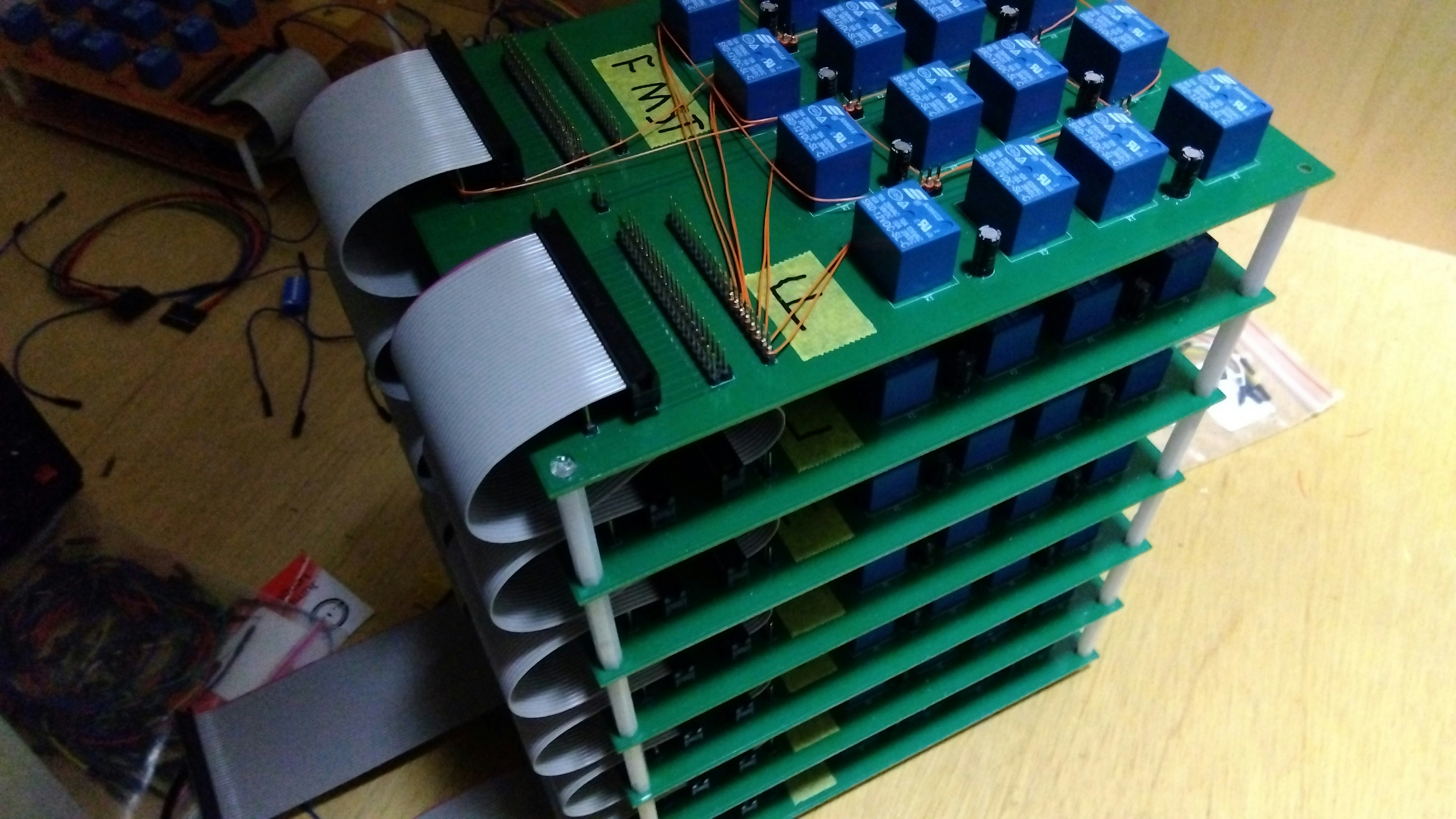

汎用レジスタはインテル8080に習いB、C、D、E、H、Lを搭載しています。この6個のレジスタに加え、フラグレジスタを縦に積むと画像のような大きさになります。高さは26cmです。

MSTレジスタ(共通のマスタ側Dラッチ)とアキュムレータは外部との接続用ピンの数を多く使うため、この二つは汎用レジスタとは別で積んでいます。

最小構成での動作

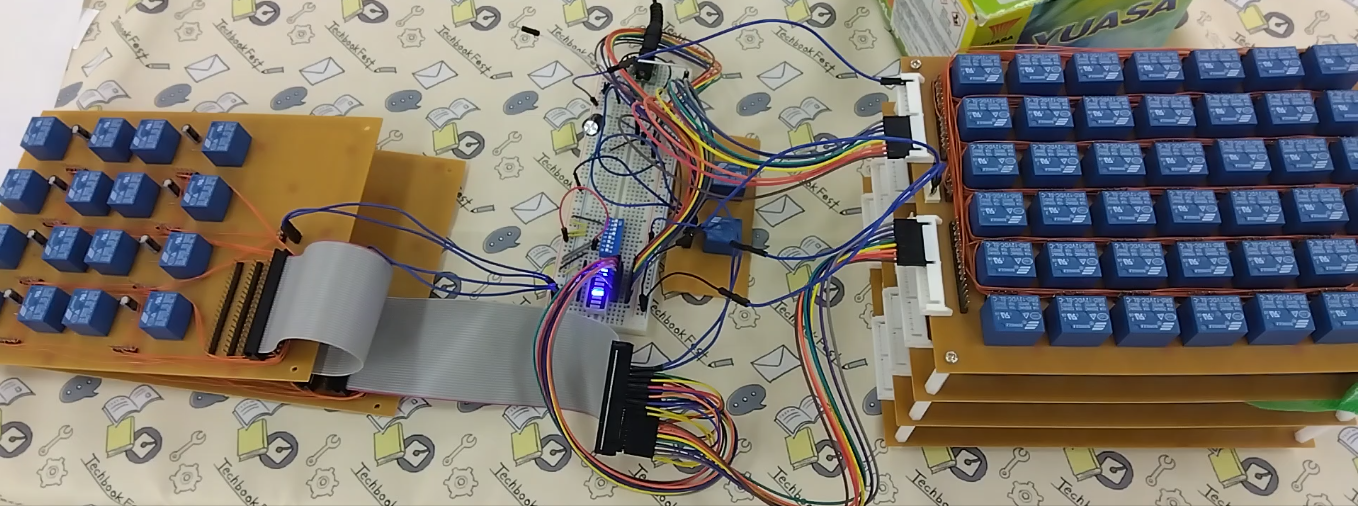

ALUとレジスタができたということで、クロックを与えれば、レジスタに保持してある値をALUに入れ、ALUからの値をレジスタに保存するという動作をすることができるようになりました。ALUの演算機能として、インクリメントやデクリメントもあるので、インクリメントし続けたりすることができるようになりました。

画像右に見えているのがALU、画像真ん中のブレッドボード付近にあるリレー2つがクロック用、画像左側がアキュムレータとMSTレジスタです。

今後の展望

まずは、レジスタ選択するマルチプレクサを制作してこうと考えています。その後、PCまわり、命令デコーダまわりと進めていく予定です。

あと、何年かかるのでしょうか…

個人で作るリレーコンピューにしては高機能すぎたかもしれません…

でも、そこそこ役に立つコンピュータにしたいので、やる気が続く限り頑張ります!日々の進捗などは、Twitter(現X)もしくは個人サイトに投稿していきますので、よかったら見に来てください。

また、C105にて実機を展示する予定です。

ブースは2日目西2い11aでお待ちしています。

ここまでの教訓

- ちゃんと設計してから作り始めよう

- リレー42個に対してコネクタ16ピン×2は少ない

- ラッピングはほどほどに

- 昔の偉大な人たちはすごい!!