この記事の概要

Intel FPGAにてNiosIIを含んだロジックを作り、Eclipseでソフトウェア開発環境を構築しました。その後FPGA側のシステムを変更してもEclipseでのBSPに反映されずハマりましたので、その対処法を書き残します。

使用したもの

開発環境:Windows10Professional

開発ツール:Quartus Prime 18.1 Lite Edition

ターゲットボード:DE0-Nano Development Board

参考書:小林優『改定2版 FPGAボードで学ぶ組込みシステム開発入門[Intel FPGA編]』技術評論社

結論

- ハマった原因:Eclipseでのプロジェクト作成を「NiosII Application and BSP from Template」で行った場合、BSPプロジェクトはsopcinfoファイルを絶対パスで参照していること。

- 対処方法:プロジェクトの作成はTemplateを使用せず、「NiosII Board Support Package」および「NiosII Application」で作成する。

- ビルド時にリンカーエラーが出るときは、NiosIIプラットフォームのソフトウェア収納用メモリサイズを大きくする。

詳細

ハマった原因

NiosIIでSDRAMを追加する際の設定ポイントという記事のあとがきで言及しましたが、NiosIIプラットフォームを変更したのになぜかEclipseでBSPを再Generateしても変更が反映されていない、という状況でかなりハマってしまいました。

その原因は、それまで練習用に使ってきたプロジェクト一式をコピペして別の場所へ用意しSDRAMの実装練習用に流用したことでした。練習用の使ってきたプロジェクトは、参考書に従ってEclipseのBSPとアプリケーションのプロジェクトは「NiosII Application and BSP from Template」で作成していましたが、どうやらこれがsopcinfoファイルを絶対パスで参照しているようです。

対処方法

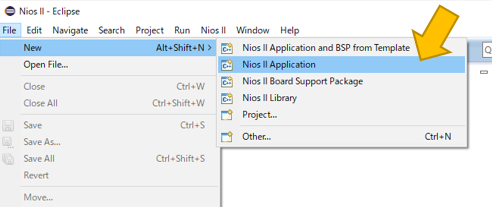

プロジェクトの作成はTemplateを使用せず、「NiosII Board Support Package」および「NiosII Application」で作成すること、これに尽きます。では早速、Templateを使わずにBSPプロジェクトとアプリケーションプロジェクトをEclipseに追加する際の設定を説明してゆきます。

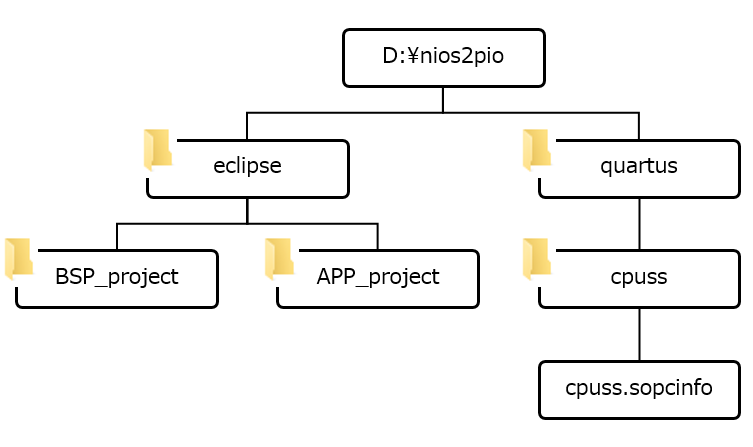

本説明の前提

フォルダ構成は下図の通りとします。quartusフォルダ以下にNiosIIプラットフォームを含むFPGAデザイン一式があり、ソフトウェアはeclipseフォルダ以下にプロジェクトを作るという設定です。

それではまず、Eclipseを起動しましょう。

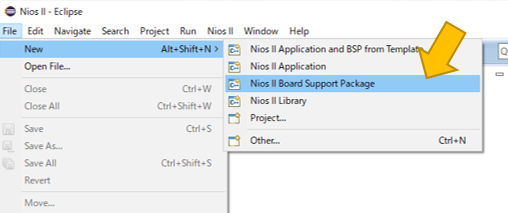

BSPプロジェクトの作成

まずはNisoIIプラットフォームに対応したBSPプロジェクトを作成することから解説します。

-

プロジェクトを作成する。

この画面でのポイントについて説明します。

1. ・・・プロジェクト名はBSPであることがわかる名前にしておきましょう。

2. ・・・sopcinfoファイルはここで指定します。

3. ・・・「Use default location」のチェックがデフォルトで入っていますが外して、Locationを好きな場所へ変更しましょう。

4. ・・・ここはデフォルトでチェックが入っていますが念のため確認しておきましょう。 -

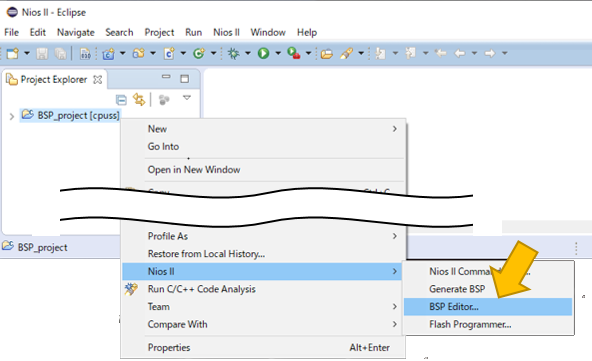

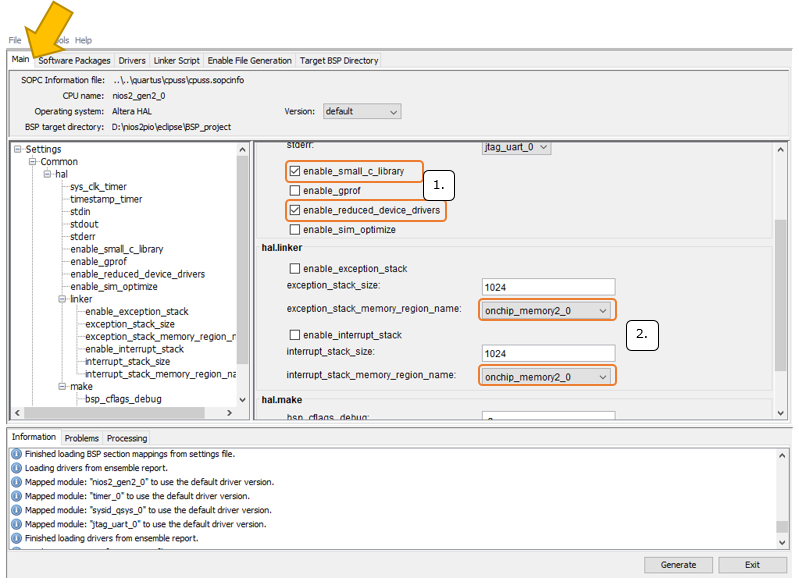

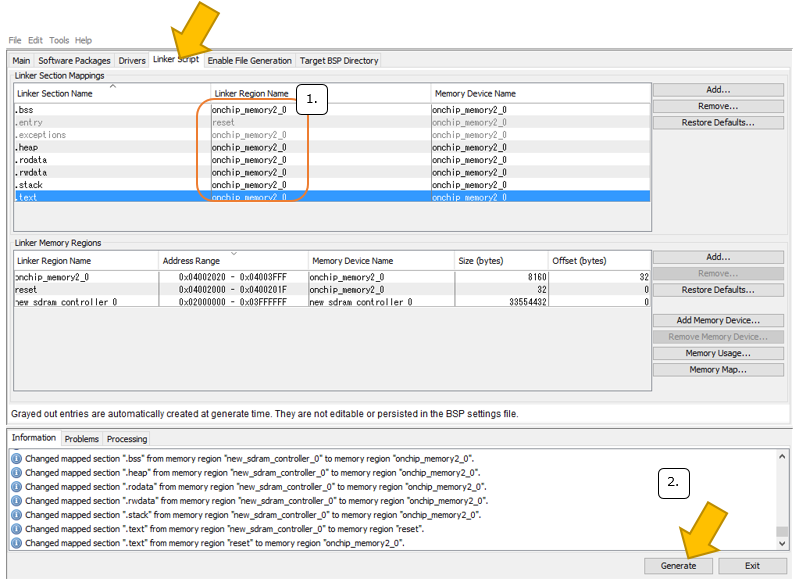

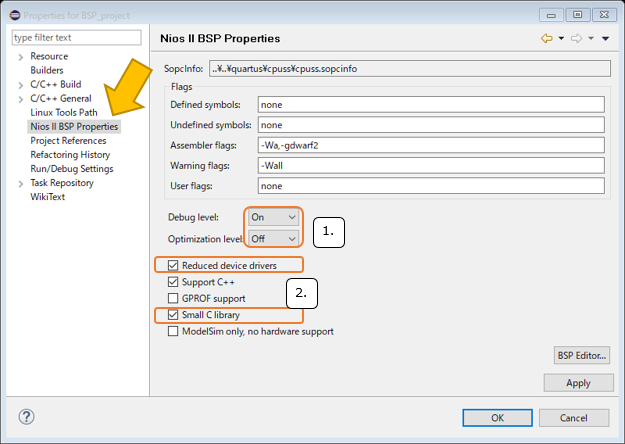

BSPの設定を変更する。

1. ・・・両方チェックを入れましょう。今回想定するNiosIIプラットフォームは、ソフトウェアを収納するRAMが16KByte程度なので、このチェックを入れないとビルド時にリンカーでエラーになります。

2. ・・・onchip_memoryに該当するものへ変更しましょう。今回想定するNiosIIプラットフォームは、ソフトウェアをFPGA内蔵RAMに収納します。

1. ・・・onchip_memoryに該当するものへ変更しましょう。ソフトウェアの各セクションの配置がデフォルトではSDRAM領域になってしまっています。

2. ・・・最後にGenerateをしてからExitしましょう。 -

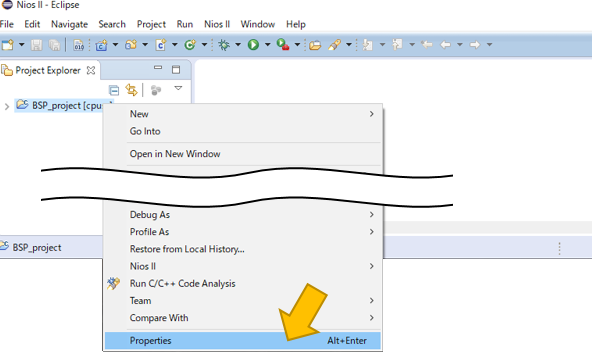

BSPの設定を確認する。

前項の「BSPの設定を変更する」が正しく出来ていれば、このようになっているはずです。

1. ・・・デバッガを使ってステップ実行等を行う場合、この設定になっていることを確認しておきましょう。

2. ・・・両方チェックが入っていることを確認しましょう。

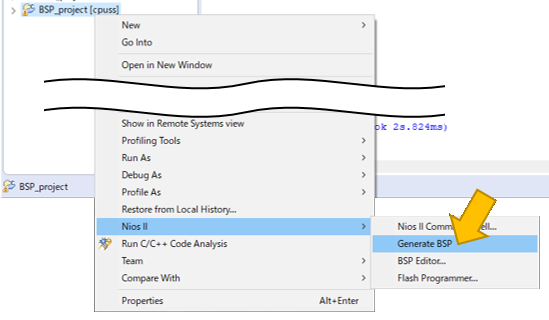

このようにして作成したBSPプロジェクトを、最後に「Generate BSP 」しておきます。

アプリケーションプロジェクトの作成

次に、作成したBSPプロジェクトを利用するアプリケーションのプロジェクトの作成について解説します。

-

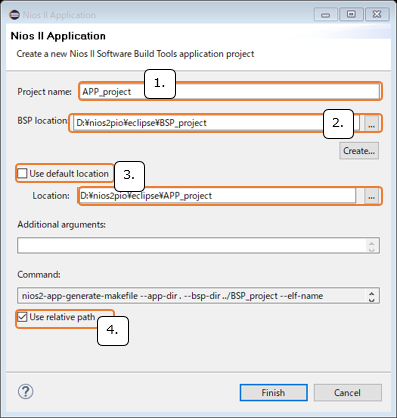

プロジェクトを作成する。

この画面でのポイントは、

1. ・・・プロジェクト名はアプリケーションであることがわかる名前にしておきましょう。

2. ・・・紐づけるBSPプロジェクトをここで指定します。

3. ・・・「Use default location」のチェックがデフォルトで入っていますが外して、Locationを好きな場所へ変更しましょう。

4. ・・・ここはデフォルトでチェックが入っていますが念のため確認しておきましょう。 -

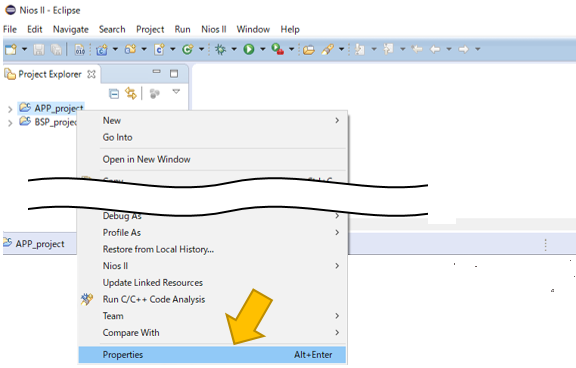

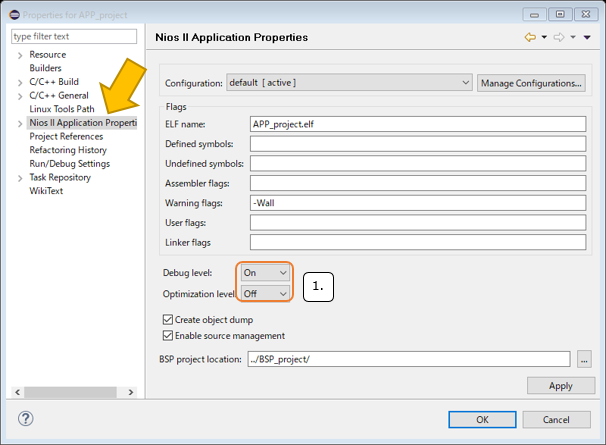

プロジェクトの設定を確認する。

前項の「プロジェクトを作成する」が正しく出来ていれば、このようになっているはずです。

1. ・・・デバッガを使ってステップ実行等を行う場合、この設定になっていることを確認しておきましょう。

このようにして作成したアプリケーションプロジェクトへソースコード等を追加して、アプリケーションの制作を行います。

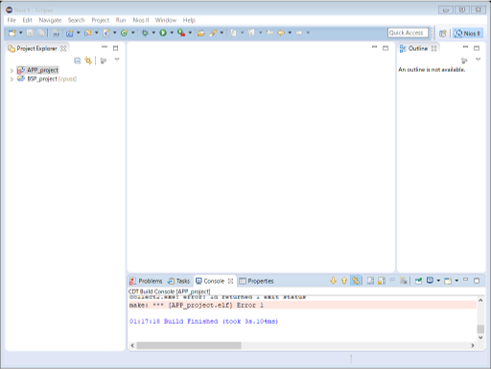

ビルドの実行

最後にもう一つハマってしまったことがあります。

アプリケーションプロジェクトをビルドするとリンカーでエラーがでてしまい、原因がわからずハマってしまいました。

エラーメッセージ的には、プログラムの各セクションについて「onchip memoryの範囲に無いよ」、との主旨なのですが、BSP設定で各セクションをonchip memoryに割り当てたはずだし・・・

色々考えて気づいた(というか思いついた)のですが、確保していたonchip memoryのサイズが小さくでプログラムが入り切らないこと、ではなかろうかと。

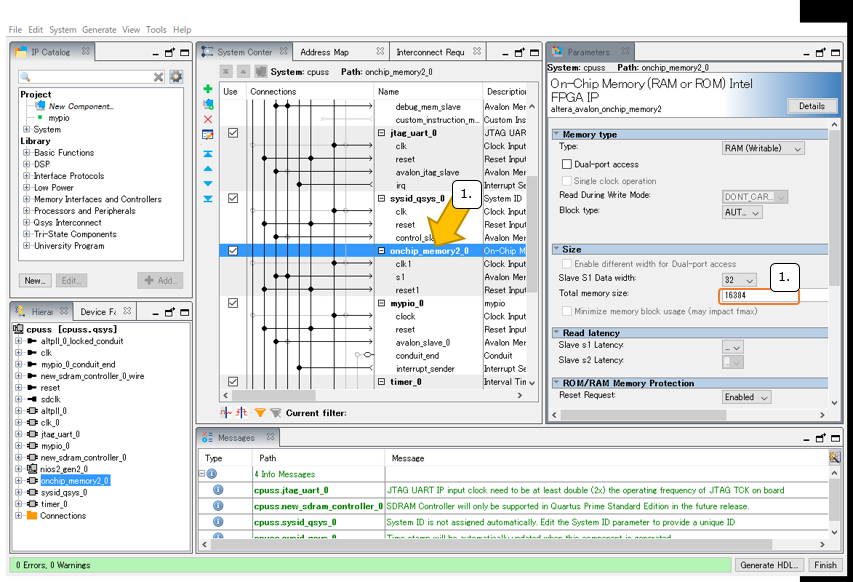

そこでPlatform Editorを立ち上げ、onchip memoryのサイズを8KByteから16KByteへ増やしてみました。

1. この行をダブルクリックすると右側に新たなペインが登場します。

2. ここを8192Byteから倍の16384Byteへ増やし、Generate HDLしました。

これで、ビルド時のエラーもなくなり、めでたくFPGAボードへソフトウェアをダウンロードしてデバッガを起動することができるようになりました。

あとがき

以上で、NiosIIプラットフォームを含むFPGA開発プロジェクトの一式を任意のフォルダへ移動させることができるようになりました。

参考書ではテンプレートを使用したプロジェクト作成のやり方しか載っていなかったので、この試行錯誤の結果を自分のためにも残して置かなければ、と思い本記事を投稿しました。

同じようにハマっている人の助けにもなれば幸いです。