その後2

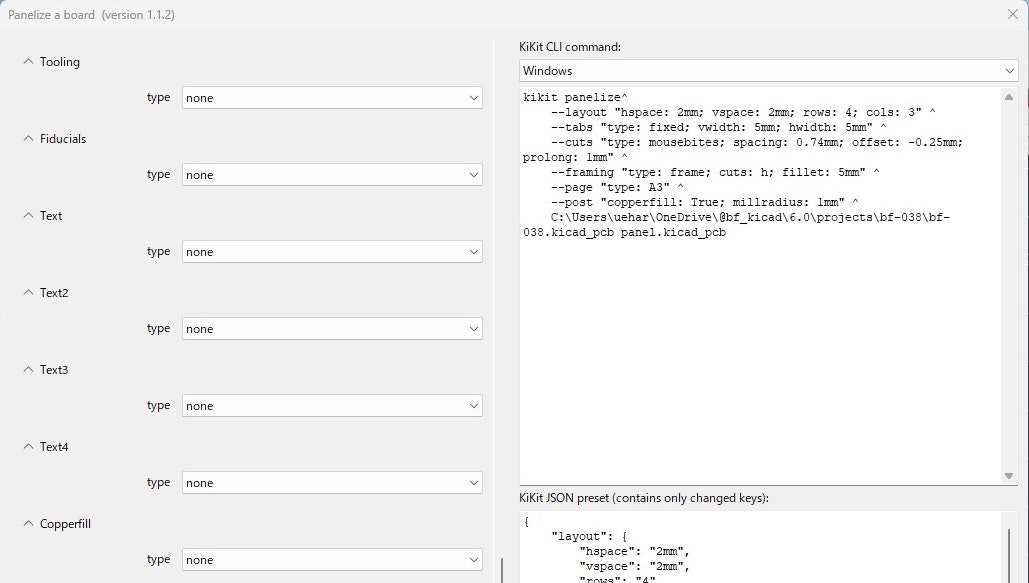

KiCad 9でKiKitを利用しています。嵌まった点です。本文のアップデートはできておりません。

(1) Output file

Panelizeの設定においてOutput fileの指定が必須となっています。Output fileには新しいファイル名を指定します。PCB Editorで開いているファイル名をOutput fileに指定すると、Panelizeがハングします。

Panelizeが完了すると、PCB Editorにはプレビュー用のデータが表示され、PCB Editorで開いているファイルにはこのプレビュー用のデータが格納されます。一方、Output fileには、リリースに向けたデータが格納されます。PCB EditorでOutput fileとして格納されたデータを改めて開き直して、リリースに向けた作業を継続することになります。

(2) Copper fill

frameやtabの強度を増すと共に、エッチング液の劣化を減らして環境保護に役立てるため、Copper fillを指定します。この指定をPostではなくCopper fillで行うようにしています。solidを指定し、クリアランスをJLCPCBの規定に倣って0.2mmとし、F.Cu, B.Cu両方に適用します。

その後..

KiCad 7においてもKikitは利用可能です。アップデートにより面付けのパラメータにも細かな変更がありますが、この記事はアップデートできておりません。その後、以下の経験をしました。

(1) Import JSON configuration

パラメータ設定において、以前セーブしたJSONファイルを読み込むことが可能です。思わぬ設定ミスで悩むことになるので、別のプリント基板のJSONを読み込むことは避けた方がよいと思います。項目は多いですが設定が必要な項目は少ないので、新規設計のプリント基板には最初から設定した方が間違いが少ないと思います。

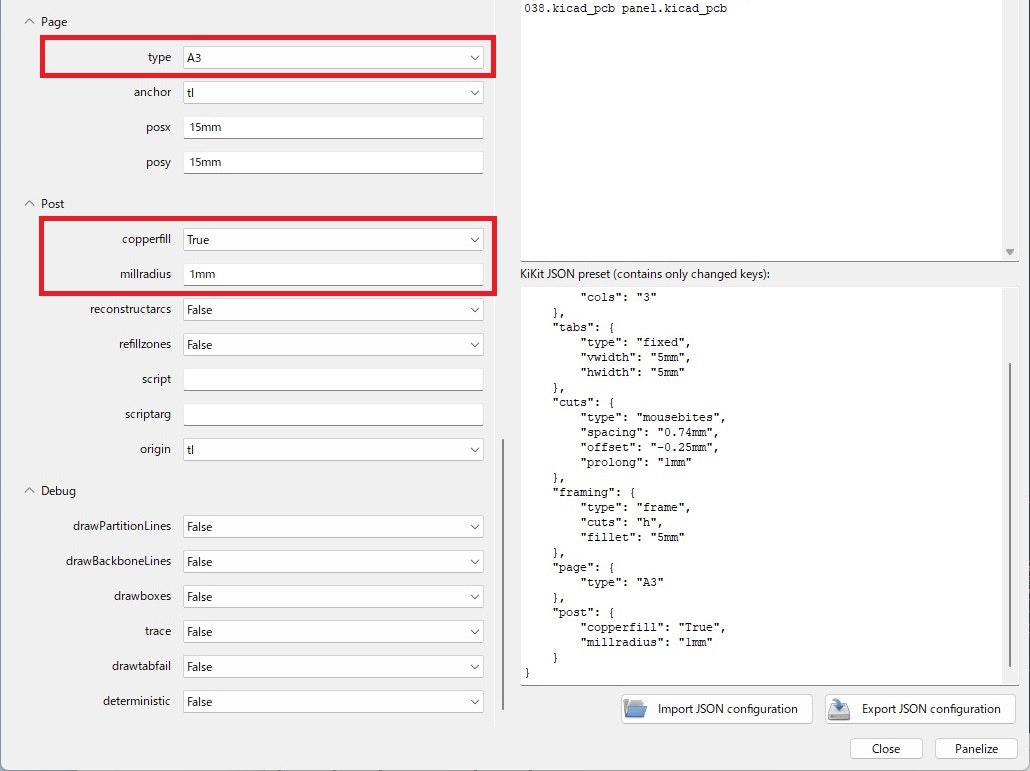

(2) Post - millradius

Post - millradiusを例えば1mmと設定すると、プリント基板の外形の凹んだ部分(ポケット)のR=1mm以上に修正されます。JLCPCBのパネライズ仕様ではパネル間スペースは2mm以上必要とあります。製造上の都合からも、R=1mmで元のプリント基板の外形を設計すべきでした。

概要

- JLCPCBのEconomic PCBAサービスの枚数制限緩和にはMouse bitesによる面付けが有効です。

- KiCad 6のKiKitプラグインでMouse bitesによる面付けを自動化できます。

- JLCPCBのPCBAオーダーのページで、BOMやPick&Placeを修正できます。

1. はじめに

プリント基板(PCB) の量産では、コスト削減のため複数のPCBを集めて1枚にまとめる 面付け(Panelization) が一般的です。PCB製造業者は、枚数の少ない試作サービスなど、異なる依頼元の複数のPCBを1枚の大きな板に面付けし効率化している様です。依頼元レベルでは、面付け済の製造データを製造業者に渡すことによって、製造業者から見た実質的な製造枚数を減らすことができます。30枚以下など少量の場合は、基板の大きさによる価格上昇や格安サービスの適用可否などの条件が絡んで必ずしも価格的なメリットは得られない様です。

PCB実装(PCBA)サービス では、PCBA作業が依頼元の製造データ単位になります。面付けにより製造業者の提供する格安サービスの枚数制限を緩和できます。

面付けに限りませんが、PCBに 捨て基板(frame, edge rails) を設けることができます。PCBの端まで部品を実装できる様になり、製造業者が付与する識別記号や製造に必要な位置決め用の穴や基準マーク(fiducial)を捨て基板に追い出すことができます。

- PCB(Printed Circuit Board)

- PCBA(PCB Assembly)

2. JLCPCBで面付け

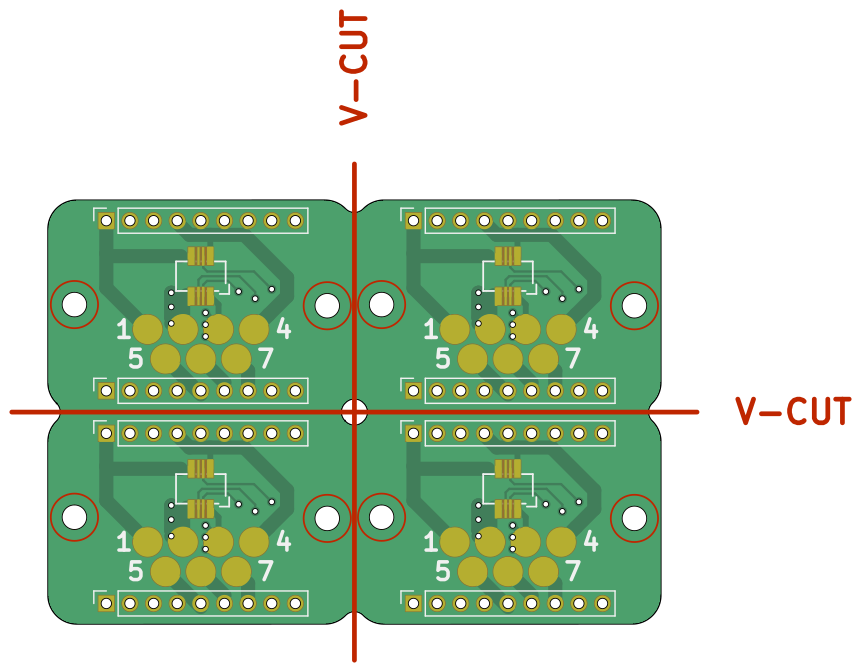

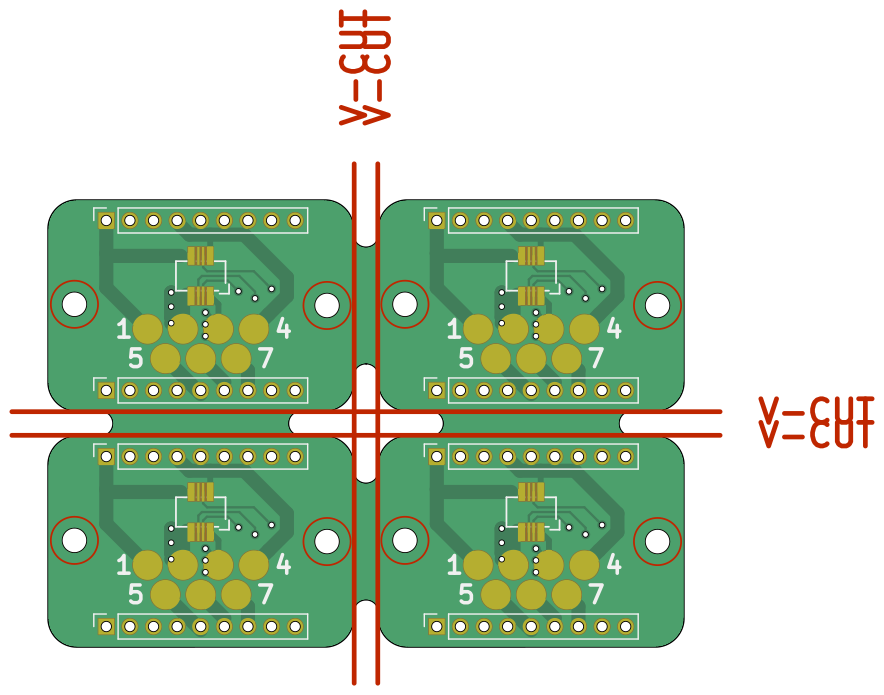

JLCPCB1は中国のPCB製造業者です。Makersを対象としたPCB/PCBA試作サービスも充実していて、依頼元による面付けにも対応しています。個々のPCBを切り出すための形状としては、V-cut2とMouse bites3が規定されています。

V-cut

PCBを折り取る溝(V-cut)を作り込みます。V-cut専用の機械へ投入するため、面付け済基板の最小サイズ(70×70mm)が規定されています。面付け済基板の水平または垂直方向で端から端までの直線の溝にする必要があります。折り取ったPCBの端面に毛羽立ちが残ります。

**PCBの角を丸くするなどV-cutを曲線の接線にするには工夫が必要です。**PCB間の外形加工に必要な隙間には最小値(2mm)があります。PCB間に捨て基板を設け、捨て基板との接線にV-cutを設けるなどの方策があります。これらは依頼元が製造データに作り込む必要があります。

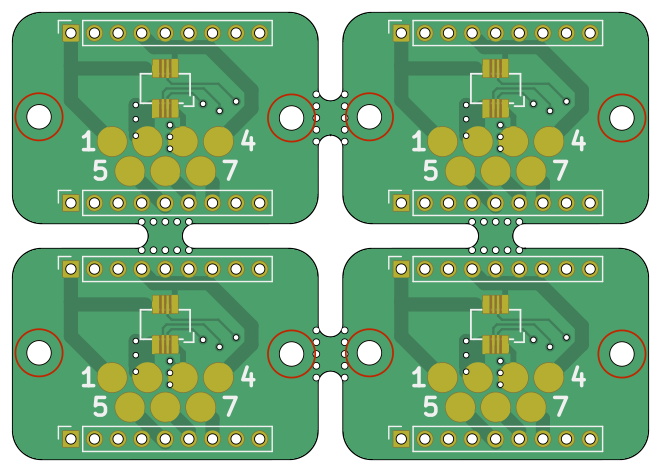

Mouse bites

PCB間に隙間を設け、PCB間をtabで接続します。tabに切手の様な小さな穴(stamp-hole)で切り取り線を作り込みます。PCB間の隙間の最小値(2mm)、tabの長さの最小値(5mm)、stamp-holeの推奨値(大きさ0.5-0.8mm, 隙間0.2-0.3mm)が規定されています。tabを折り取った跡にギザギザが残ります。ギザギザを外形線内に収めるためにはstamp-holeをPCB内に引っ込める必要があります。外形を滑らかにする場合は、stamp-holeをPCBの外に出してギザギザをグラインダーなどで削ります。

Frame, Edge rails

PCBAで使用するチップマウンタやリフロー装置のガイドレールに載せるため、edge railsの幅の最小値(3mm)が規定されています。JLCPCBでedge railsを付加する場合は5mmとあります。

面付け済基板の4辺をedge railsで囲む場合は、edge railsにも最初に折り取るためのstamp-holeが必要です。

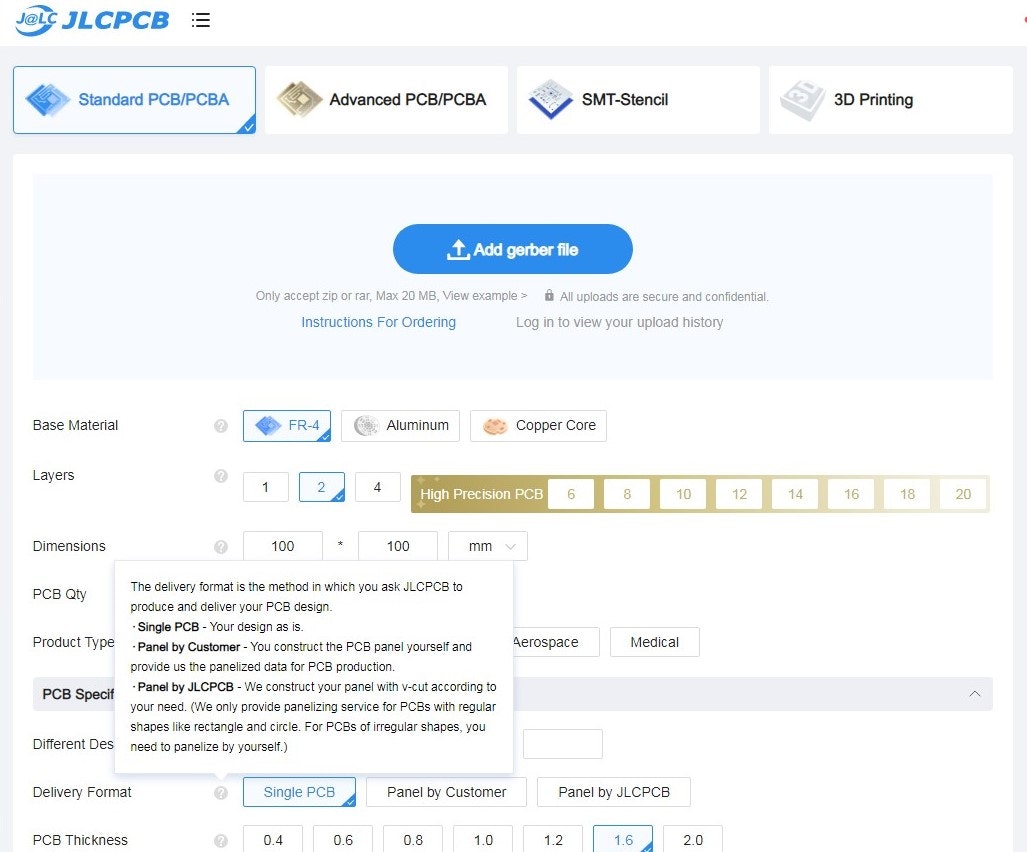

PCB製造での面付け指定

依頼元が面付け済みの製造データを提供する方法(Panel by Customer)とJLCPCBに面付けを依頼する方法(Panel by JLCPCB)があります。"Panel by Customer"はそのまま製造されます。"Panel by JLCPCB"はV-cutのみであり、四角や丸などのシンプルな外形に限られます。PCBは隙間ゼロで並べられます。丸い形状もV-cutとの接する部分の滑らかさについては妥協が必要と思います。

Economic PCBAサービスでの面付け条件

Economic PCBA4は、実装は片面のみで50枚以下(条件に依っては30枚以下)などの制限付きの格安サービスです。面付けできるのはMouse bitesのみ です。したがって、"Panel by Customer"である必要があります。

edge railsは必須ではありません。edge railsがない場合、JLCPCBが識別記号や位置決め用の穴をPCB上に追加します。edge railsがある場合、これらをedge rails上に追加します。

面付け済基板はedge railsを含め最大250x250mmです。

JLCPCBでの面付けのまとめ

Economic PCBAサービスの枚数制限(30-50枚)を超える場合、Mouse bitesによって250x250mm以下に面付けしたデータを依頼元が作成する必要があります。

3. KiCad 6

KiCad EDA5は、無料で使用可能なPCB CADソフトウェアで、Makersにも広く普及しています。最新のKiCad 6に対応する説明書としては、公式ドキュメントのほかに「Kosaka.Lab.出版掛」提供の 『KiCad Basics for 6』6を利用しています。

- CAD(Computer Aided Disign)

- EDA(Electronic Design Automation)

4. KiKit

KiKit7はKiCadのプラグインです。機能の1つが面付けです。examples.md8に具体的でわかりやすい説明があり、画像を引用しています。『KiCad Basics for 6』6にも説明があります。

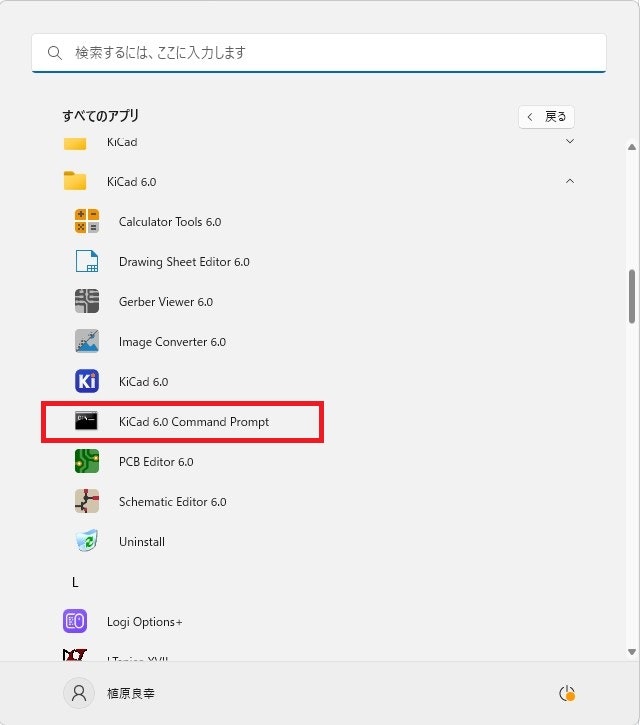

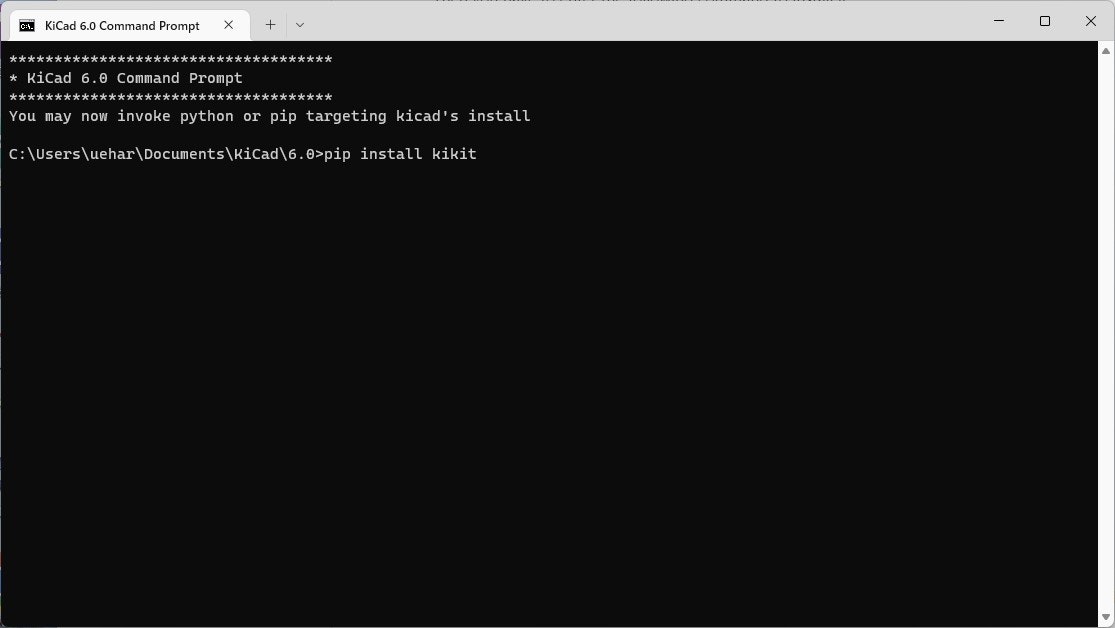

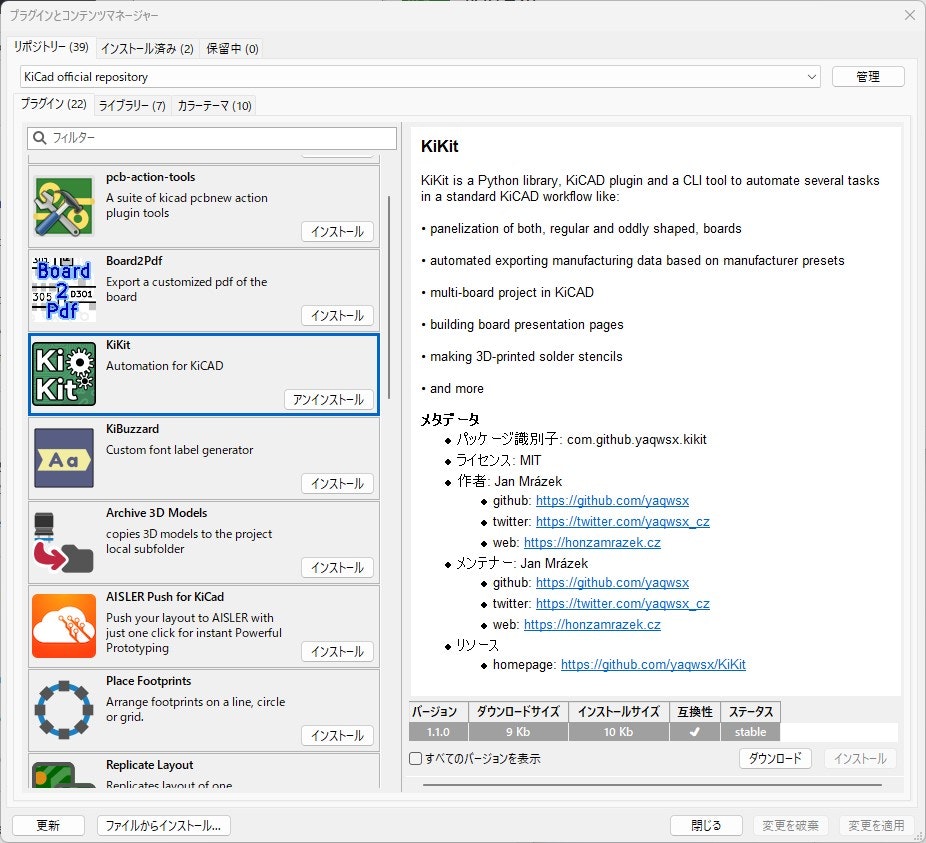

インストール

KiKitのInstallation9の説明に従い、Pythonパッケージをインストールします。以下はWindows11の例で、KiCad Command Promptでpip install kikitを実行します。

続いて、「プラグインとコンテンツマネージャーPCM(Plugin and Content Manager)」でダウンロード、インストールを行います。

Mouse bitesによる面付け

面付けの設定をGUIで行う説明がpanelizeGui.md10にあります。個々の設定項目の説明は、panelizeCli.md11 にあります。

GUI(Graphical User Interface)

CLI(Command Line Interface)

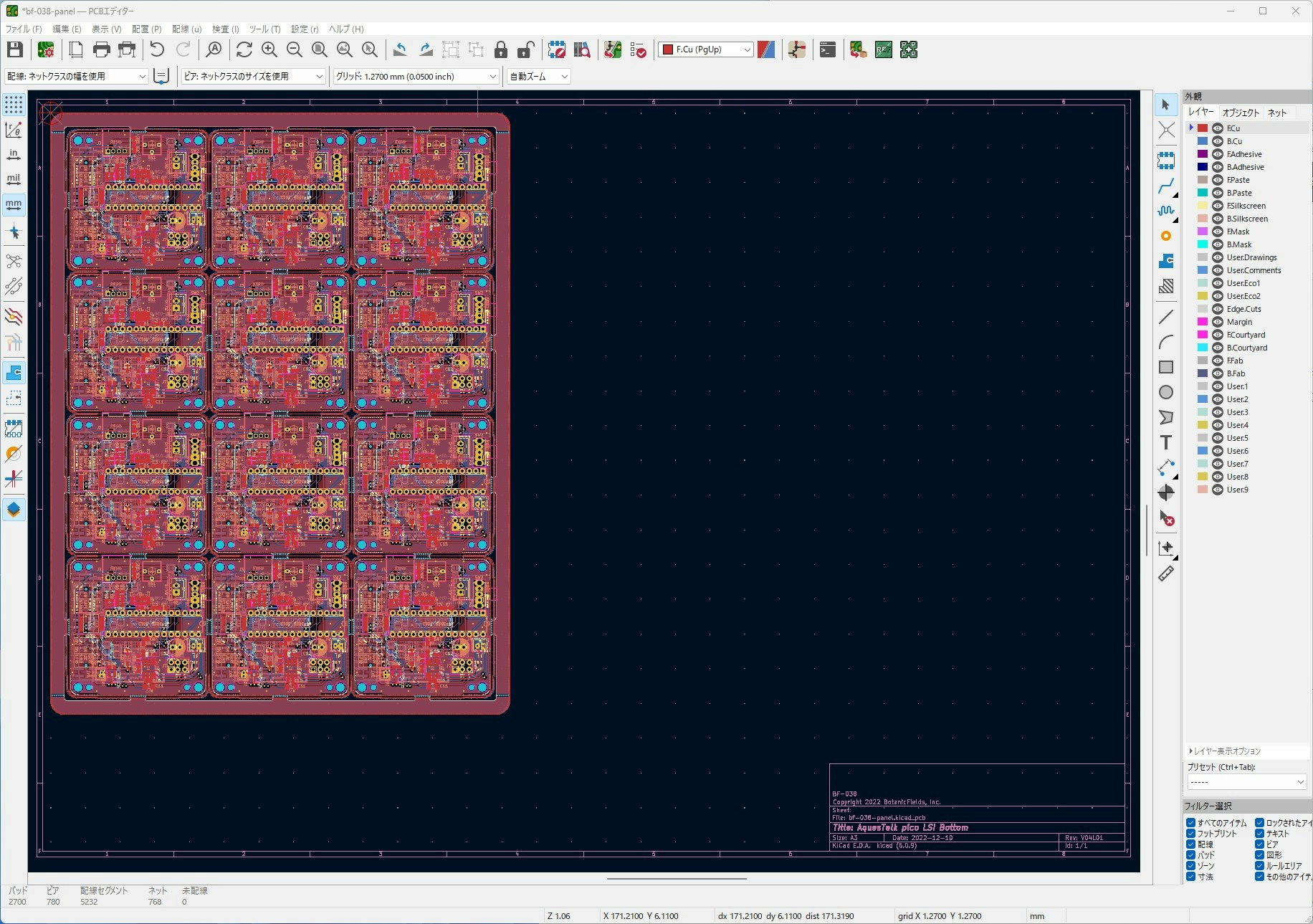

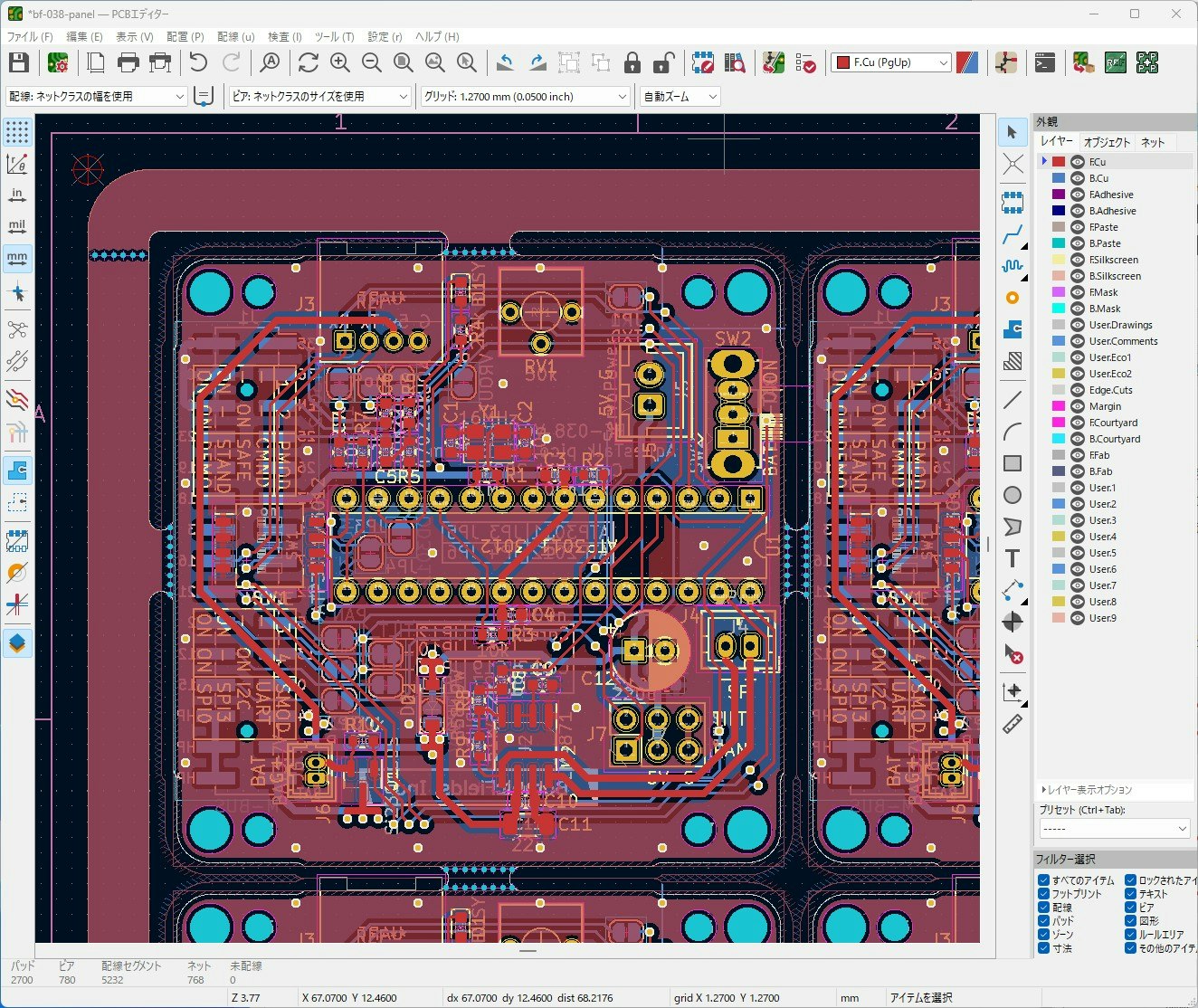

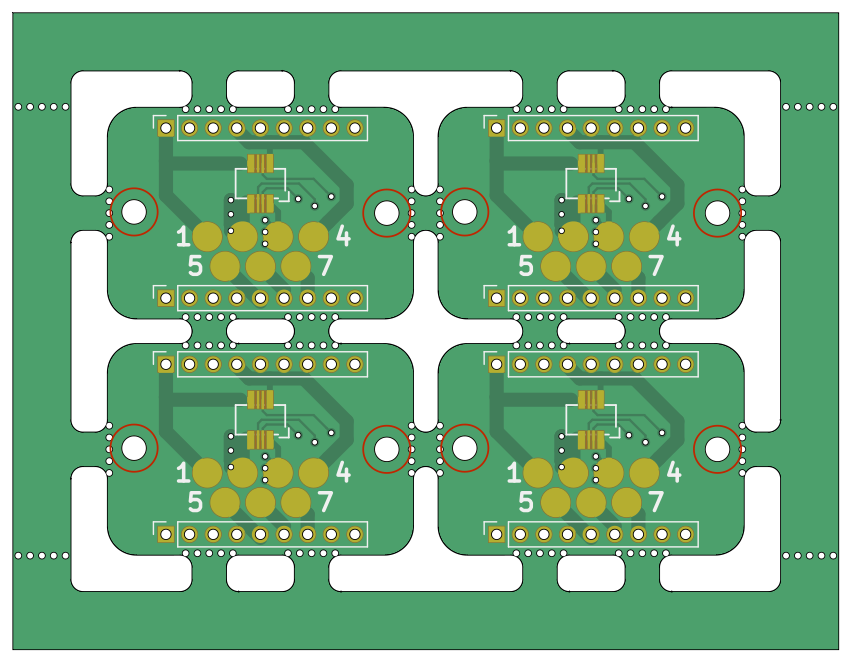

5. Kikitによる面付けの例

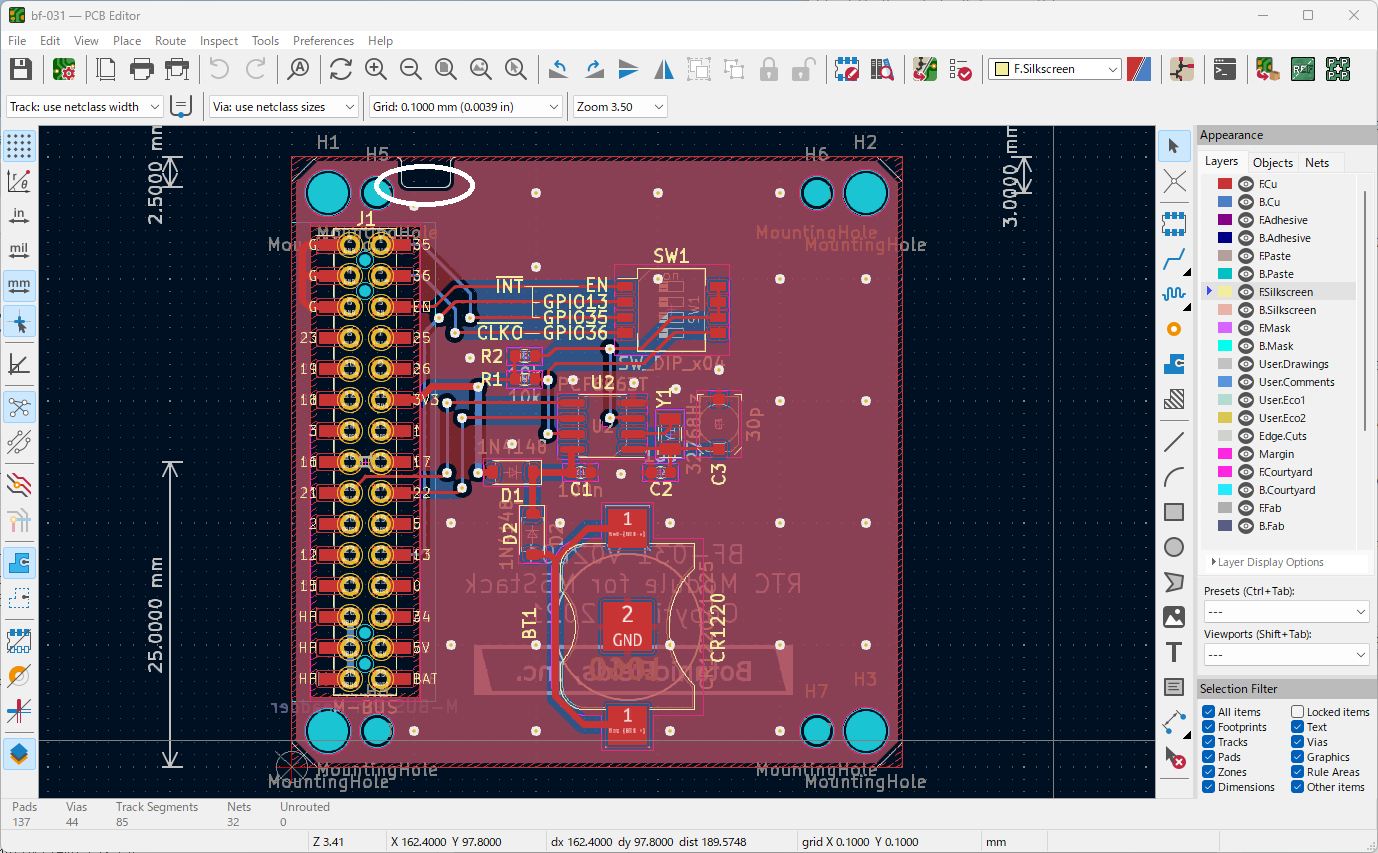

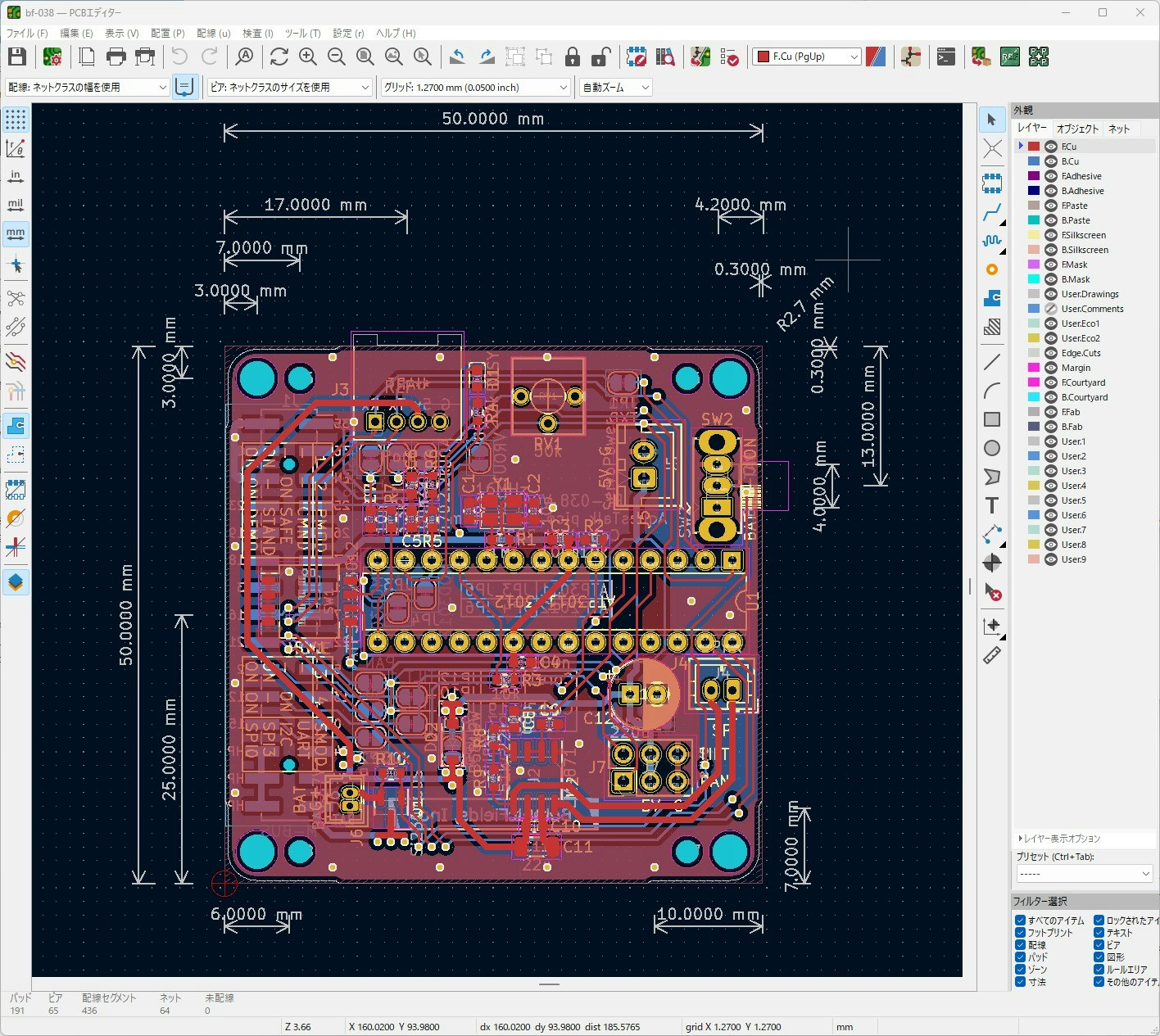

(1)PCBの準備

具体例として以下のPCBをKiKitのGUIで面付けしてみます。面付けに先立ち、PCBの外形線からはみ出しているシルクを、面付けしたPCBに被らない様に修正 しました。PCBエディタ上でのfootprint修正は、このPCBのみに反映されます。

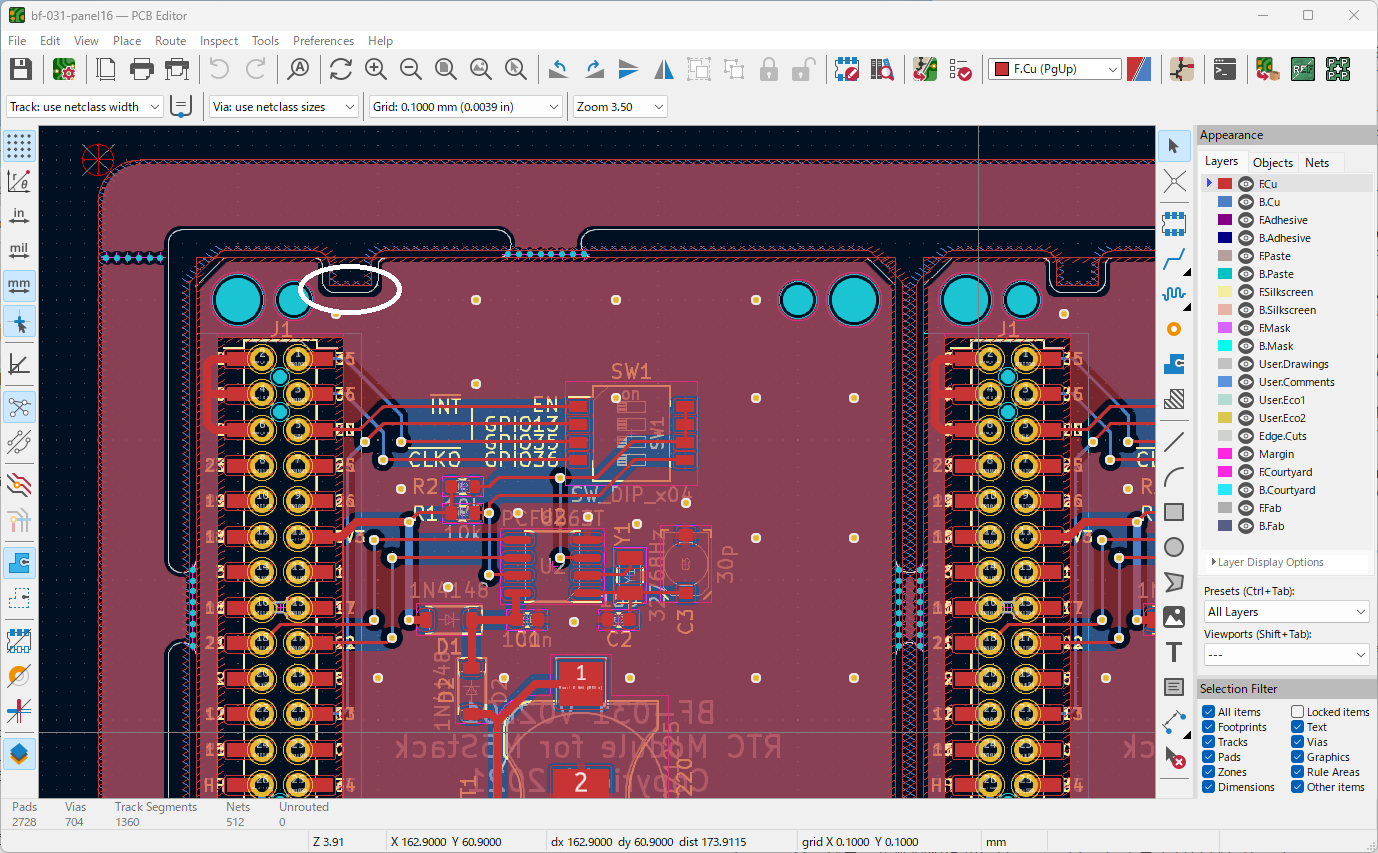

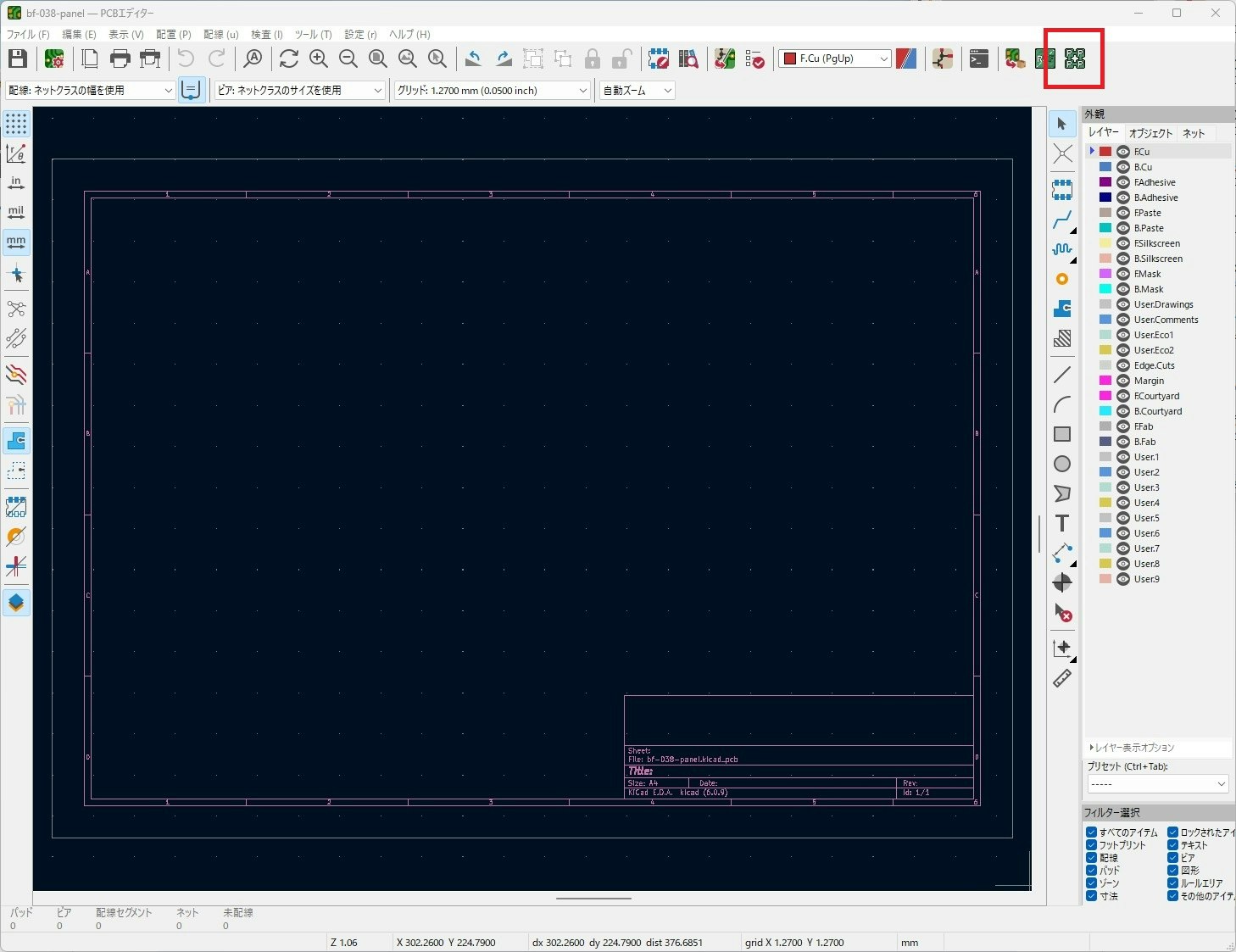

(2)面付けプロジェクトの新規作成と面付けの開始

面付け済の基板データは、新規プロジェクトとして作成します。新規プロジェクトでPCBエディターを起動し、"KiKit: Panelize PCB"アイコンをクリックします。

(3)面付けの指定

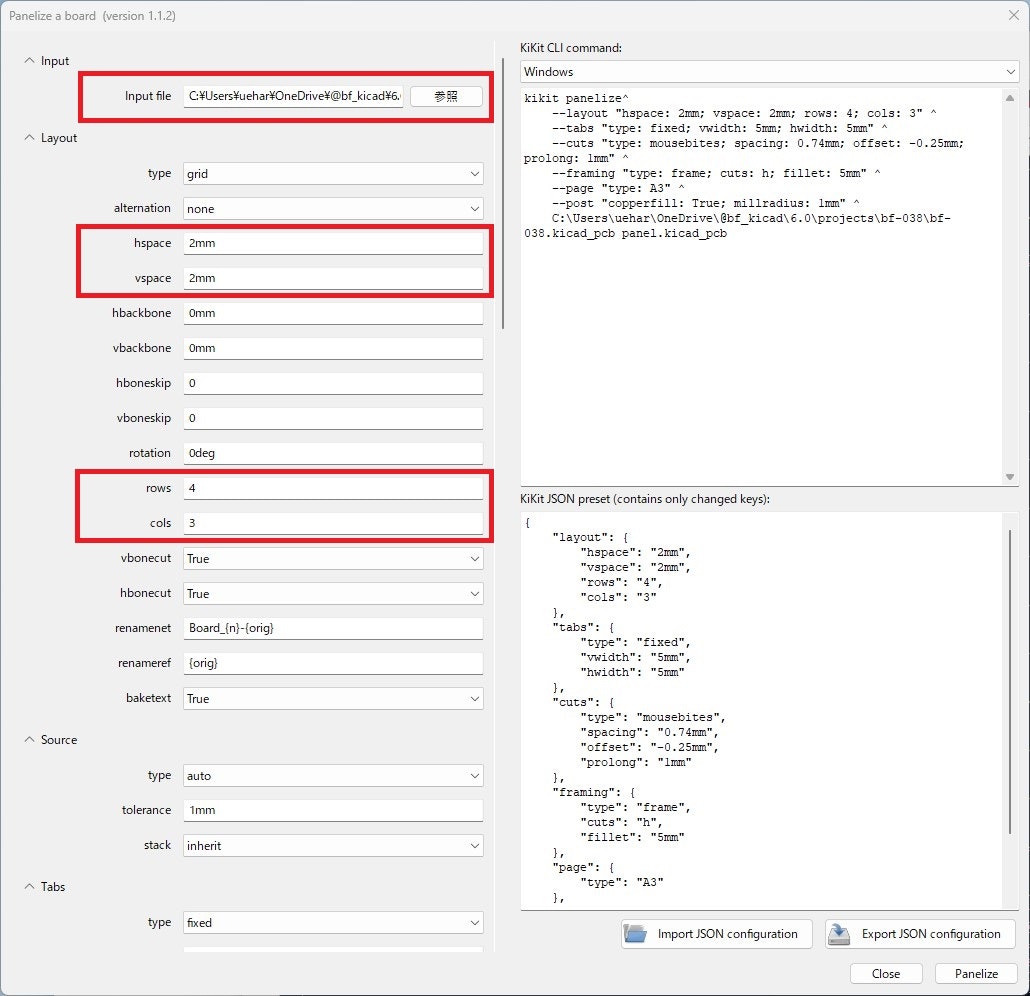

現れたPanelizeの設定メニューに入力していきます。

Input

面付けの元となるPCBの設計データファイル名(xxx.kicad_pcb)を指定します。

Layout

面付け数とPCB間の隙間の長さをJLCPCBにおける最小値2mmに指定します。元のPCBが50x50mmなのでJLCPCBにおける最大250x250mmに対して4x4まで面付けできそうです。今回は4行3列としています。PCB間に捨て基板(背骨)を設ける場合の設定項目が多いです。背骨を設けないので指定する項目は4項目のみです。

| ID | 意味 | 指定 | 備考 |

|---|---|---|---|

| type | 面付け形状 | grid | 格子状(default) |

| alternation | 隣接するPCBの向き | none | 向きの変更なし(default) |

| hspace | 横方向のPCB間隙 | 2mm | JLCPCBにおける最小値(2mm)以上 |

| vspace | 縦方向のPCB間隙 | 2mm | JLCPCBにおける最小値(2mm)以上 |

| hbackbone | 横方向の背骨の幅 | 0mm | 背骨なし(default) |

| vbackbone | 縦方向の背骨の幅 | 0mm | 背骨なし(default) |

| hboneskip | 横方向の背骨の間隔 | 0 | 背骨なし(default) |

| vboneskip | 縦方向の背骨の間隔 | 0 | 背骨なし(default) |

| rotation | PCBの回転 | 0deg | 回転なし(default) |

| rows | v方向の面付け数 | 4 | JLCPCBにおける基板最大値(250mm)に収まる枚数 |

| cols | h方向の面付け数 | 3 | JLCPCBにおける基板最大値(250mm)に収まる枚数 |

| vbonecut | 縦方向の背骨の切り込み | True | 背骨なし(default) |

| hbonecut | 横方向の背骨の切り込み | True | 背骨なし(default) |

| renamenet | netの付け替え | Board_{n}-{orig} | 付け替えあり(default) |

| renameref | referenceの付け替え | {orig} | 付け替えなし(default) |

| baketext | text変数への代入 | True | (default) |

Source

元PCBを取り込む際の設定です。デフォルトのままです。

| ID | 意味 | 指定 | 備考 |

|---|---|---|---|

| type | 面付け元PCBの外形 | auto | 自動検出(default) |

| tolerance | 面付け元PCBの外形への周囲追加 | 1mm | (default) |

| stack | PCBの導体層数 | inerit | 面付け元PCBを継承(default) |

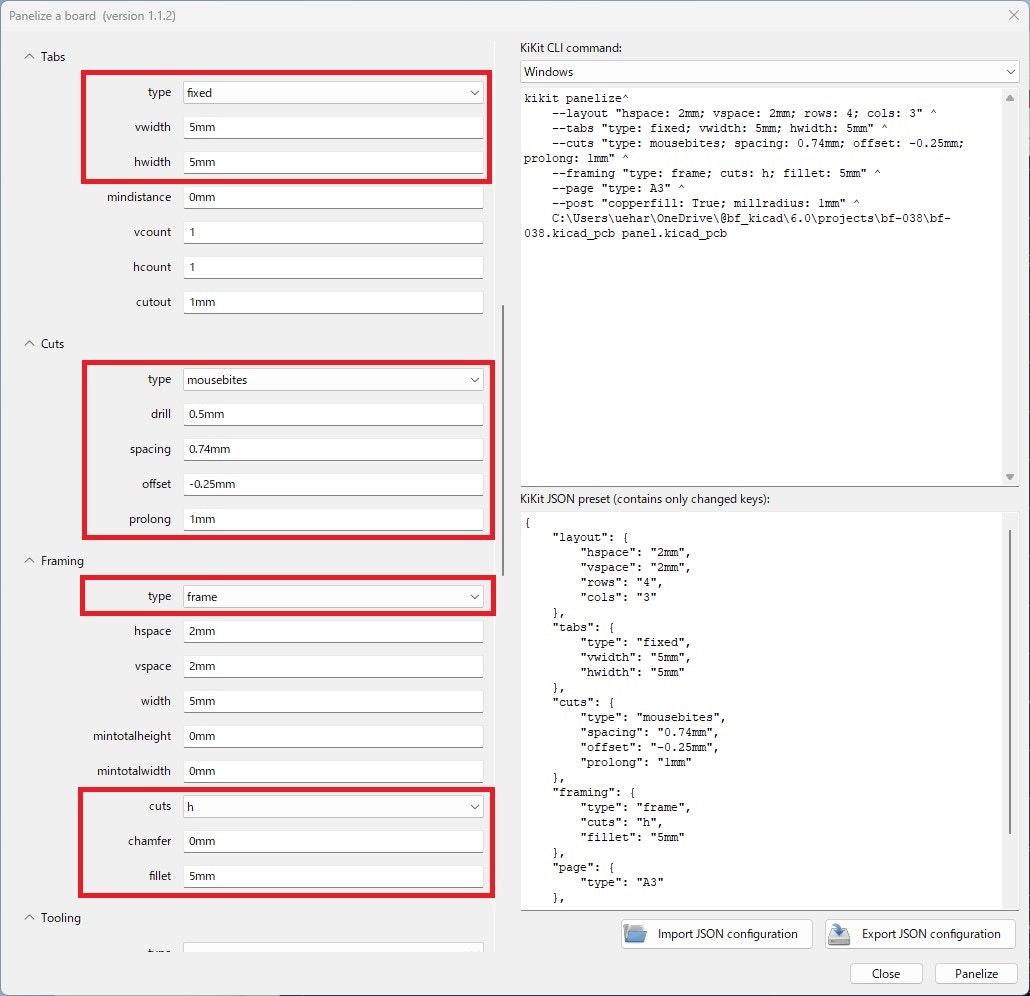

Tabs

PCB間やframe(edge rails)との間をつなぐtabの形状としては、単純なFixedを使っています。tabの長さはJLCPCBにおけるMouse bites使用時の最小値5mmとします。PCBあたりのtabの数もデフォルトの1個としています。

| ID | 意味 | 指定 | 備考 |

|---|---|---|---|

| type | tabの形状 | fixed | 固定tab |

| vwidth | 縦方向のtabの長さ | 5mm | JLCPCBにおける最小値(5mm)以上 |

| hwidth | 横方向のtabの長さ | 5mm | JLCPCBにおける最小値(5mm)以上 |

| mindistance | tabの最小間隔 | 0mm | (default) |

| vcount | 縦方向のtabの元PCBあたりの数 | 1 | (default) |

| hcount | 縦方向のtabの元PCBあたりの数 | 1 | (default) |

| cutout | PCB外形の切り欠きに対応するtab側の切り欠き | 1mm | (default) |

Cuts

切り離し方法としてMouse bitesを指定します。JLCPCBの推奨範囲に従いドリル0.5mmとし、間隔は0.2-0.3mmになるように試行した結果、spacingを0.74mmとしました。Mouse bitesをPCBの外側に出すことにし、offsetをドリル径の半分外側の-0.25mmとします。tabの形状を加工しやすい形状とするため、prolongを1mmとします。PCBの間隙が2mmなのでtabの外形は半円弧になります。

| ID | 意味 | 指定 | 備考 |

|---|---|---|---|

| type | 切り離し方法 | mousebites | Mouse bites |

| drill | ドリル径 | 0.5mm | JLCPCBの指定範囲0.5-0.8mm(default) |

| spacing | ドリル間隔 | 0.74mm | JLCPCBの指定範囲0.2-0.3mmに収まる値を試行 |

| offset | 穴あけ位置 | -0.25mm | PCB内側がプラス、外側がマイナス |

| prolong | tabからPCB外形への接続距離 | 1mm | PCB間隙の半分 |

Framing

frame(edge rails)を設定します。強度確保のため4辺にframeを設けることとします。PCBとの間隙はPCB間と同じJLCPCBの最小値2mmとします。frameの幅は、JLCPCBの最小値3mmに対し、JLCPCBが付加する場合の5mmとします。面付け基板の大きさの最小値はクリアしています。4辺を囲むためframeにもMouse bitesが必要です。縦横いずれか一方でよいと思われます。frame外形の面取りまたはフィレット(丸み付け)は、チップマウンタやリフロー装置のレール上で引っかかることなくスムーズに流れるために推奨されています。frameの幅を考慮してフィレット5mmを指定します。

| ID | 意味 | 指定 | 備考 |

|---|---|---|---|

| type | frameの形状 | frame | 4辺 |

| hspace | 横方向のframeとの間隙 | 2mm | JLCPCBにおける最小値(2mm)以上(default) |

| vspace | 縦方向のframeとの間隙 | 2mm | JLCPCBにおける最小値(2mm)以上(default) |

| width | frameの幅 | 5mm | JLCPCBにおける最小値(3mm)以上(default) |

| mintotalhight | 面付け基板の高さの最小値 | 0mm | 指定なし(default) |

| mintotalwidth | 面付け基板の幅の最小値 | 0mm | 指定なし(default) |

| cuts | frameのMouse bites | h | 横方向に作成 |

| chamfer | frame外側の面取り | 0mm | 指定なし(default) |

| fillet | frame外形のフィレット | 5mm | frameの幅以下 |

Tooling, fiducials

位置決め用の穴、基準マーク(fiducial)は製造上の仕様に合わせる必要があります。JLCPCBに追加を任せることにします。

Text, Text2, Text3, Text4

frameにシルクの文字列を追加できます。特に使用していません。JLCPCBが整理記号を追加します。

Copperfill

PCB外の領域を銅箔で覆う処理は、使用していません。frameやtabについては後のPostで処理できます。

Page

面取り基板生成後の、図面への反映方法を設定します。図面サイズtypeをA3とします。それ以外はデフォルトのままです。

Post

最終処理の指定です。copperfillをTrueにします。frame(edge rails)やtabに銅箔を満たします。frameの強度を改善するとともにエッチング液の劣化を減らします。millradiusを1mmとします。ルーター加工のミル径が考慮されframeの内側にアールが形成されます。

Debug

(4)面付けの実行

以上の設定でPanelizeボタンをクリックすると面付け済基板が生成されます。この状態で、DRCも実行することができます。ただし、回路図との整合性はチェックできません。面付け前のPCBの段階でDRCを確認しておく必要があります。

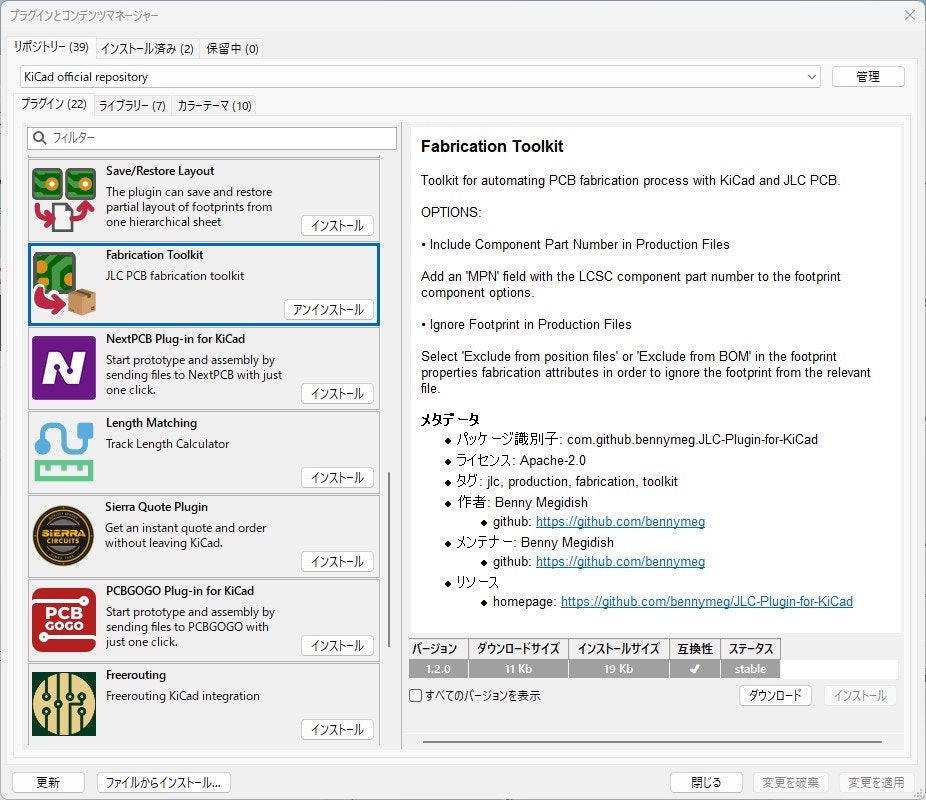

6. JLCPCBへのオーダーの例

kikitにも製造データの出力機能がありますが、JLCPCBに関しては、JLCPCB Fabrication ToolKitを使うのが便利です。回路図がなくてもPCBAに必要なファイルを生成できます。製造データはproductionフォルダに出力されます。

gerber.zip

JLCPCBのPCBオーダーのページでadd gerber fileとしてこのままアップロードできます。bom.csv, position.csvなども含まれますが問題なく無視される様です。

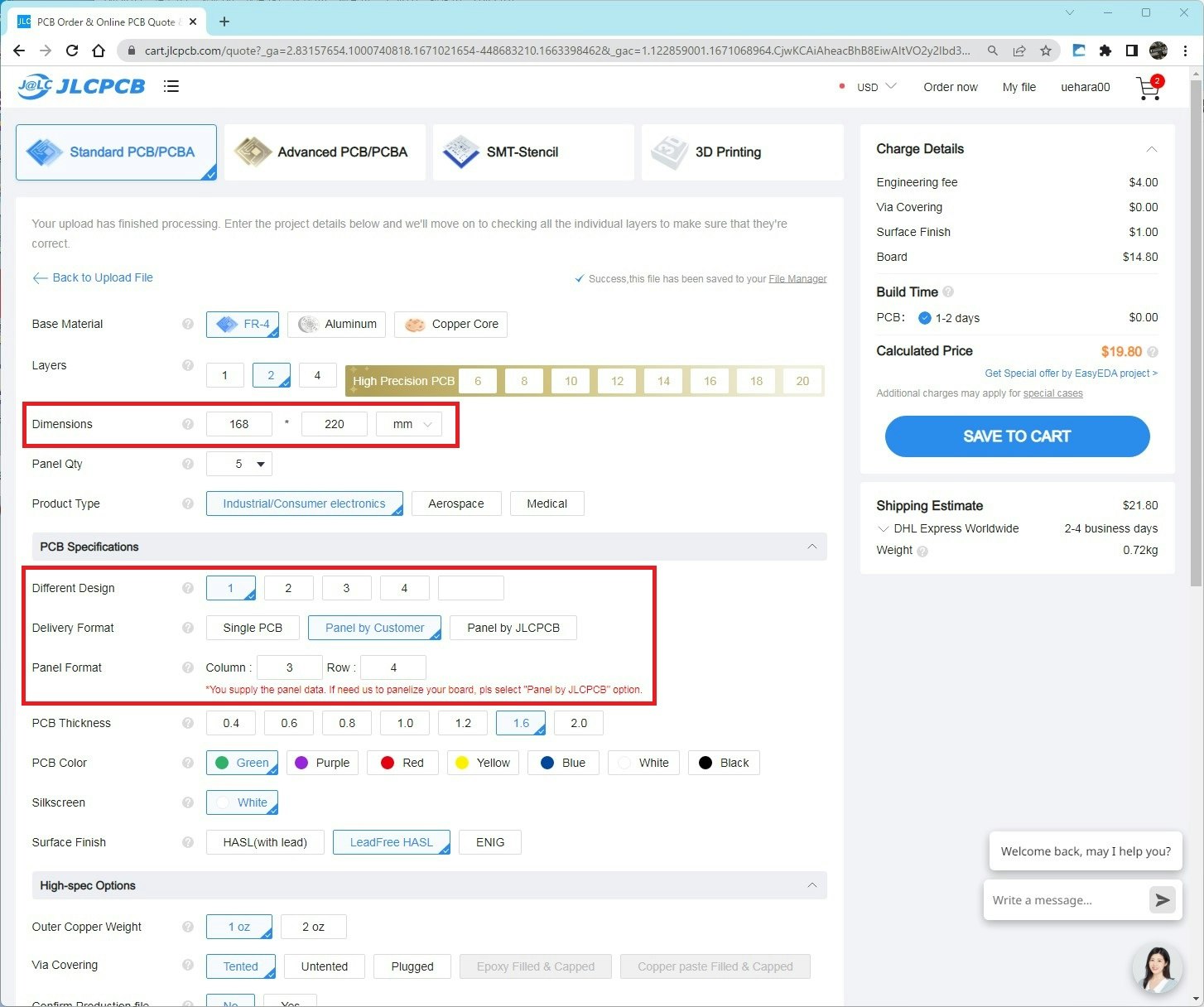

データ量が大きくなると基板イメージが表示されない場合があります。この場合、Dimensionsに面付け後の基板の外形を正確に入力します。枚数も面付け後の基板単位です。面付けの情報(Different Design, Deliverly Format, Panel Format)も入力します。その他の項目も必要に応じて修正します。

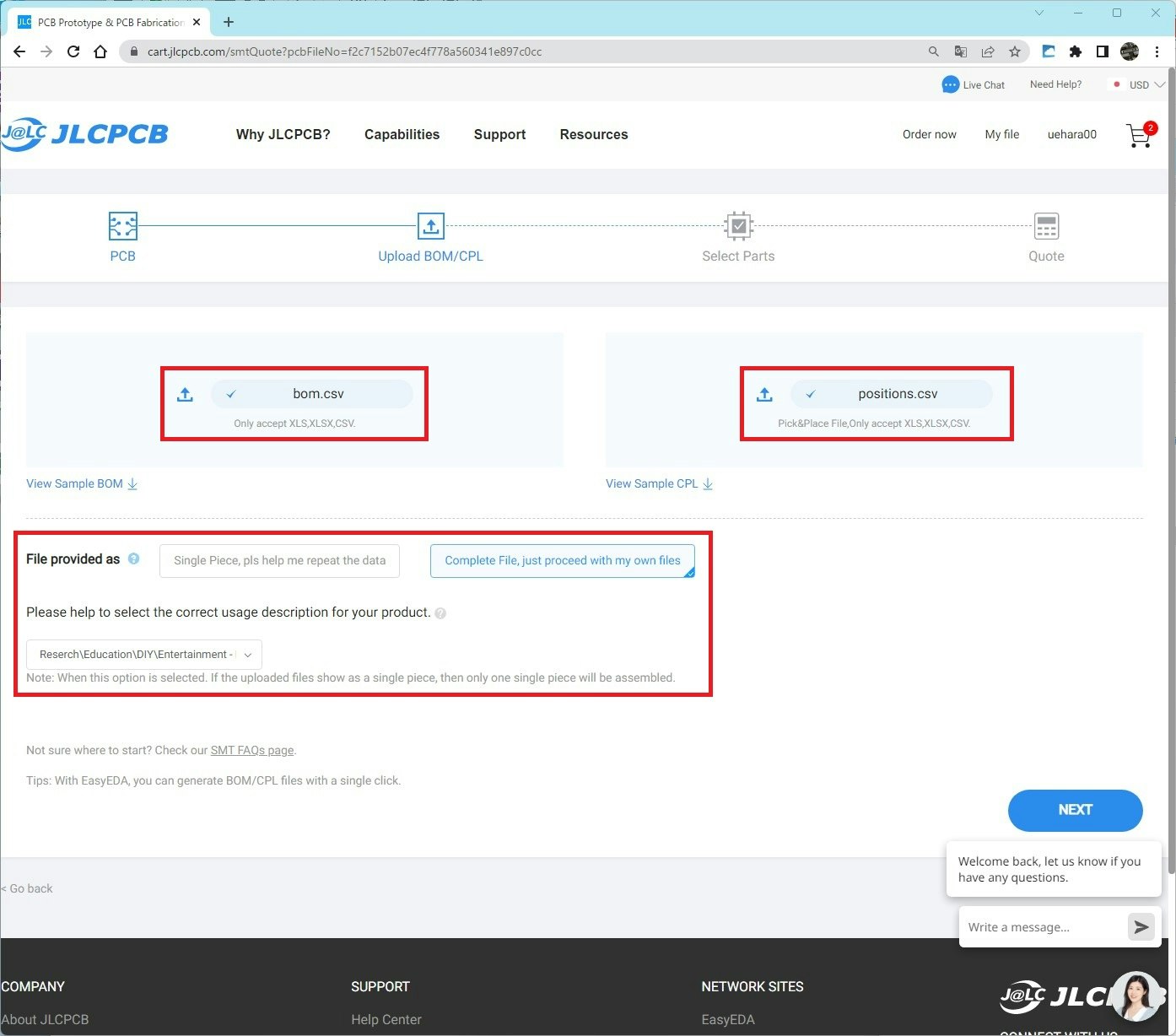

bom.csv, positions.csv

JLCPCBのPCBAオーダーのページで部品表(BOM)やPick&Placeファイルをアップロードします。bom.csv、positions.csvは面付け済基板全体の情報を含むComplete Fileです。

- BOM(Bill of Materials)

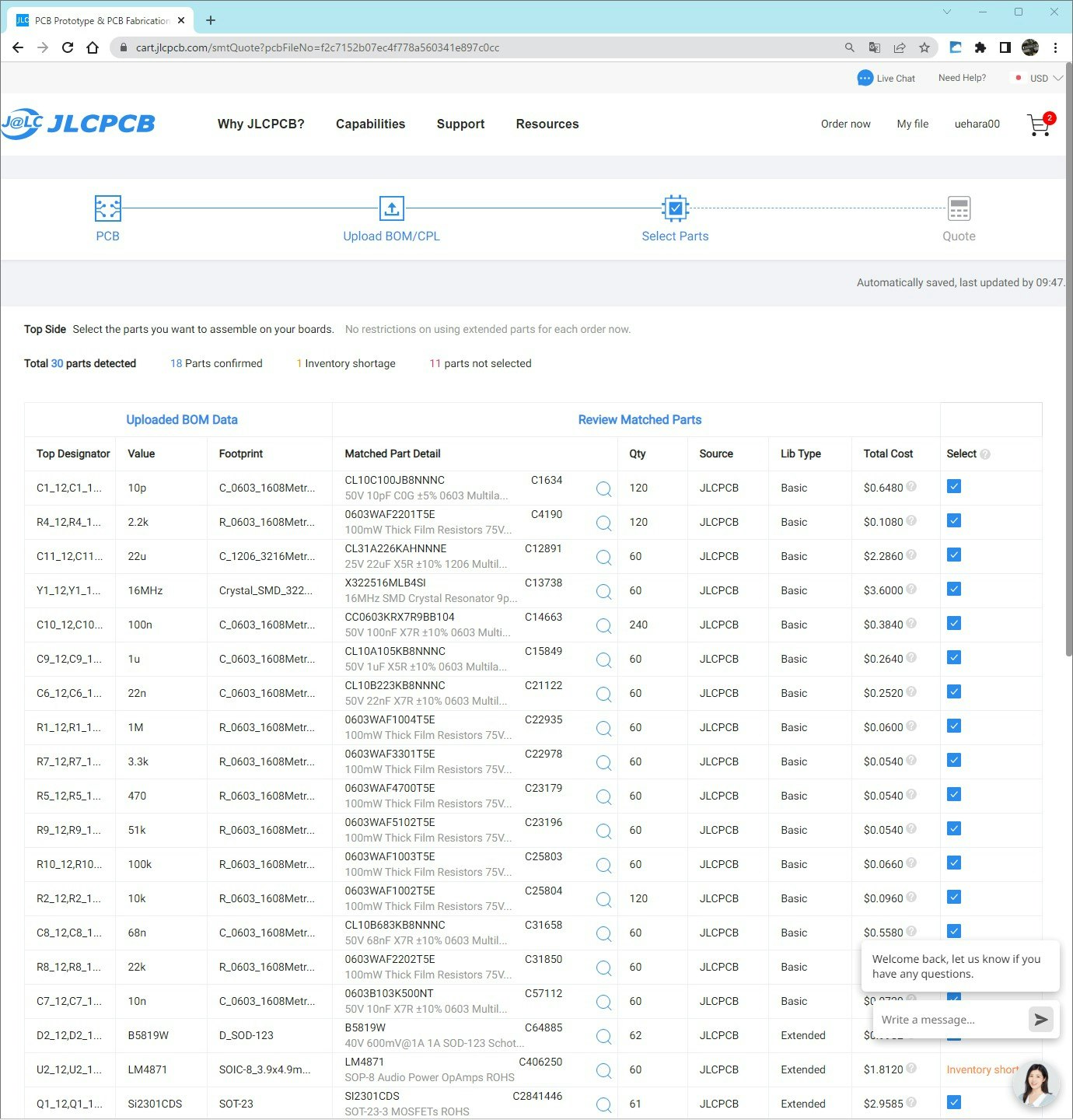

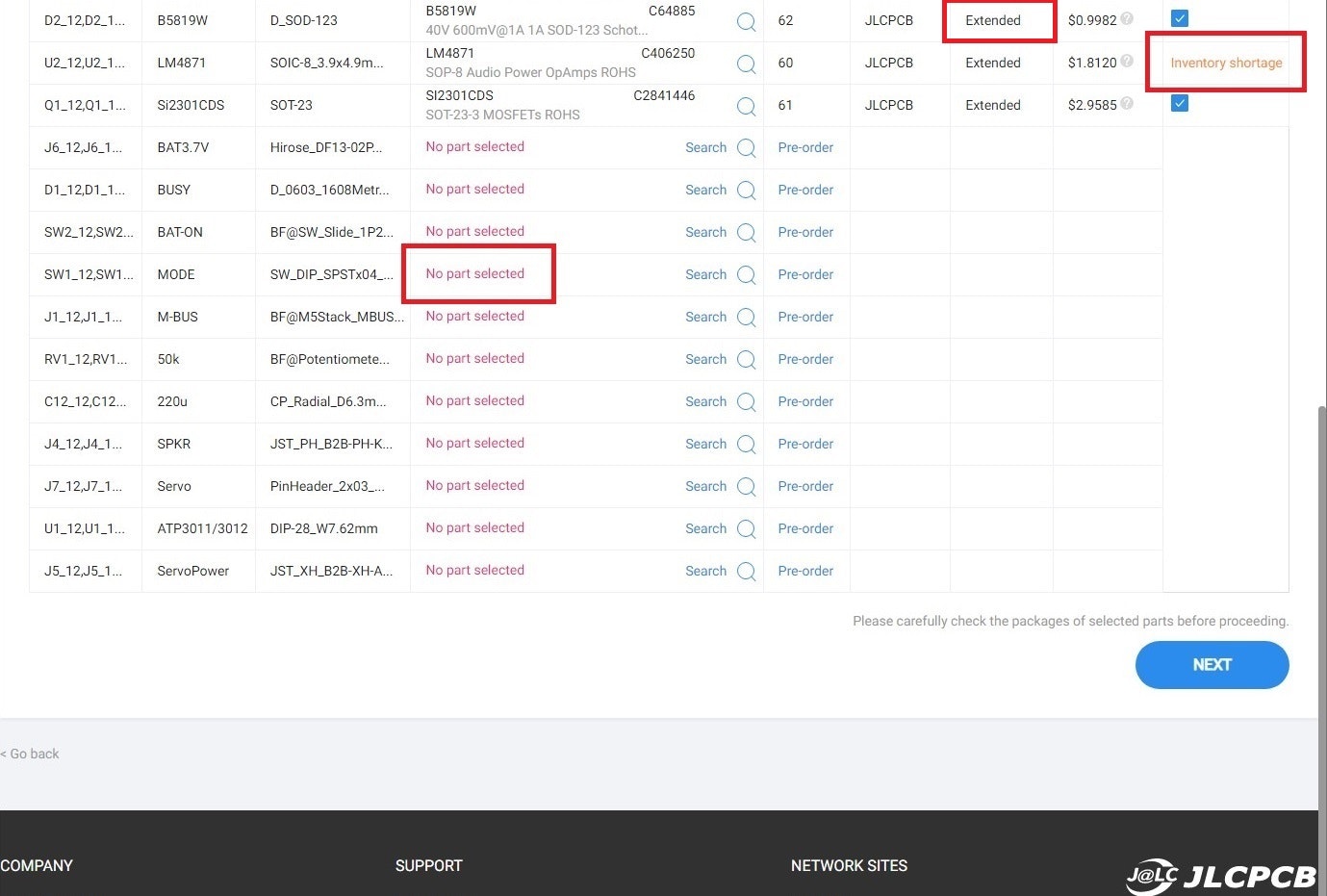

部品選択の確認・修正

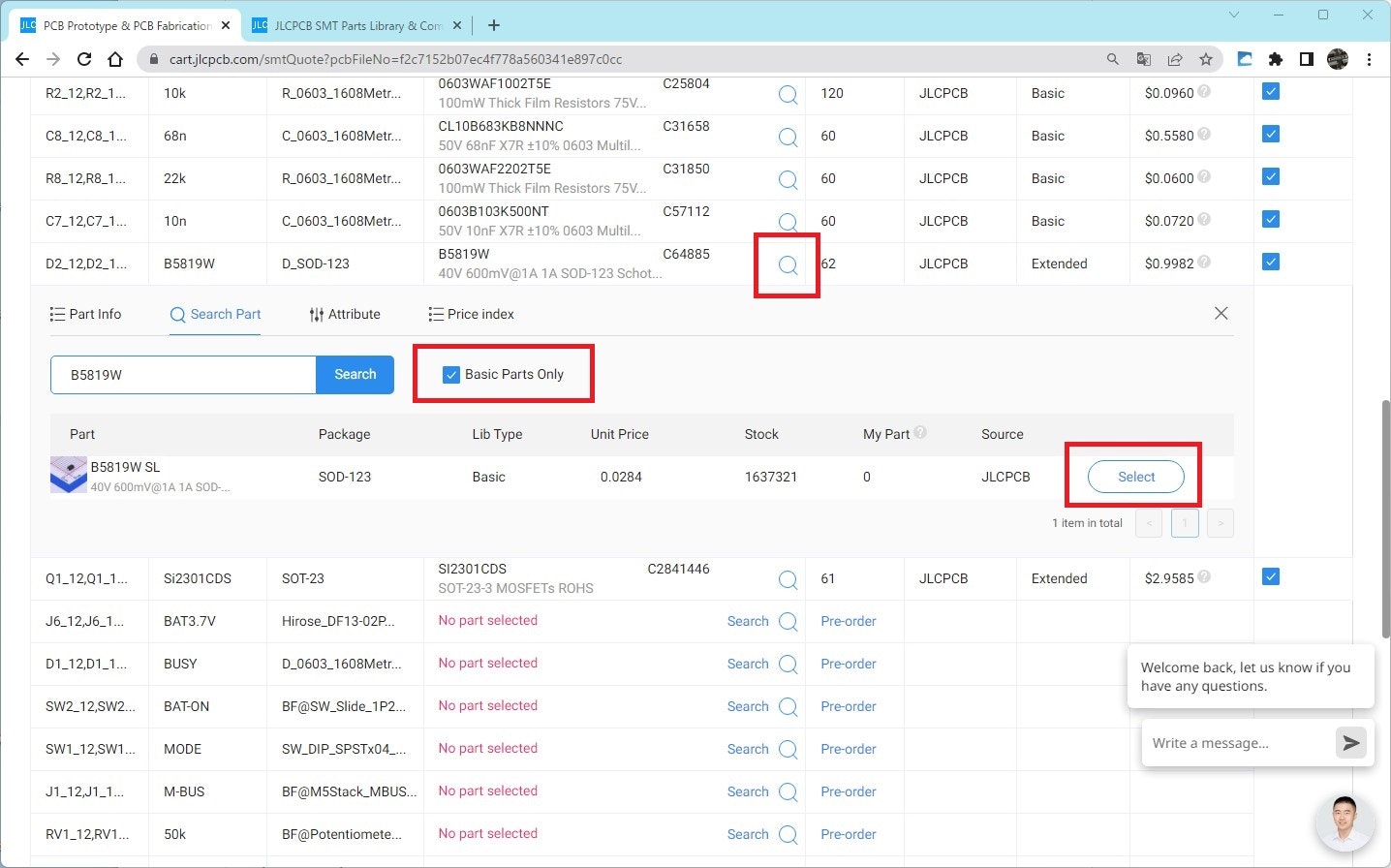

Select Partsページで選択された部品を確認します。bom.csvのLCSC Part#(JLCPCB Part#)欄に指定がない場合は自動で選択されます。

部品が自動選択不能、在庫不足、あるいは部品を変更したい場合、このページで修正できます。以下の例は選択された部品B5819W(C64885)を、Basic PartsであるB5819W SL(C8598)に選択しなおす様子です。Basic Partsは手数料が発生せず、一般に在庫が潤沢で安価です。

PCBAを繰り返す場合、部品の確認作業と修正作業が毎回発生するのは煩雑ですので、bom.csvにおいてLCSC Part#欄で部品を指定します。

部品配置の確認・修正

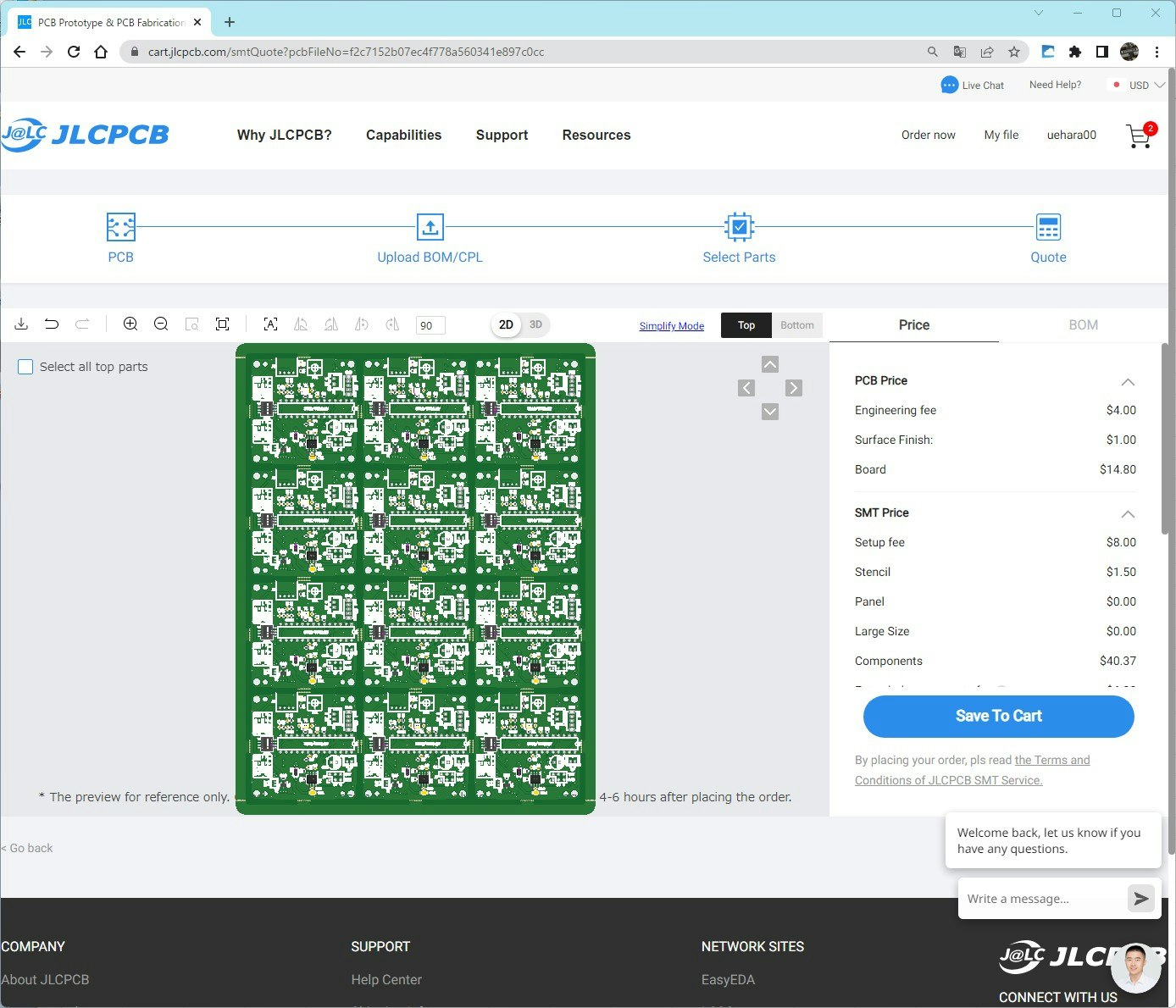

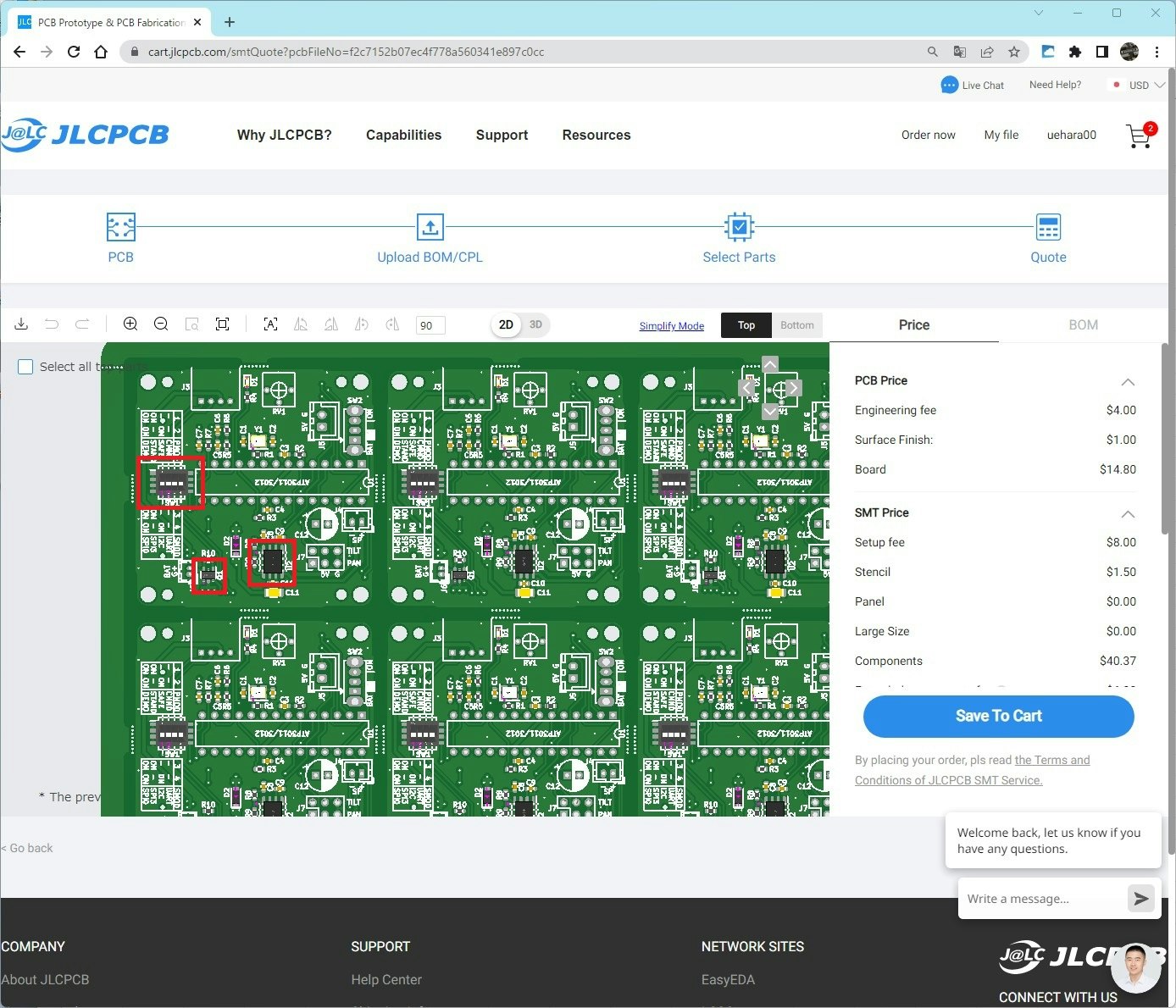

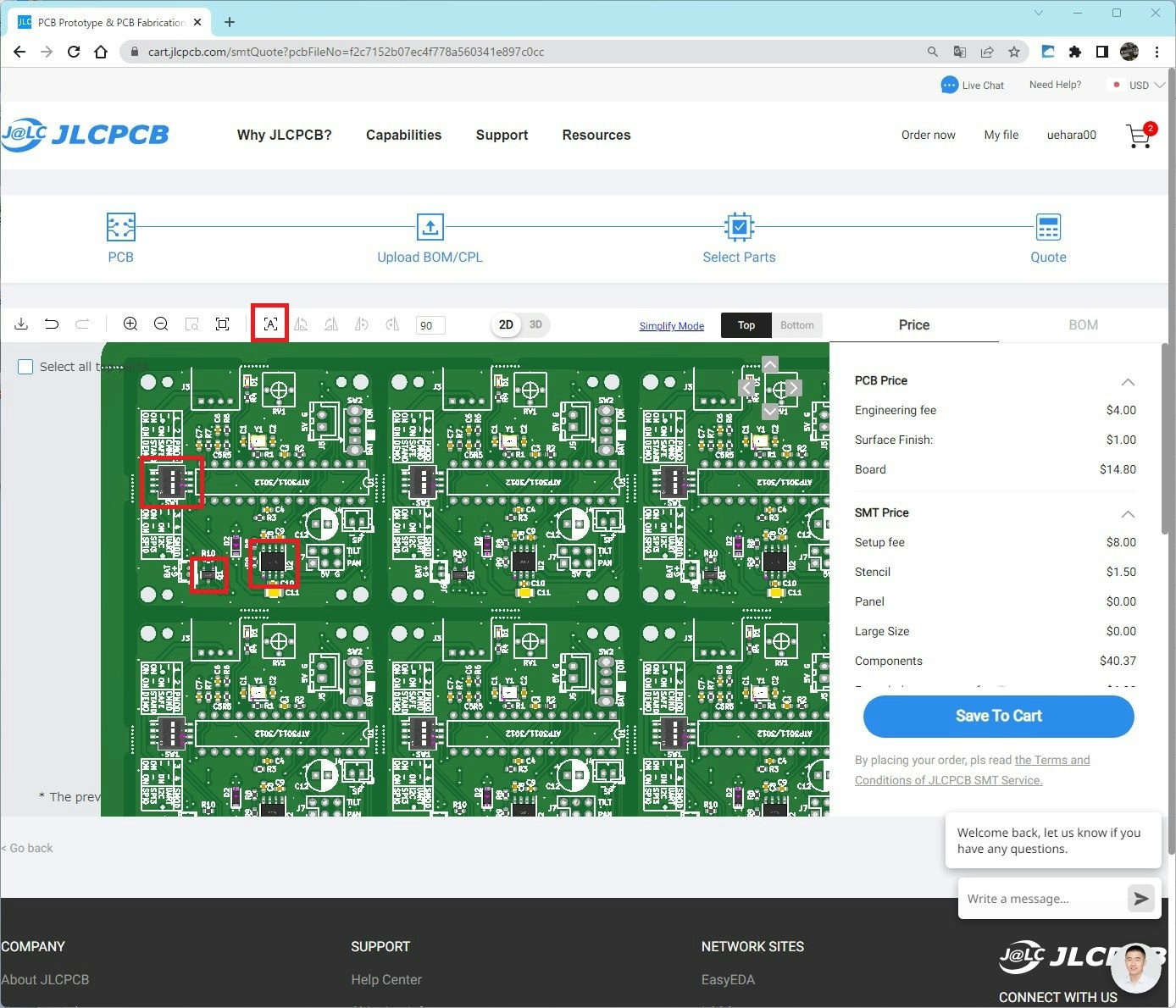

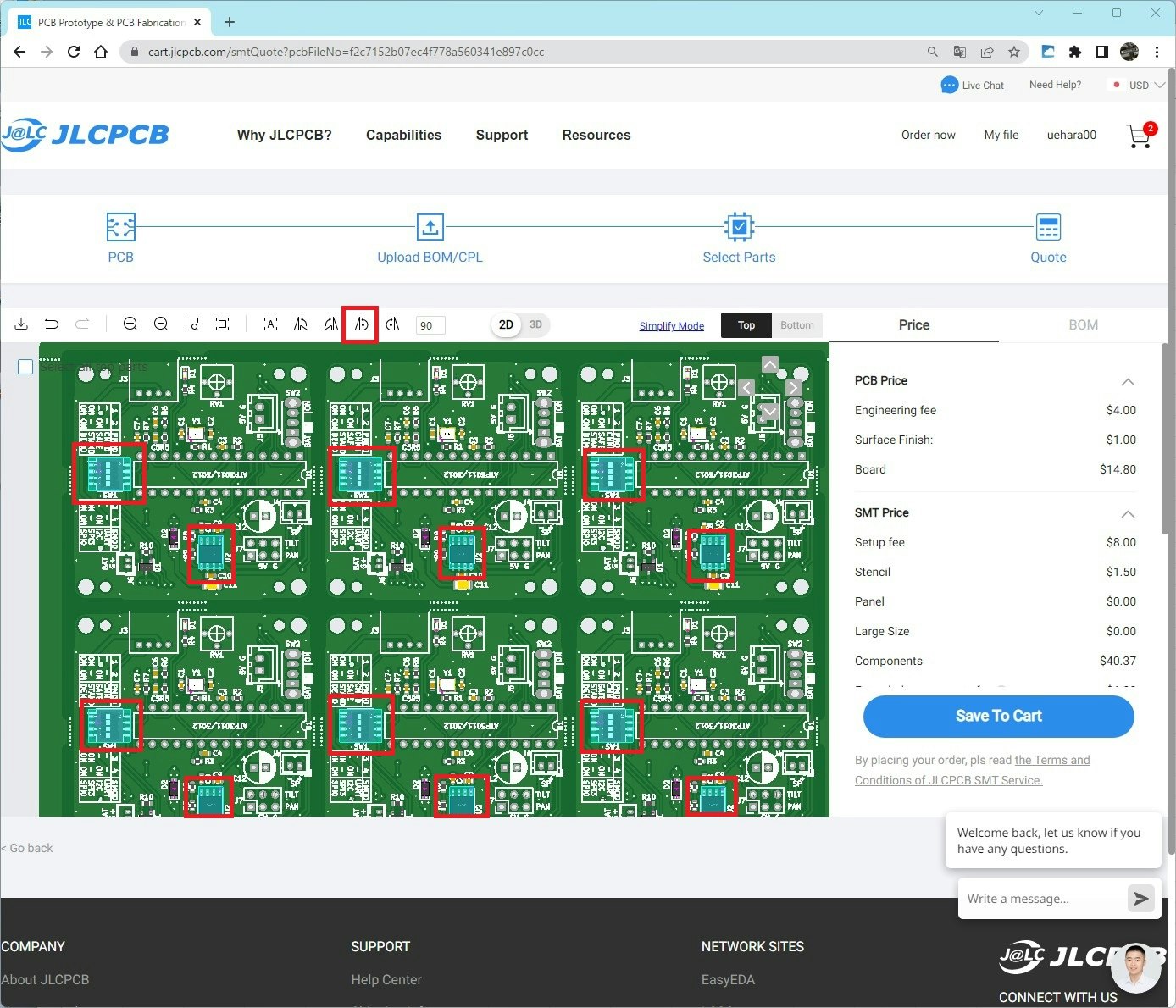

bom.csv、positions.csvの情報が基板の完成イメージでQuoteページに表示されます。

3ピンおよび8ピンの部品の向きが基板のパッドと合っていません。

Alignボタン[A]をクリックすると、パッドにピンを載せる様に部品を回転します。3ピンの部品はきれいにパッドに載りました。

しかし、8ピンの部品はピン1の位置があっておらず180°回転させる必要があります。部品を複数選択するにはCTRLキーを押しながらクリックします。部品をその場で回転させるためRotate Left/Rightボタンを押します。ちなみにAll Rotate Left/Rightボタンは、選択した部品をグループ化して回転します。

PCBAを繰り返す場合、修正作業が毎回発生するのは煩雑ですので、**positions.csvにおいてRotation欄の値を修正しておきます。

7. まとめ

KiCadもプラグインもJLCPCBも日々改善され、便利な機能が新たに提供されています。現状、手作業が必要な個所も近い将来は自動化されることでしょう。これからも新たな機能を有効活用していきたいと思います。