1. はじめに

トランジスタ技術(トラ技)2020 年 5 月号1の特集記事に感化されました。この記事を真似て製作したいと考えました。以前から単体トランジスタ23、基本ゲート IC45、またはリレー6を使ってコンピュータを製作し動作させている方々がいます。ネットや MakerFaire Tokyo で見るたびに、いつか作ってみたいと思っていました。Web を参照すると、それぞれに特徴のある記録があり大変参考になります。Youtube にある動作の様子などは大変興味深いです。

2. 考え方

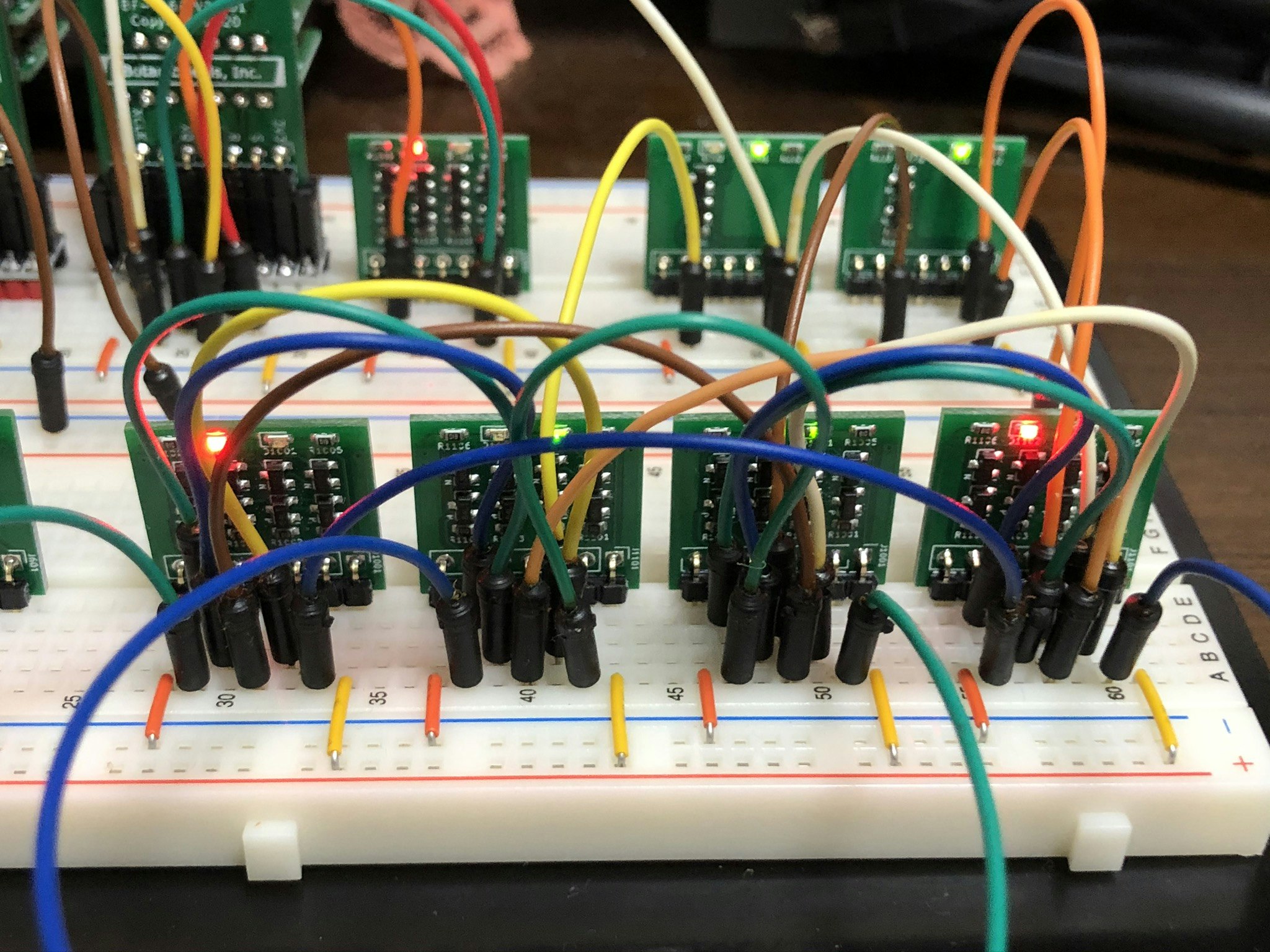

MOS-FET で論理ゲートを実現します。機能の異なる小さなプリント基板(論理ゲート基板)を用意します。これらを組み合わせてコンピュータを作成します。動作を LED で表示する「光りモノ」にします。動作スピードは特に追求しないことにします。

2.1 AND-OR インバータを活用する

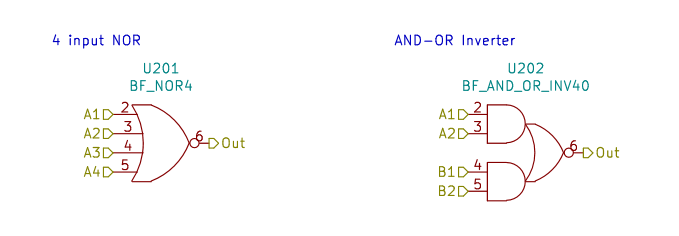

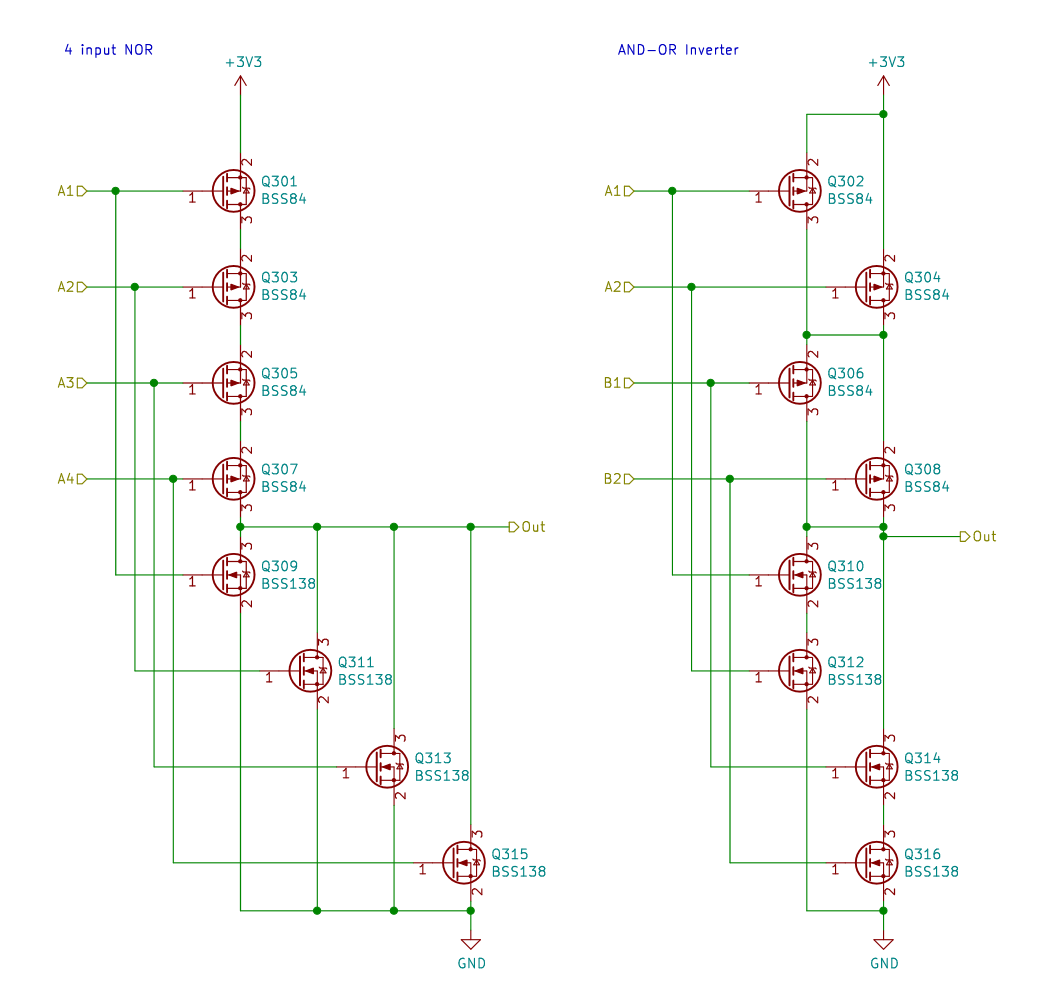

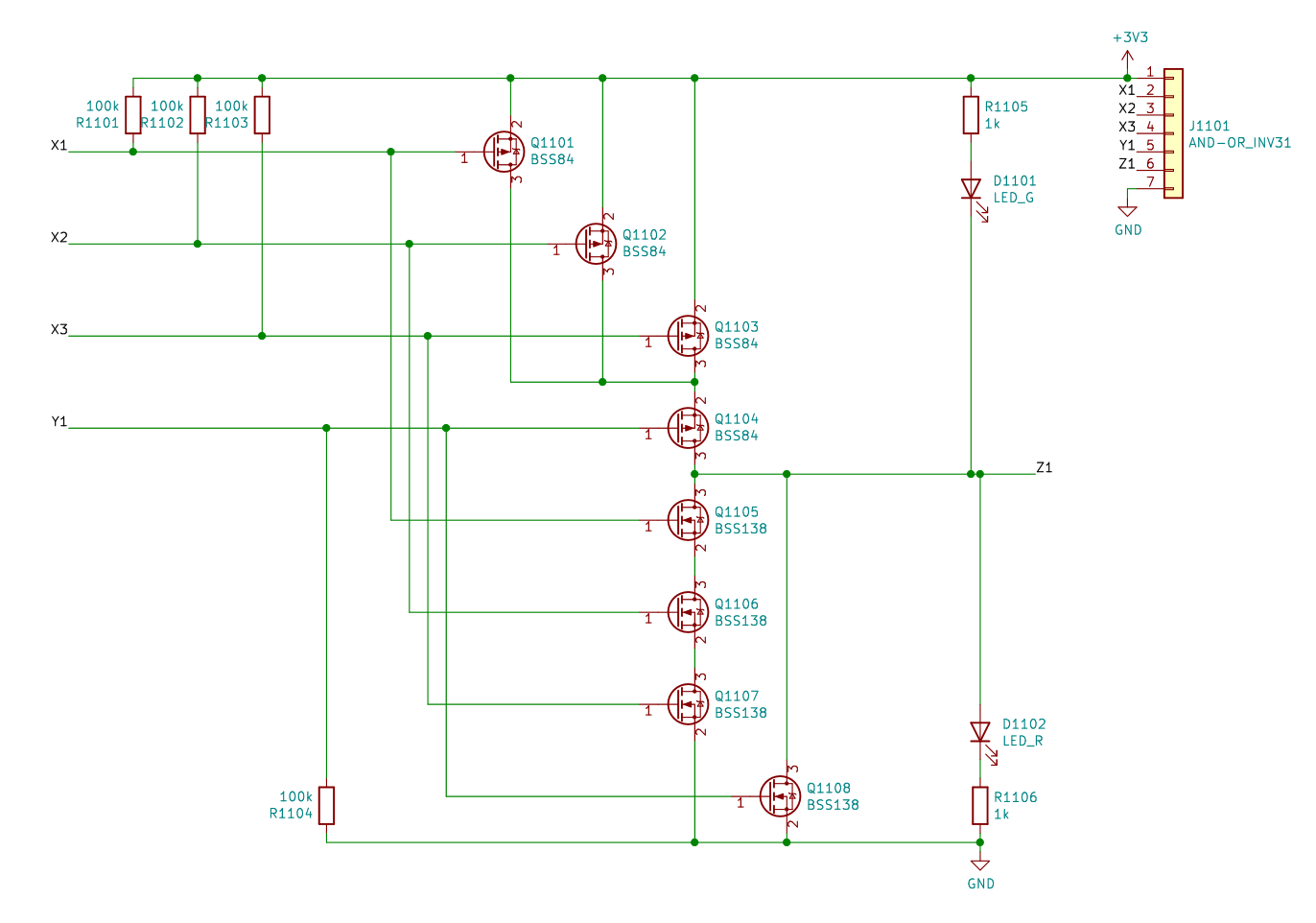

4 入力の NAND や NOR と同じ MOS-FET 数で 4 入力の AND-OR インバータを実現することができます。マルチプレクサなどに多用したいと思います。

4 入力 NOR と AND-OR インバータの回路シンボル

MOS-FET による実現

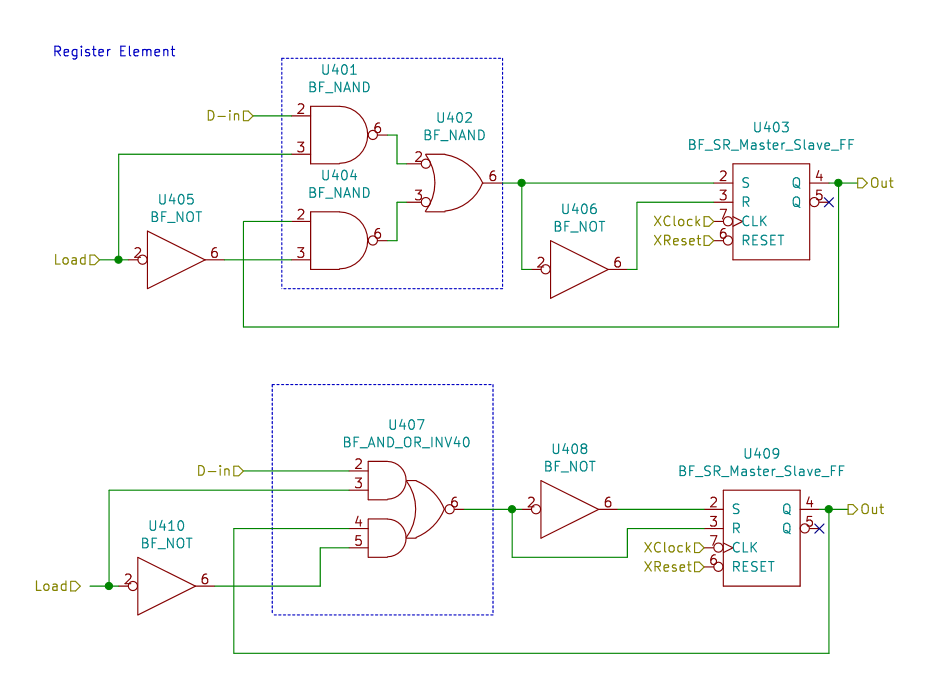

AND-OR インバータ使用前/使用後(レジスタ)

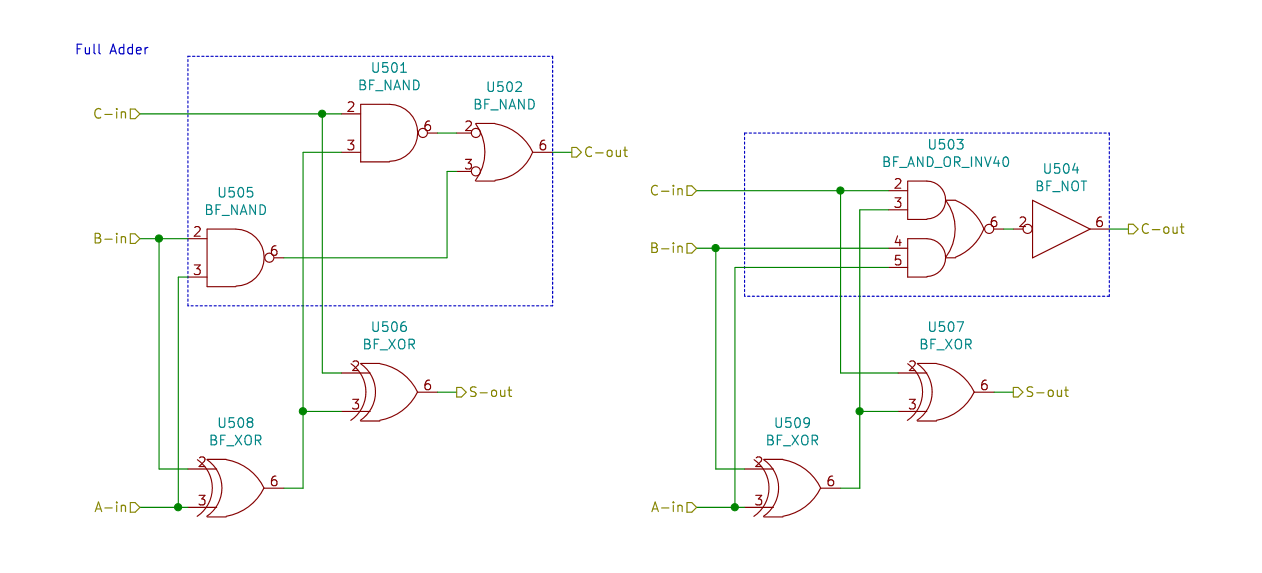

AND-OR インバータ使用前/使用後(全加算器)

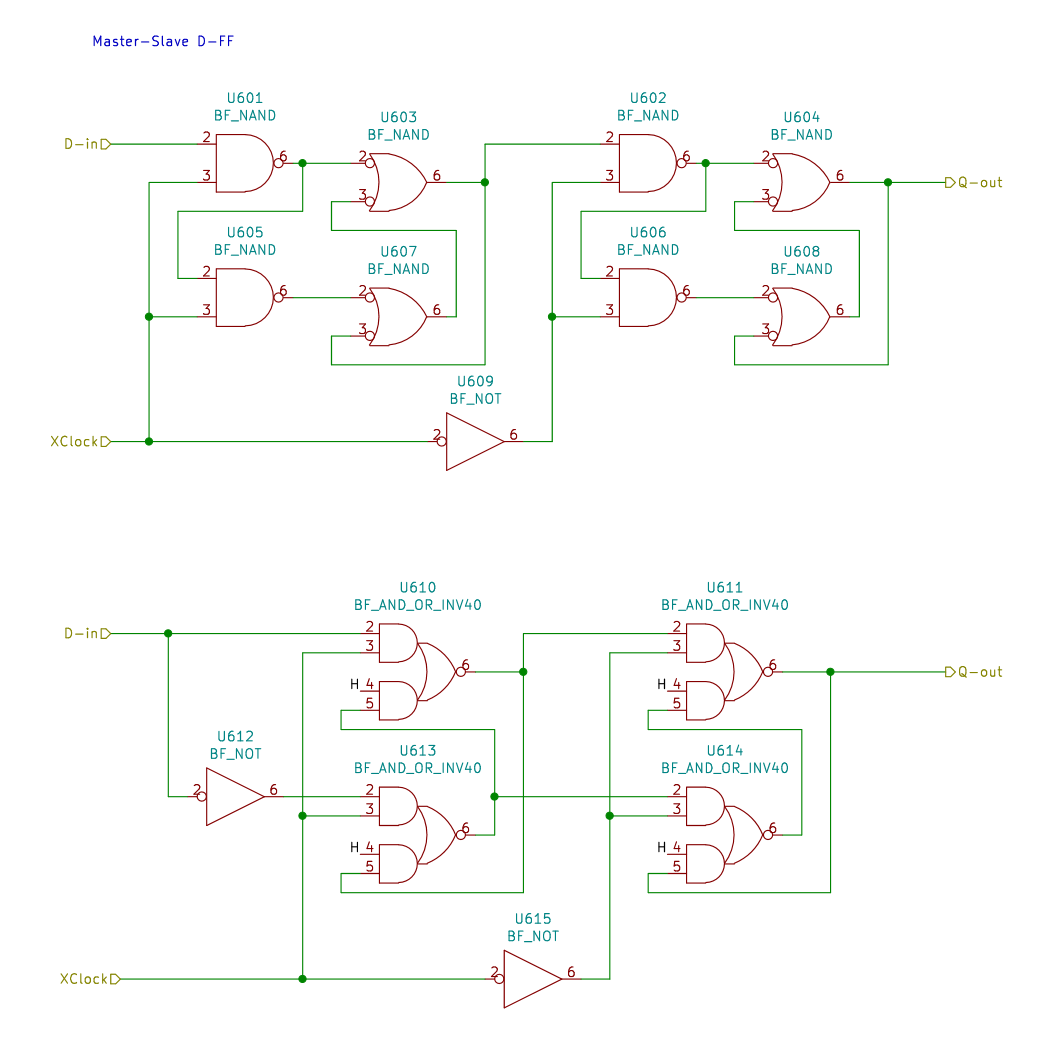

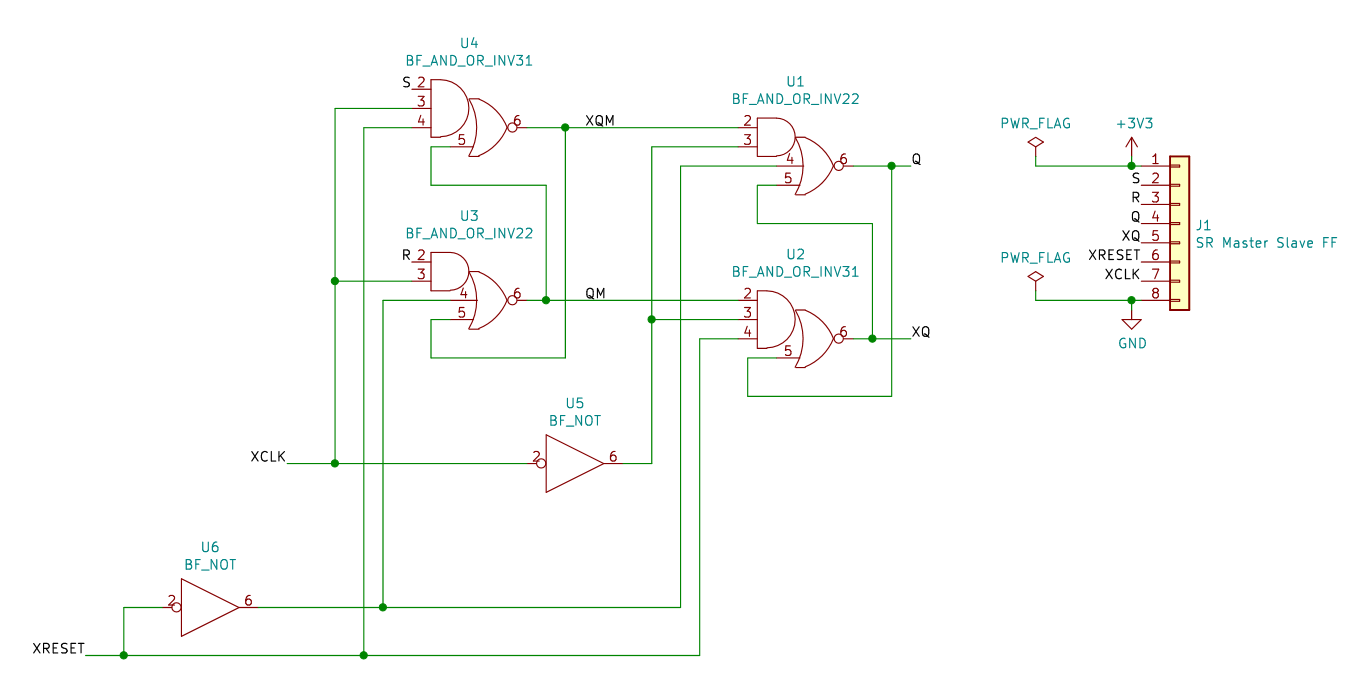

AND-OR インバータ使用前/使用後(フリップフロップ)

マスタースレーブ型 D フリップフロップ(FF)を NAND で構成すると 9 ゲート必要です。AND-OR インバータでは実質的に 6 ゲートで実現できます。6 ゲート構成のエッジトリガ型 D-FF も知られています。今回の工作ではマスタースレーブ型の動きを見てみたいと思います。

2.2 階層化する

以下の様に階層化して設計します。

| プリント基板の階層 | 構成部品 | 機能 |

|---|---|---|

| 論理ゲート基板 | MOS-FET | NOT, AND, OR, NAND, NOR, XOR, AND-OR インバータなど |

| 論理モジュール基板 | 論理ゲート基板 | 全加算器、フリップフロップ、ROM |

| 論理ユニット基板 | 論理モジュール基板、論理ゲート基板 | 4 bit 加算器、4 bit レジスタ |

| メイン基板 | 論理ユニット基板、論理モジュール基板、論理ゲート基板 | 装置全体 |

2.2.1 シンボルをライブラリに登録する

論理ゲート基板、論理モジュール基板、論理ユニット基板のシンボルを作成し部品ライブラリに登録します。シンボル化した論理ゲート基板、論理モジュール基板、論理ユニット基板を上位階層から部品として使用します。部品なので複数使えます。組み立てる際には使用した数だけプリント基板が必要です。

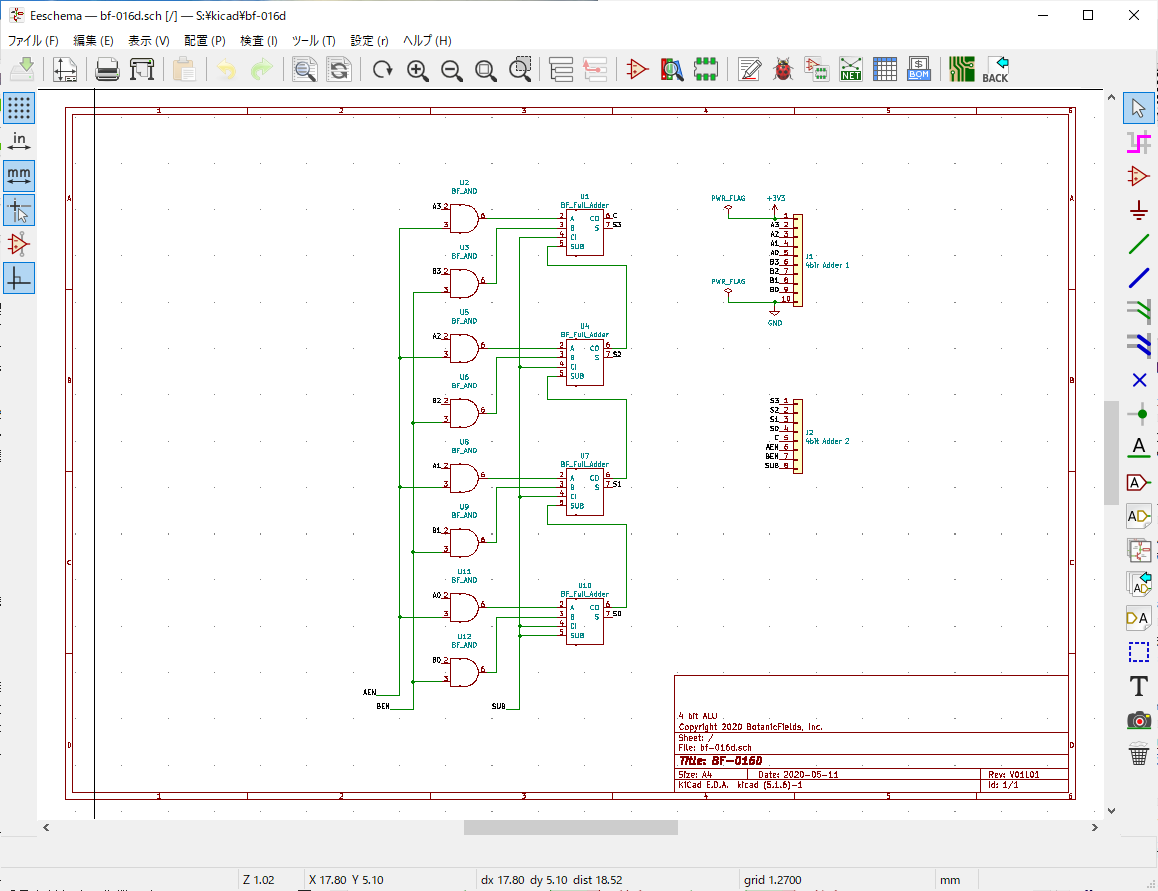

回路図エディタとシンボル作成

設計にはプリント基板 CAD の 1 つである KiCad7を使用します。回路図は、KiCad の Eeschema で作成します。以下は 4 bit 加算器の回路図です。A 入力または B 入力を強制的に 0 にする回路があります。論理ゲート(AND)と論理モジュール(全加算器)のシンボルを使用しています。

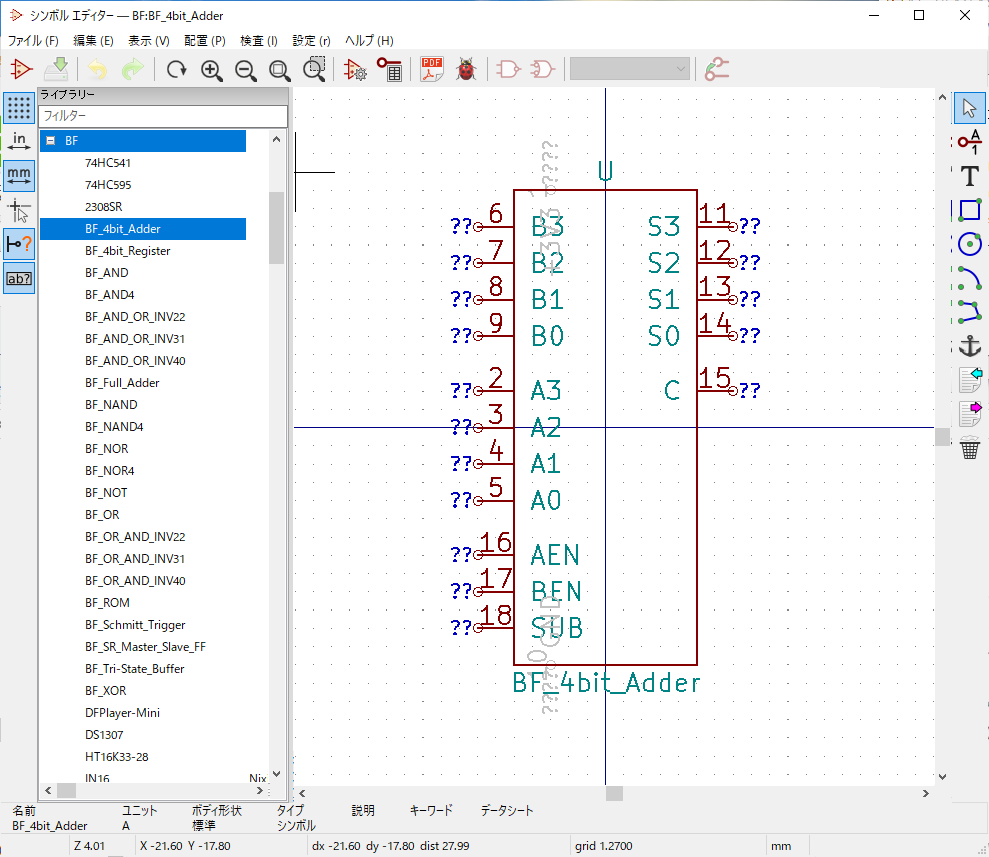

部品を表すシンボルは、KiCad の Symbol Editor で作成します。以下は 4 bit 加算器のシンボルです。

2.2.2 回路図の階層化

Eeschema の階層機能も併用します。Eeschema では同一階層で複数ページの図面を作成できません。複数ページにするためには階層化をします。階層を使用することで上位階層の回路図を単純化し、別ページの下位階層で詳細化できます。階層化した回路は、上位階層からインスタンス(実体)として複数引用することができます。論理ゲート基板、ROM モジュール基板、および装置全体(メイン基板)で階層を使用しています。複数のインスタンスも便利に使用しています。

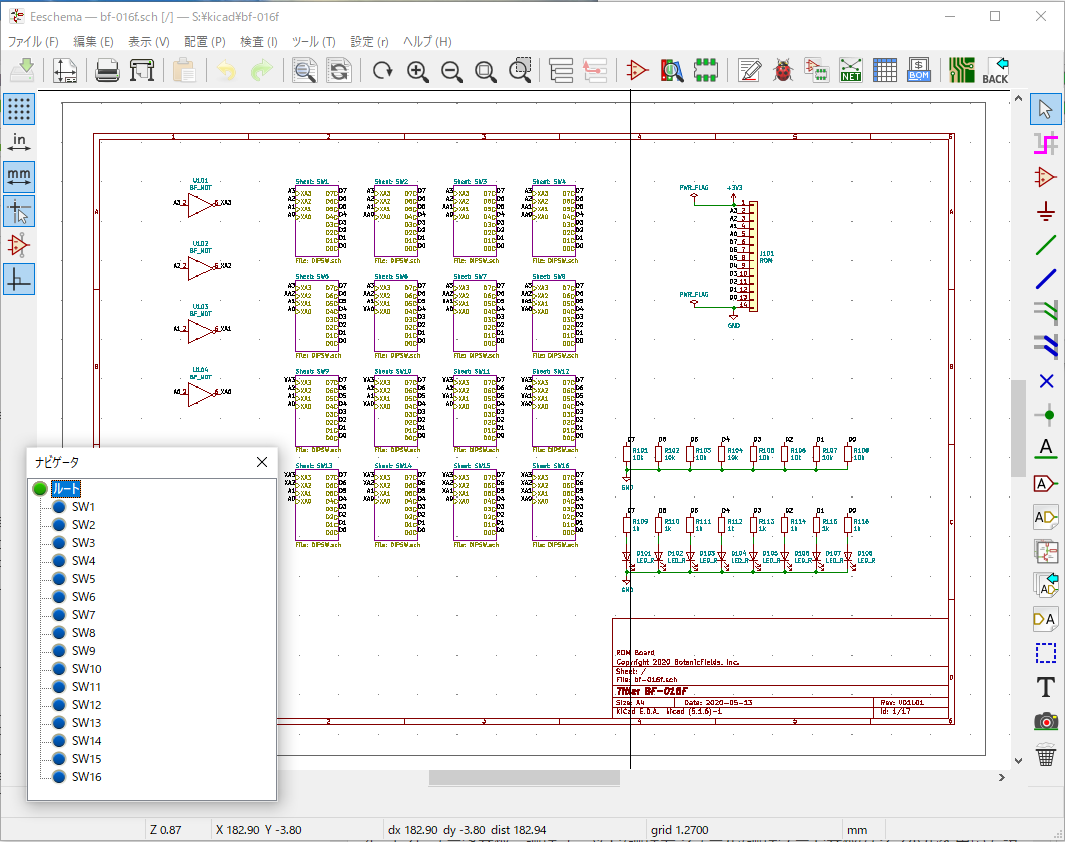

階層を使った ROM モジュールの回路図面です。階層ナビゲータを表示しています。SW1 ~ SW16 を下位階層で作成しています。

SW1 ~ SW16 は、同じ回路図面ファイルを引用しています。ユニークな部品番号を付与するために回路図面が 16 枚になりますが、1 枚を修正すると 16 枚全てに修正が反映されます。

回路図面のページ番号とアノテーション

階層化して複数ページとなった回路図面のページ番号は、階層を生成した順番になります。複数インスタンスの場合も同様です。この順番を変更するスマートな方法がありません。並べたい順番に階層を一旦カットしてペーストしていくことで、きれいに並べることができます。

アノテーションとは、回路図面上の部品にユニークな識別番号を付与する作業です。アノテーションは、回路図面上で横方向順、縦方向順などいくつかの条件を与えて自動的に行うことができます。階層の場合、ページ 1 は 100 番台、ページ 2 は 200 番台という様に割り当てることが可能です。階層ページが意図どおり並んでいれば、自動アノテーションで意図通りの部品識別番号を割り当てることができます。

3. 回路

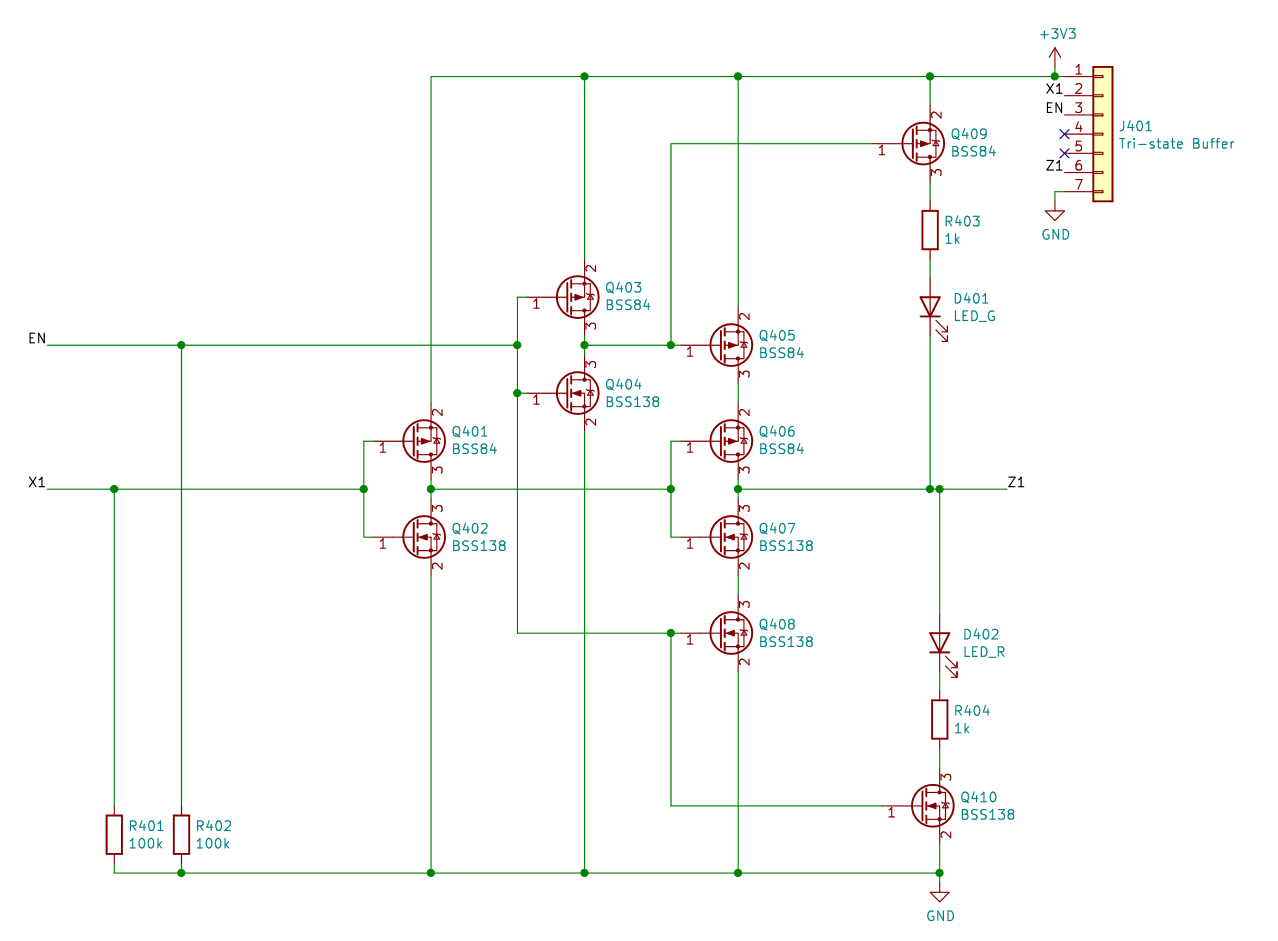

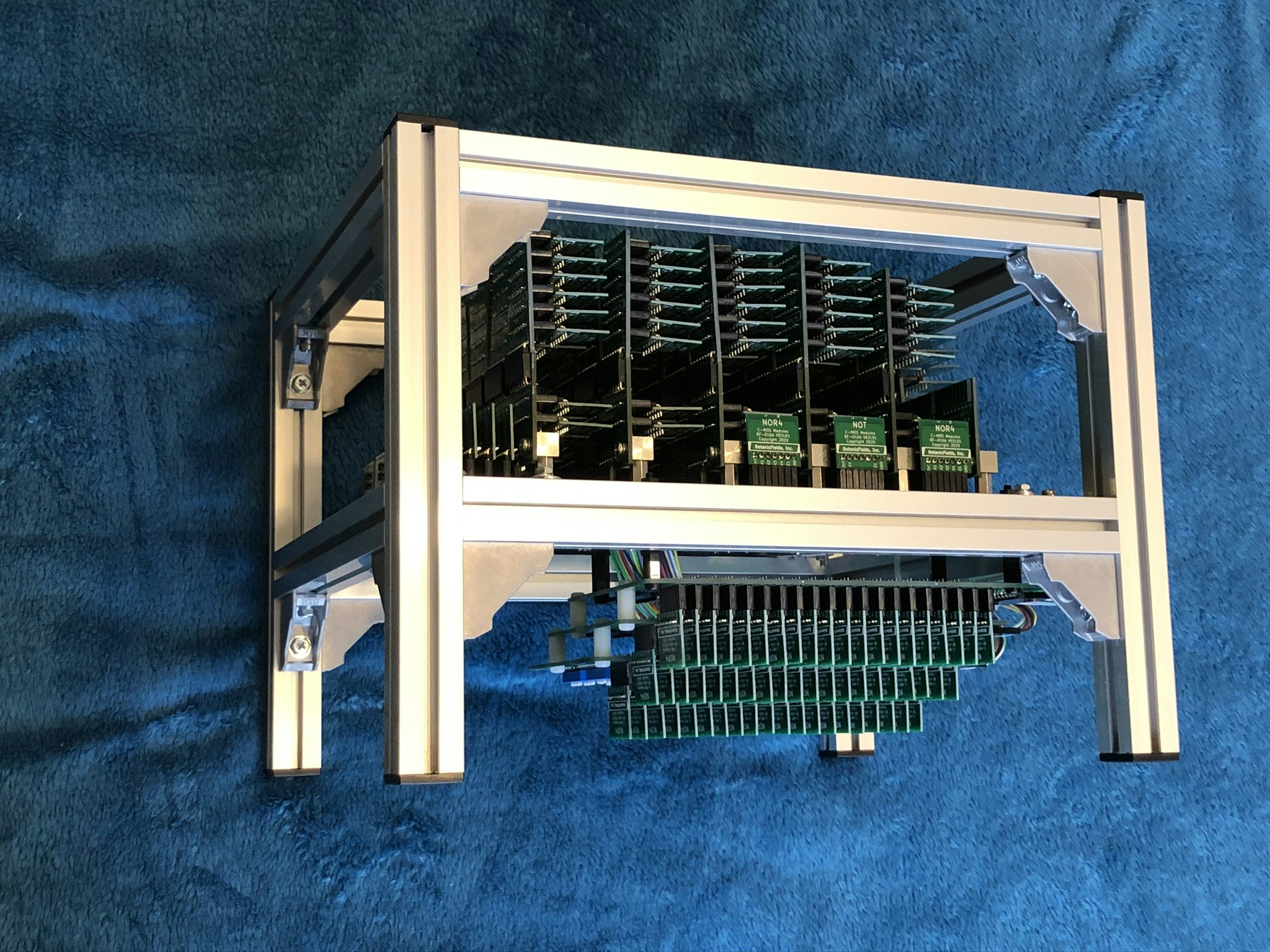

3.1 論理ゲート基板

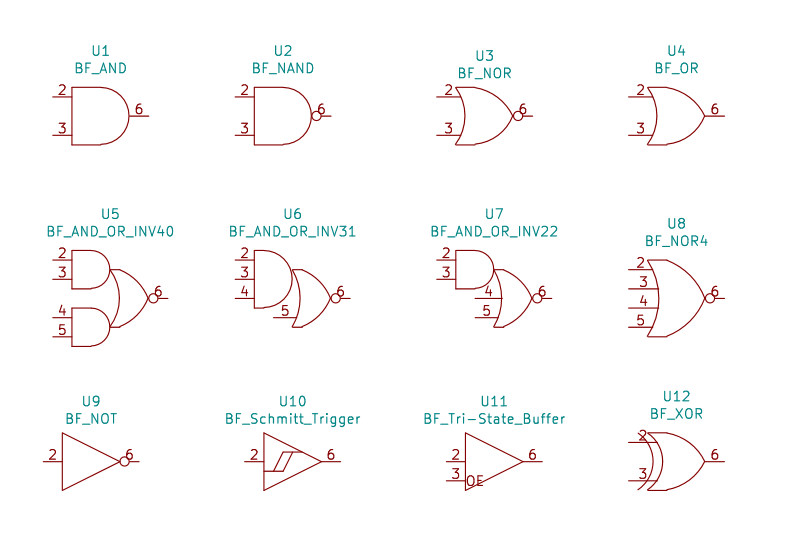

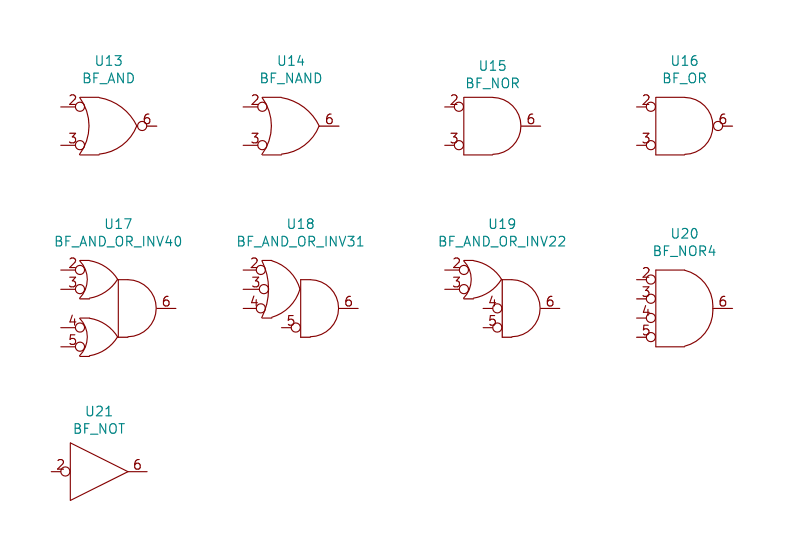

以下の 12 種類を用意します。装置全体まで設計してみて必要なものを選択します。4 入力 NOR は、4 bit コンピュータで有意義に使えます。今回、出番が少なく代替が可能なものもありますが、他への流用も考慮して基本的な論理ゲートについては用意することにしました。

- NOT

- Schmitt Trigger

- Tri-state Buffer

- NAND

- NOR

- AND

- OR

- XOR

- AND-OR-INV40 .. 2 つの 2 入力 AND の出力を OR 後、反転

- AND-OR-INV31 .. 3 入力 AND の出力と1入力を OR 後、反転

- AND-OR-INV22 .. 2 入力 AND の出力と 2 入力を OR 後、反転

- NOR4 .. 4入力 NOR

論理ゲート基板のシンボルは、MIL 論理記号のお椀型に似せて作成しました。

ド・モルガンの定理による変換にも対応しています。

LED

論理ゲート基板には LED を載せます。論理ゲート基板の 1 辺にはピンヘッダを実装します。LED はピンヘッダとは反対側の辺に置きます。入力・出力の両方を LED 表示するとわかりにくくなると考え、出力に絞ります。出力 L で緑色、H で赤色を点灯します。両方が点灯することはありません。緑色/赤色の LED は、出力から電流制限抵抗を介して電源またはグランドに接続します。

トライステートバッファの場合、バス接続した別のバッファがバスを駆動すると出力に接続した LED がバスに引きずられて点灯してしまいます。ハイインピーダンス時に両方とも消灯する様、LED 専用の MOS-FET を設けます。現在どのバッファがバスをドライブしているかが判ります。

信号ピンの割り当て

論理ゲート基板のピンヘッダは全て 7 ピンとし信号の割り当ては統一します。

- 電源(3.3V)

- 入力 1

- 入力 2

- 入力 3

- 入力 4

- 出力

- グランド(GND)

プルアップ、プルダウン

一般に未使用の入力は H または L に接続する空き端子処理が必要です。論理ゲート基板において論理和の入力の場合はプルダウン抵抗(L)を、論理積の入力の場合はプルアップ抵抗(H)を付けます。これによりブレッドボードでの実験で、未使用端子を処理する手間が省けます。また、論理ゲート基板の代用が可能になります。例えば、NOT の代わりに NAND や NOR を挿しても NOT として動作できます。ピン配置に互換性があり、かつ未使用入力が論理に影響がないレベルに固定されるからです。

プルアップ、プルダウンの副作用

プルアップの入力とプルダウンの入力を接続すると、電圧が電源とグランドの中間レベルになります。入力を 3 つ以上を接続した場合は、さらに複雑なレベルになります。何らかの出力でドライブされれば問題はありません。空き端子の仕様を理解していないと思わぬトラブルの原因になる可能性があります。

採用しなかった案

反転・非反転の両方の出力を持たせることにより論理ゲート基板の種類を減らすことを考えました。結局、単機能の基板を多種類作成することにしました。

- 反転と非反転の両方を同時に使用することは少なく、MOS-FET が無駄になる

- NOT の所要が多い。NOT のプリント基板がないと、MOS-FET の無駄が多い

- 回路シンボルが複雑化し無粋になる。回路図作成が楽しくなくなる

- 論理ゲート基板をできる限り小さくしたい

3.2 全加算器

1 bit の全加算器の機能をもつ論理モジュール基板です。4 bit 加算器の論理ユニット基板での使用を考慮して入力の一方を反転する機能を追加します。この機能は除算で使用します。今思えば、入力の反転機能は上位の 4 bit 加算器ユニット基板が担うべきだったかもしれません。

3.3 フリップフロップ(FF)

1 bit の SR マスタースレーブ FF 機能をもつ論理モジュール基板です。4 bit レジスタの論理ユニット基板の回路と合わせて D-FF になります。コンピュータのリセット動作のため、マスター/スレーブ両方の FF をクリアする非同期リセットを追加しています。

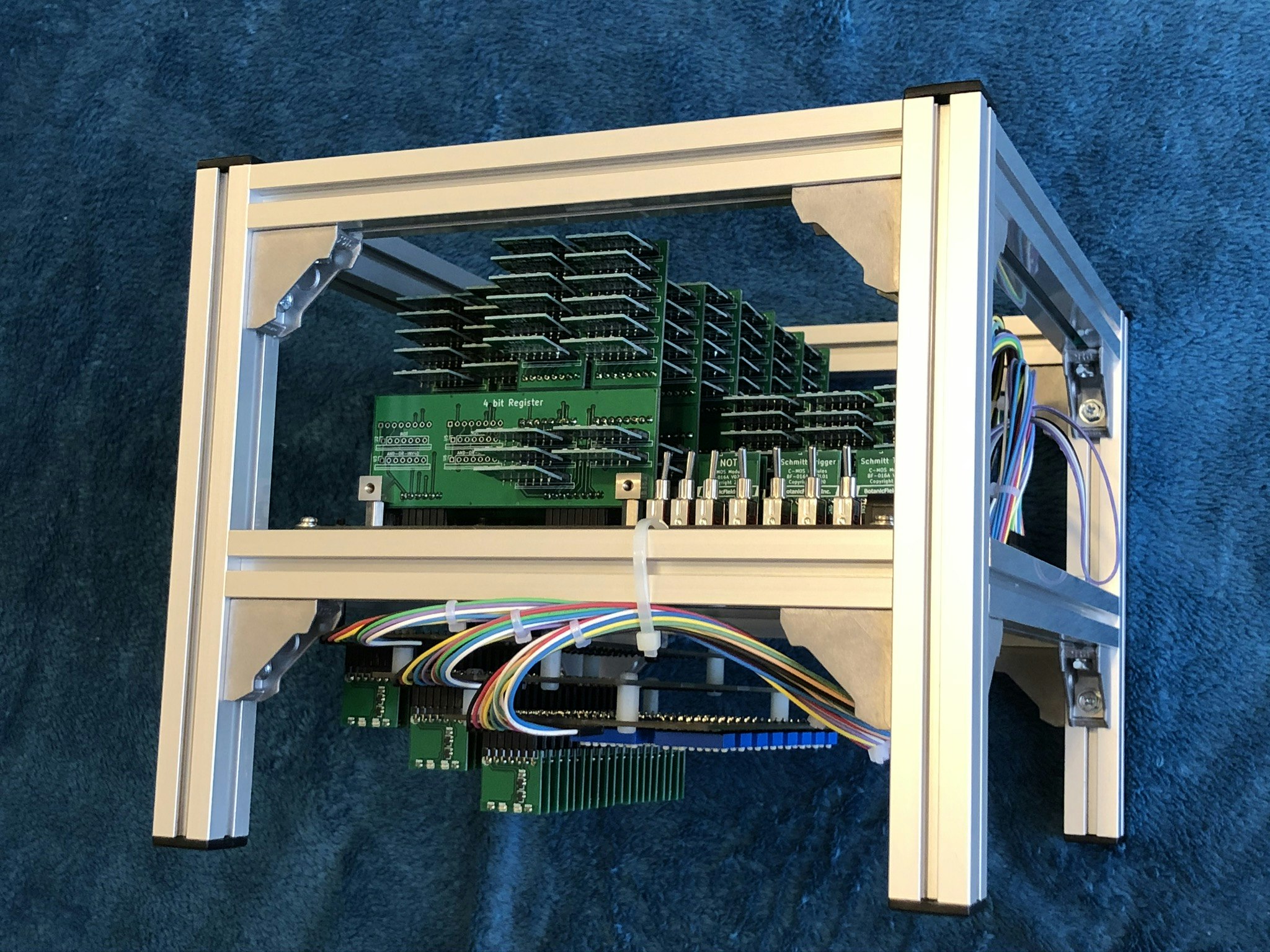

3.4 4 bit 加算器

全加算器の論理モジュールを 4 個搭載します。入力 A, B を各々強制的にゼロにする回路を備えます。引き算を指定できます。

3.5 4 bit レジスタ

SR マスタースレーブ FF の論理モジュールを 4 個搭載します。データをロードするか保持するかを制御できます。

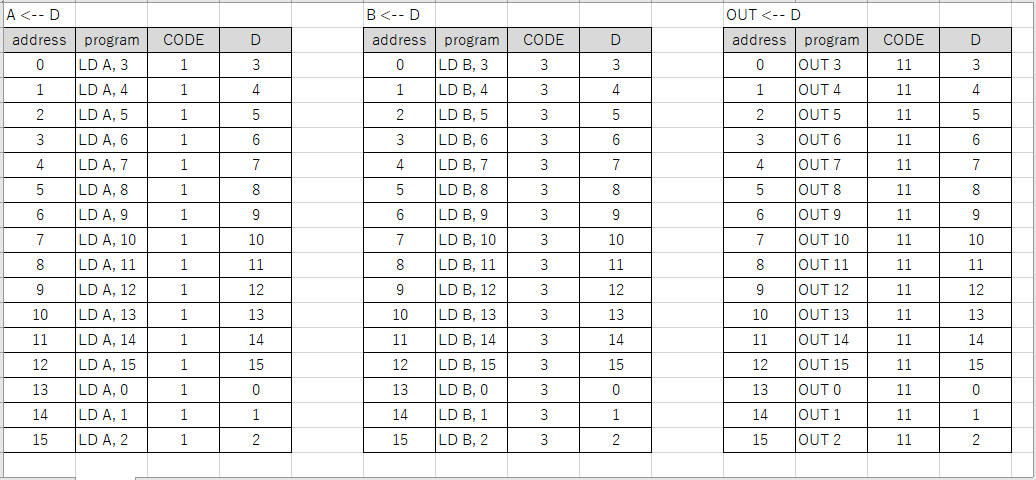

3.6 ROM

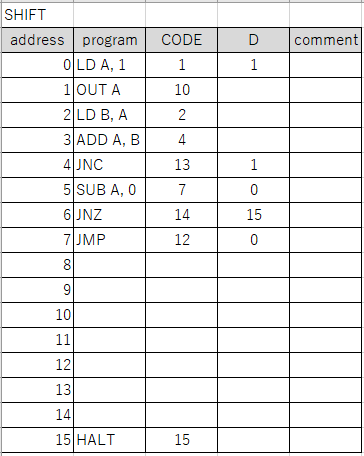

8 bit のデータ 16 個を予め設定し 4 bit のアドレスで選択して出力します。

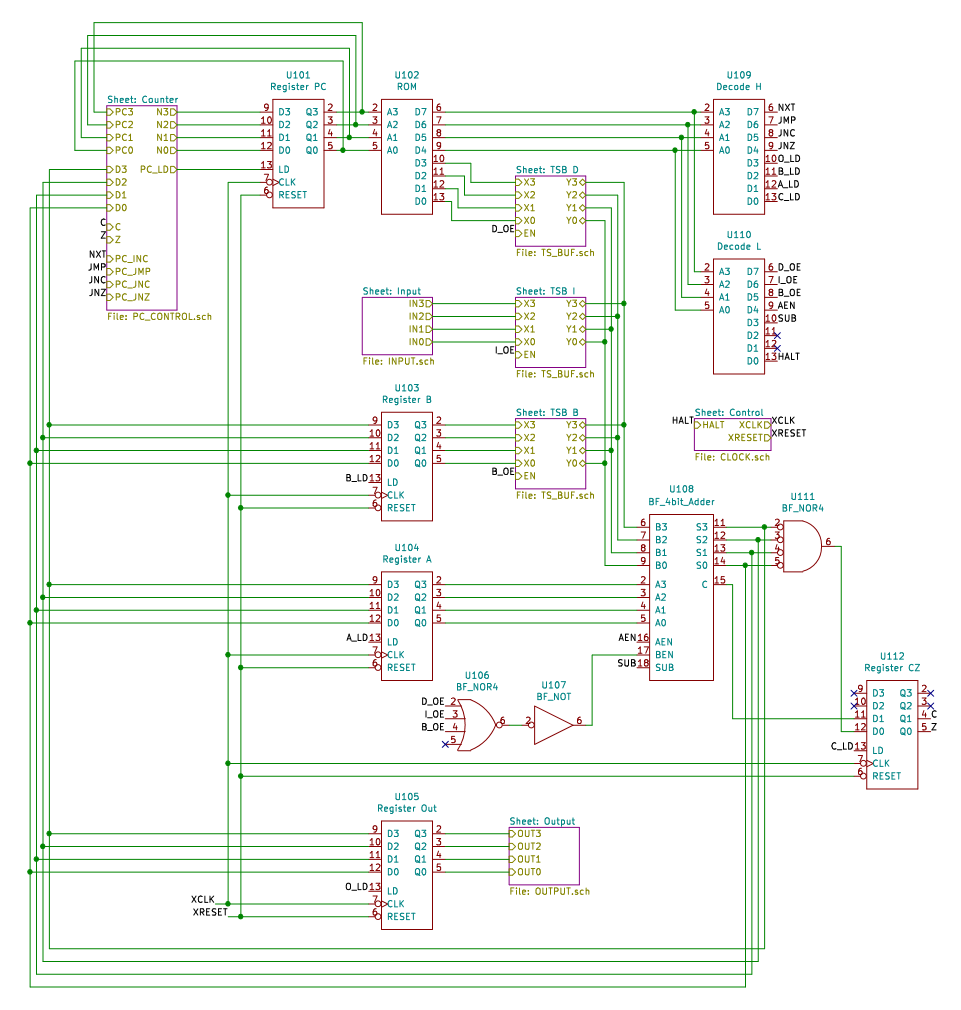

3.7 装置全体

コンピュータ全体の回路図です。今回作成した論理ユニット基板、論理モジュール基板、論理ゲート基板のシンボルと、別ページに階層化した回路を繋いでいます。

3.7.1 演算器

4 bit 加算器ユニット基板を 1 個使用します。コンピュータの回路図上で線の交差が少なくなる様にシンボルのピン配置を決めました。

3.7.2 レジスタ

4 bit レジスタユニット基板 5 個を以下の用途で使用しています。

- A レジスタ

- B レジスタ

- OUT レジスタ .. 出力信号データを保持します。

- プログラムカウンタ(PC)

- キャリー・ゼロ(CZ) .. 2 bit 分だけ使用します。

3.7.3 ROM

ROM モジュール基板です。8 bit のプログラム(命令コード 4 bit、即値データ 4 bit)を保持します。

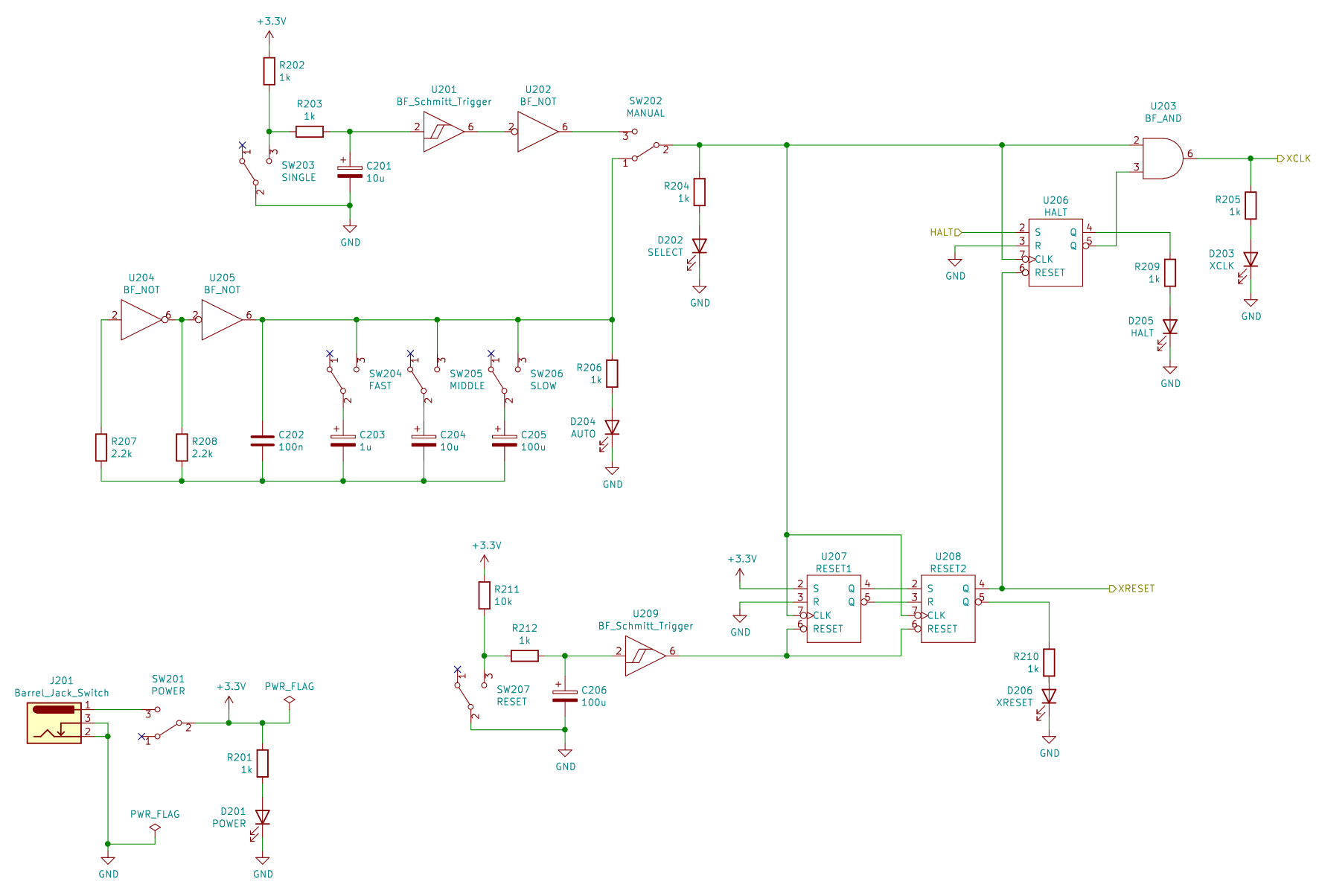

3.7.4 コントロール回路

階層化しています。クロック生成、ホールト、リセット、操作スイッチ、電源が含まれます。

クロック生成

周波数を4段階(約 2kHz、約 200Hz、約 20Hz、約 2Hz)に切替できます。マニュアル操作に切替できます。

ホールト

ホールト命令実行によりホールト状態となり、クロック配信(Gated Clock)を停止します。ホールト回路の FF は生クロック(Free Run Clock)で動作します。

リセット

リセット信号は、スイッチ操作により非同期にオンになります。全レジスタをゼロクリアしホールトを解除します。リセットがオンの状態ではクロックは配信されていますがレジスタはゼロのままです。リセット解除はクロックに同期させます。リセット解除によりプログラムカウンタがゼロの命令から実行を開始します。リセット回路の FF は生クロック(Free Run Clock)で動作します。

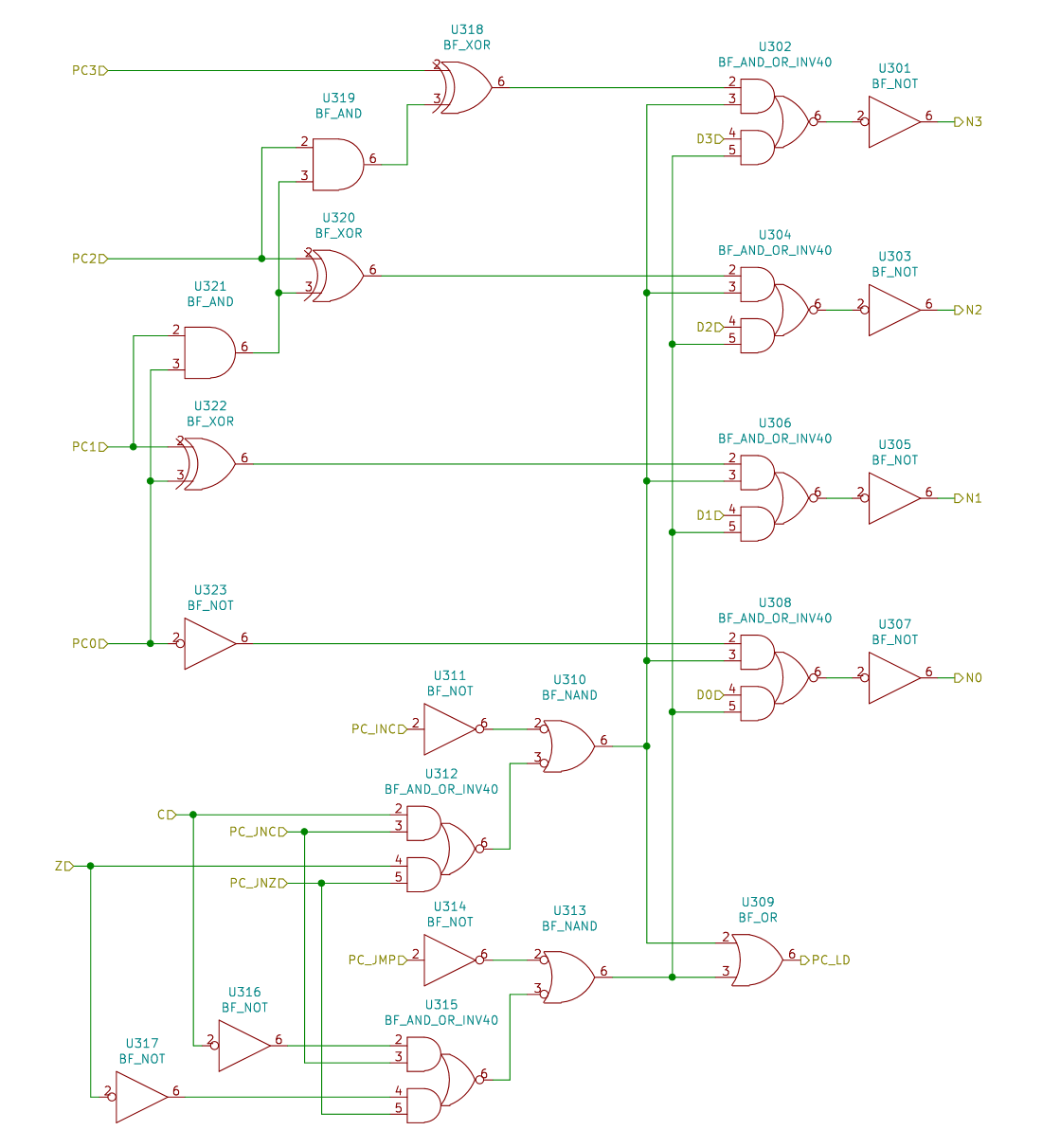

3.7.5 プログラムカウンタ回路

階層化しています。プログラムカウンタへの入力は、命令の種類と条件(ゼロ、キャリー)に拠って、インクリメント演算結果か、または ROM の即値データのいずれかになります。

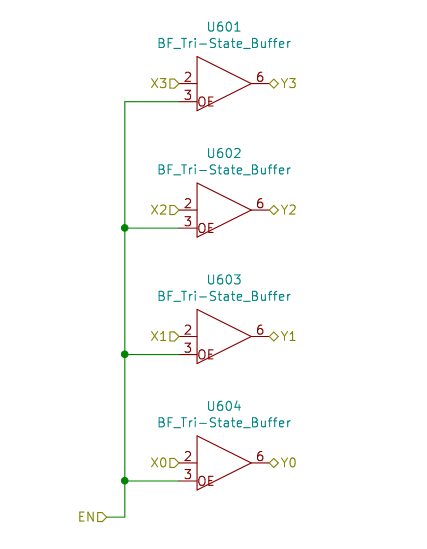

3.7.6 バスドライバ回路

階層化しています。バス接続のためのトライステートバッファです。回路は 1 種ですが、インスタンス(実体)は 3 組あります。

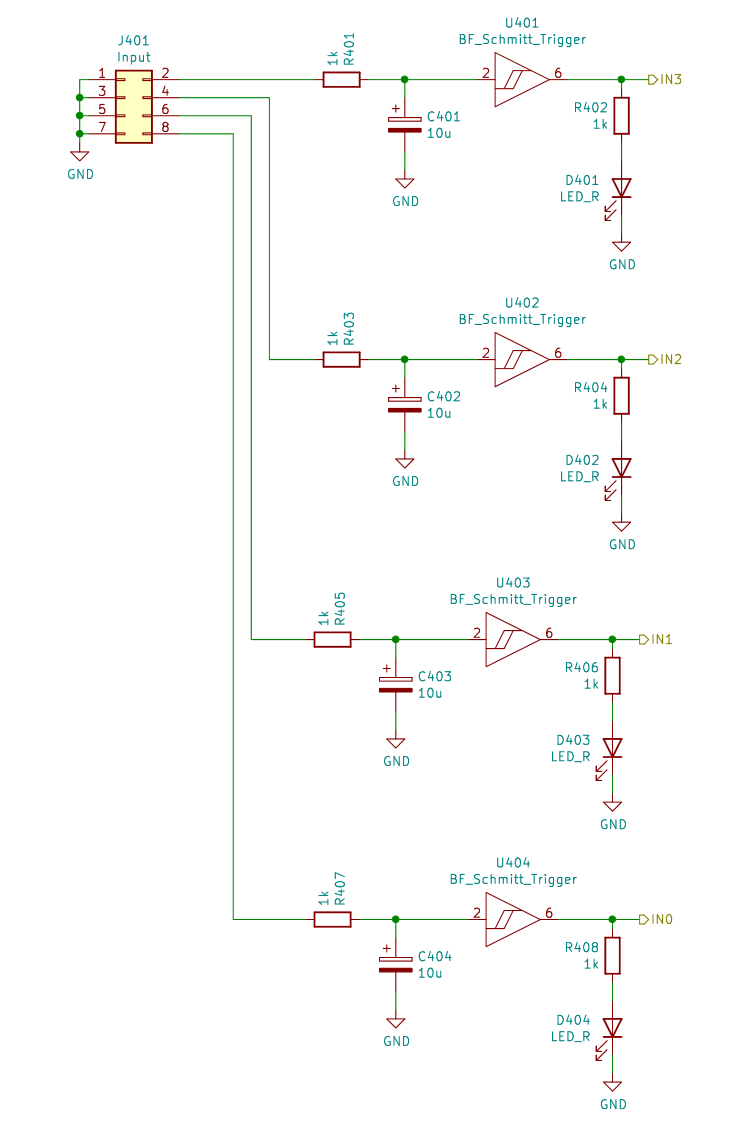

3.7.7 入力回路

階層化しています。シュミットトリガーを使用しています。入力にはピンヘッダを使用することを想定しています。

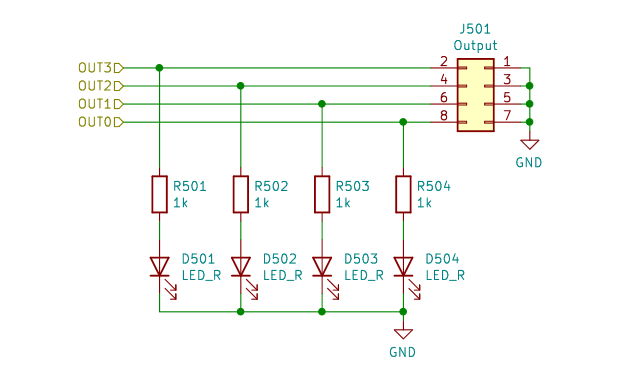

3.7.8 出力回路

階層化しています。GND ピンの位置関係が入力回路と逆になっています。出力にはピンソケットを使用することを想定しているためです。

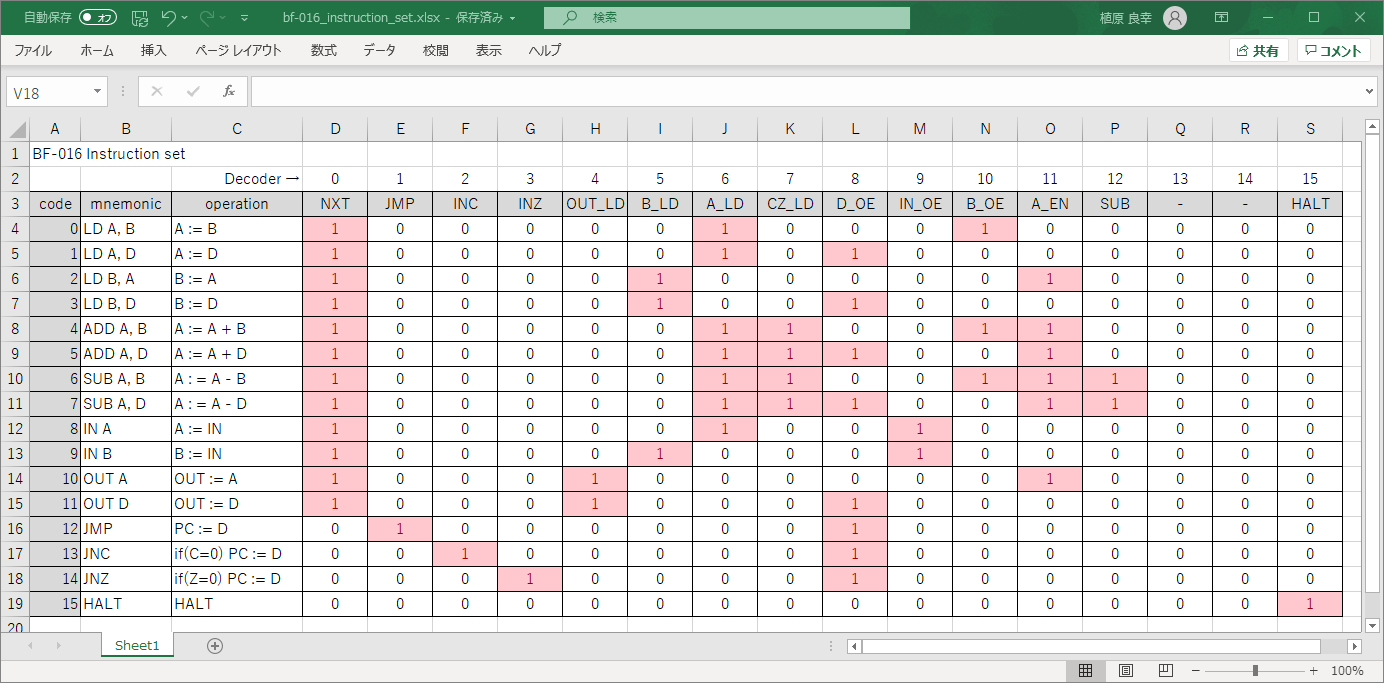

3.7.9 命令デコーダ

ROM モジュール基板 2 枚を命令デコーダとして使用し、レジスタや演算器などへの制御信号を取り出します。デコードの仕様を変更して命令の動作を変更することは比較的容易です。例えば、ジャンプしながらデータ転送や演算をしたり、複数のレジスタに同じデータを同時に格納したり、といったことが可能な範囲でできます。

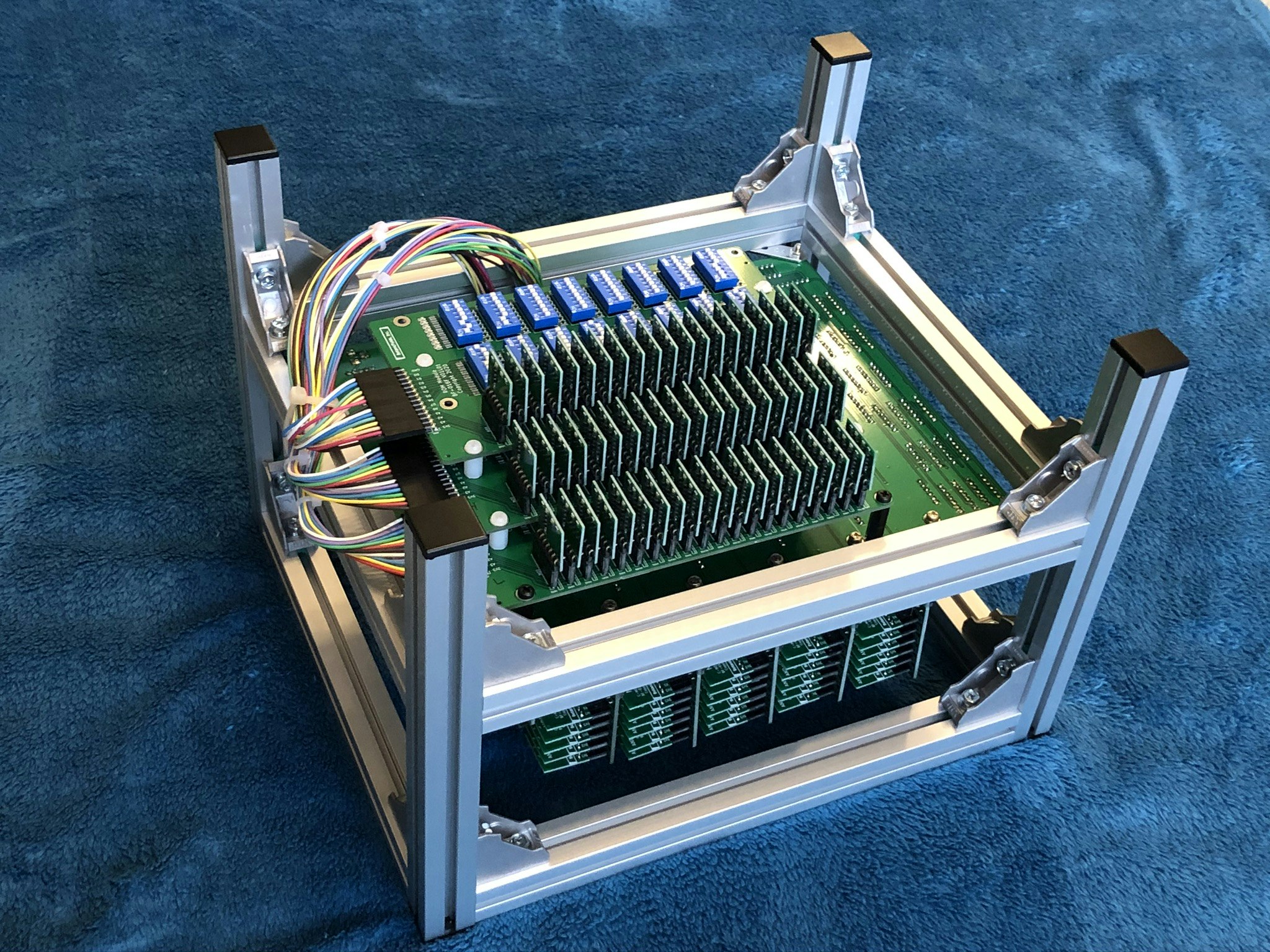

3.8 部品の数

コンピュータ全体では、論理ゲート基板が 303 個、MOS-FET が 1,482 個の規模となりました。

4. 実装設計

論理ゲート基板、論理モジュール基板、論理ユニット基板、コンピュータ基板の製造データを設計します。

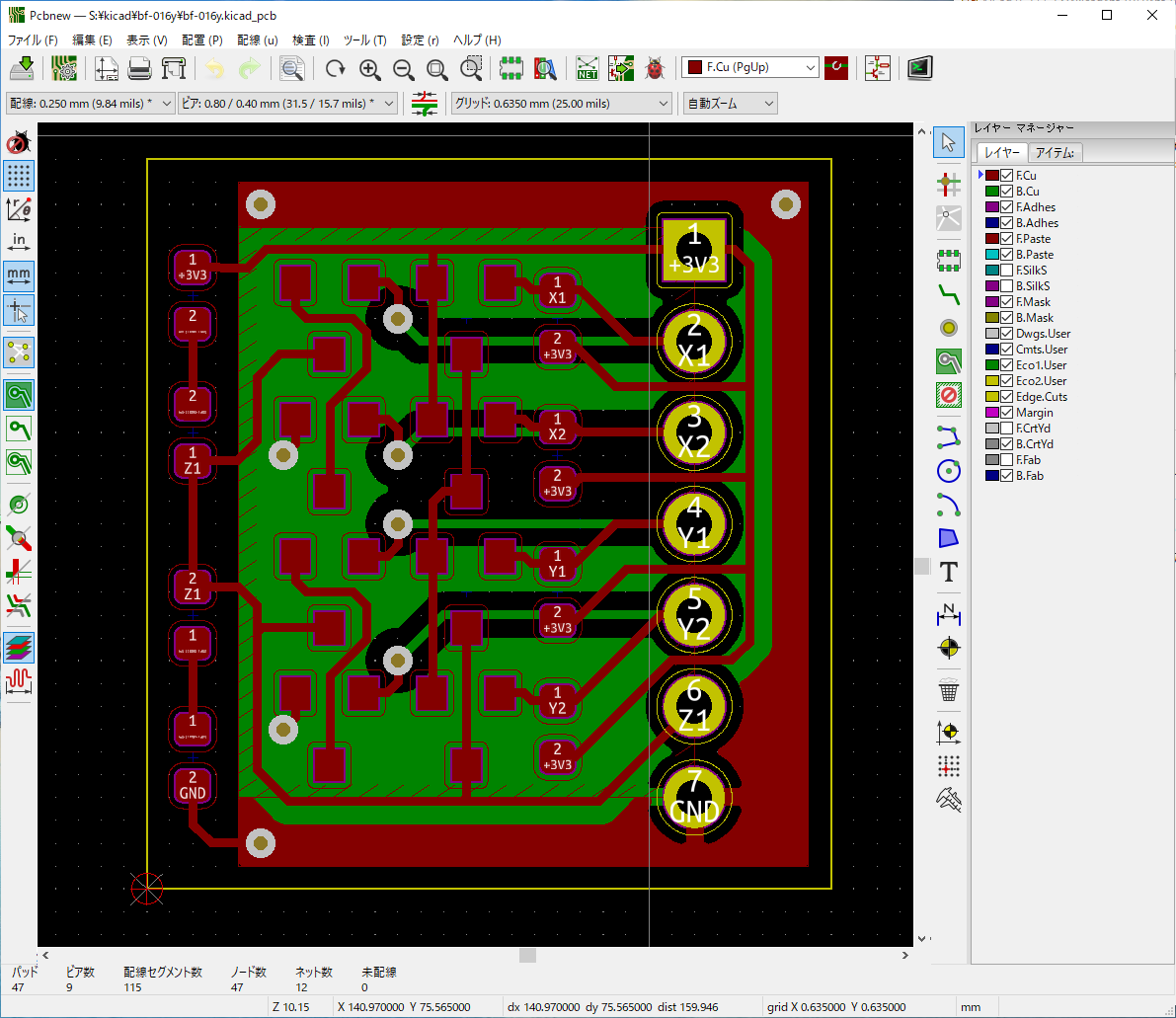

4.1 プリント基板レイアウトエディタ

KiCad の基板レイアウトエディタは PcbNew です。レイアウト設計後、プリント基板製造データ(gerber)、部品配置データ(Pick & Place または POS)を出力し製造業者に送付します。なお、部品表(BOM)は、Eeschema で出力します。LED の周りの銅箔は無くし、LED の点灯が裏側からもわかるようにします。

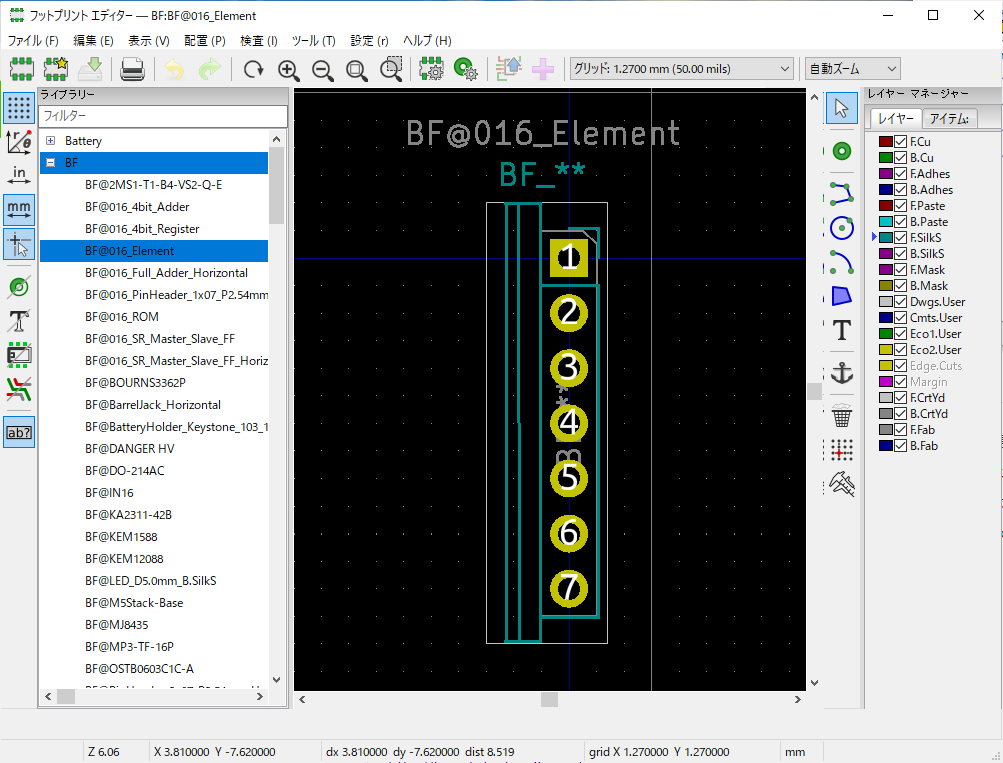

フットプリントエディタ

円滑なレイアウト設計のために、論理ゲート基板、論理モジュール基板、論理ユニット基板の外形を KiCad の Footprint Editor で作成しました。論理モジュール基板(SR フリップフフロップ)の外形は、垂直挿しと水平挿しの 2 種を作成しました。

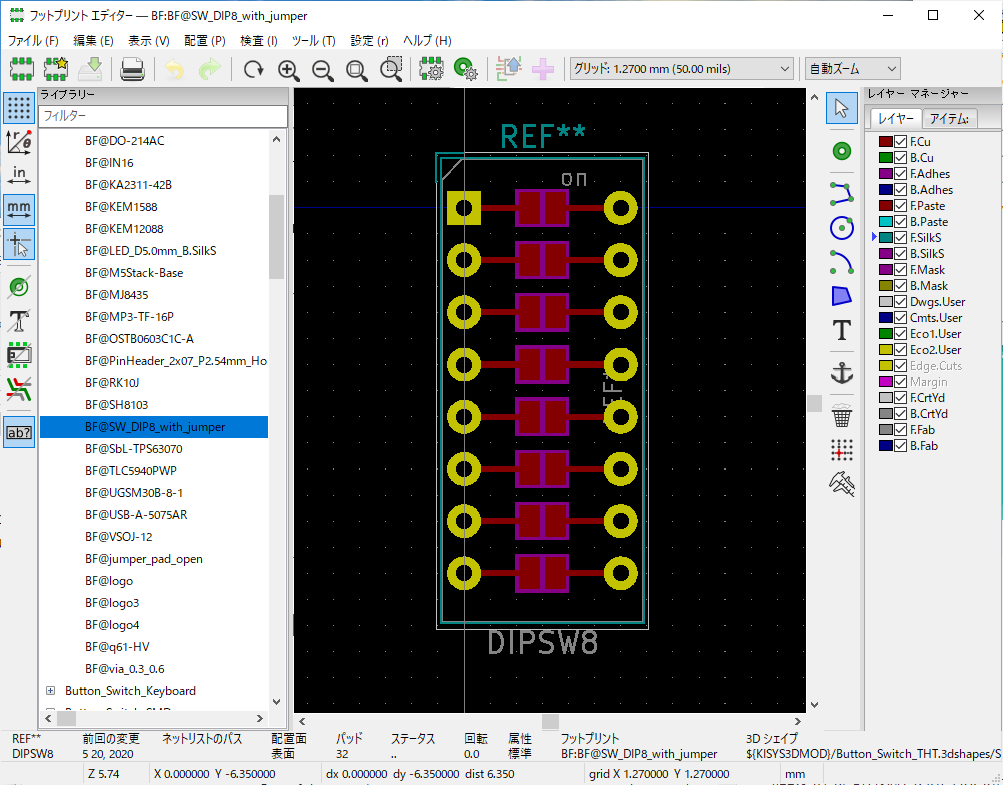

フットプリントのカスタマイズ

ROM モジュール基板では DIP-SW を 16 個使用します。プログラムの書き換えのためには切替スイッチが便利です。命令デコーダとして使用する ROM 2 枚は、書き換え頻度が少ないです。DIP-SW に代えてハンダブリッジによるジャンパ接続を選べる様にします。そのためには DIP-SW とジャンパを合成したフットプリントが必要です。スルーホールと表面実装パターンの接続は、基準点を意識して接続することで実現できました8。

4.2 SMT 実装サービス

MOS-FET、抵抗、LED には表面実装部品(SMT, SMD)を使用します。手作業でのハンダ付けが可能な大きさの部品を使用しますが、プリント基板実装サービス(PCBA)の利用も可能です。JLCPCB9の SMT 実装の特別価格キャンペーンが渡りに船で、これを利用します。

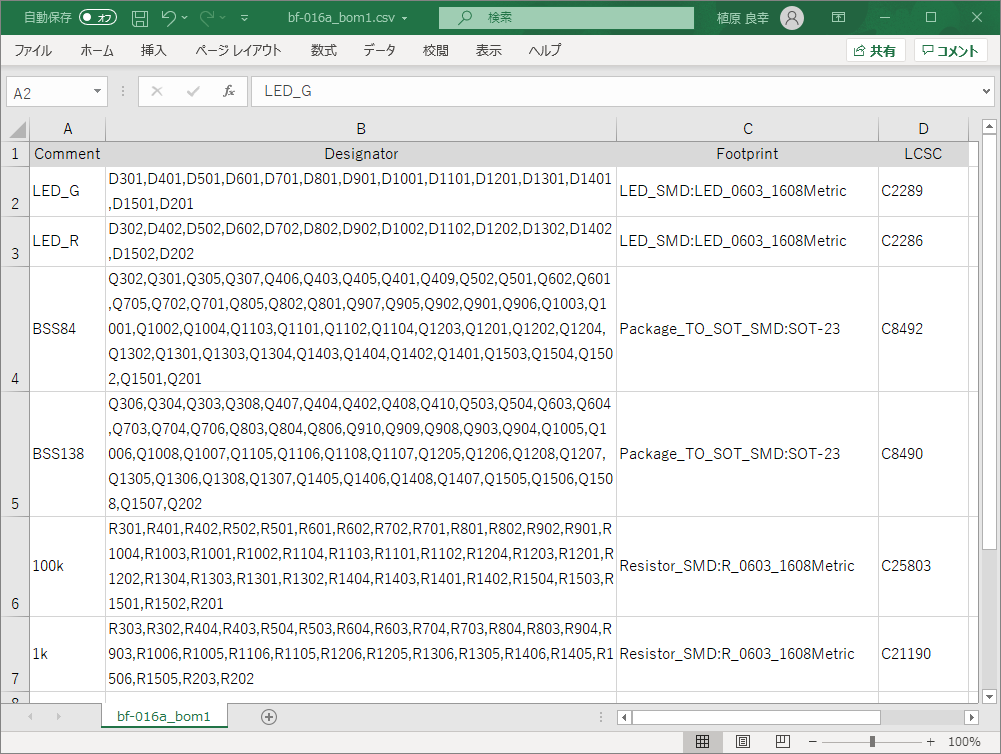

部品表

部品を JLCPCB の SMT Parts Library10で選択し、商品番号(LCSC番号)を Eeschema で出力した部品表(BOM)に追記します。LCSC 番号は、系列の部品センター LCSC11が使用している番号です。

Basic, Extended

JLCPCB の SMT サービスでは、部品に Basic、Extended の区別があります。Extended の部品は 1 種毎に $3 が加算されます。Basic を基本に安価なもの、在庫の多いものを選びました。メーカーで価格が異なるなど部品選びは楽しい作業ですが嵌ると時間がかかります。

余計な部品、複数使用する部品

実際には使っていない部品が部品表に含まれていても大丈夫です。アノテーションで割り振られた部品識別番号を Designator 欄から探し出して部品を特定してくれます。また、後に説明する面付けでは同じ部品識別番号が複数使用されることになりますが、問題なく処理されます。

在庫不足

生産が開始され、最初のレビューの段階で部品の在庫不足が判明すると、そのプリント基板がキャンセルとなり、オーダー全体がストップします。部品表を見直して再投入します。速やかに行えば同じオーダーに追加できます。再投入後、残りを再開すると確実と思います。

キャンセル分は即座に返金処理されます。クレジット払いだと全体分の引き落としが翌月なのに対し、返金が当月だったりします。Yahoo カードでは、返金が明細に記載されないまま総額から差し引かれるため確認には注意が必要です。同様の問い合わせが多いのかオペレータは手馴た対応でした。部品を選択し直して再投入すると、再投入分の製造費用が請求されます。送料のマージもうまくなされる模様です。

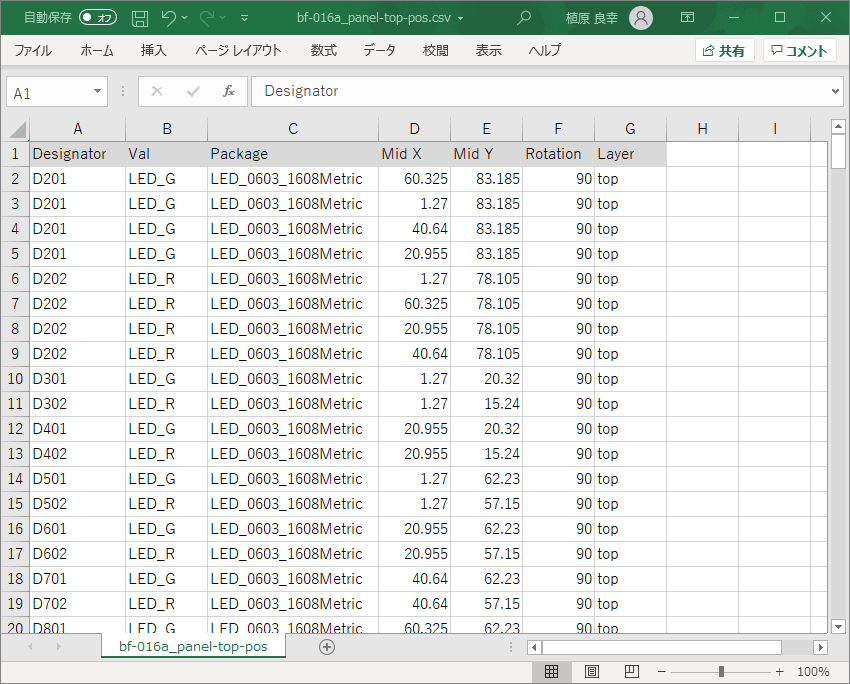

部品配置データ

部品配置情報は PcbNew で出力した CSV をヘッダーのみを修正してアップロードします。

JLCPCB のサイトに表示される画像では、部品の位置および回転が一様にずれています。KiCad と JLCPCB で基準が合っていないものと思われます。部品数が少ない基板では、ピッタリ合っていたケースがあります。どのような条件でずれるのか、詳細は不明です。

JLCPCB の技術者による修正が入ります。単純な設計ではありますが設計情報をアップロードするだけで何ら打ち合わせもなく実装済プリント基板が納入されるのが驚きです。

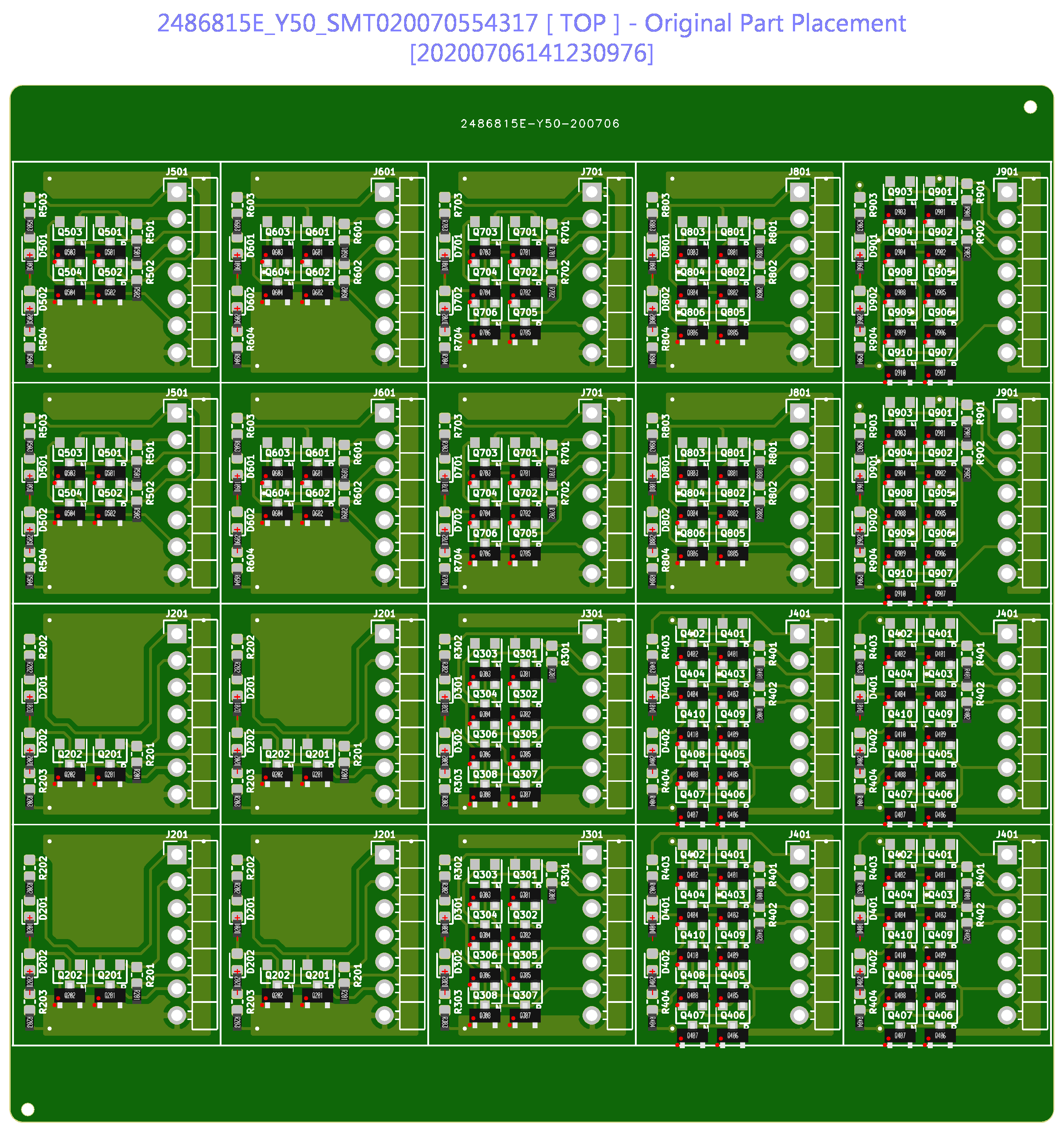

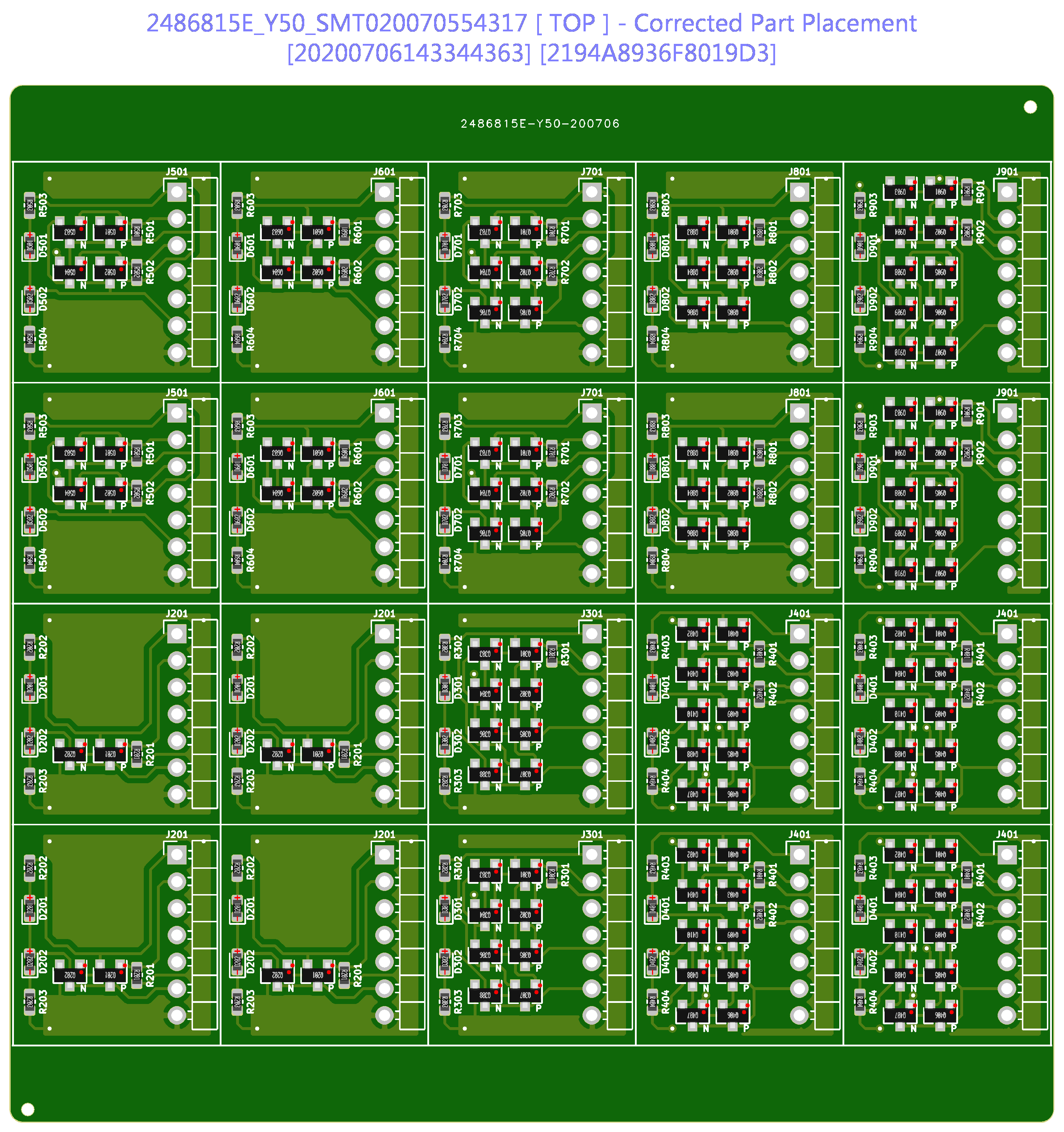

面付け

論理ゲート基板は、小さなプリント基板で多数必要です。10 x 10cm だと 20 枚分になります。プリント基板を複数並べて製造する面付け(panelize)をします。特に異なる種類のプリント基板を並べる異種面付けをすると、種類数に応じてかなり高額になります。

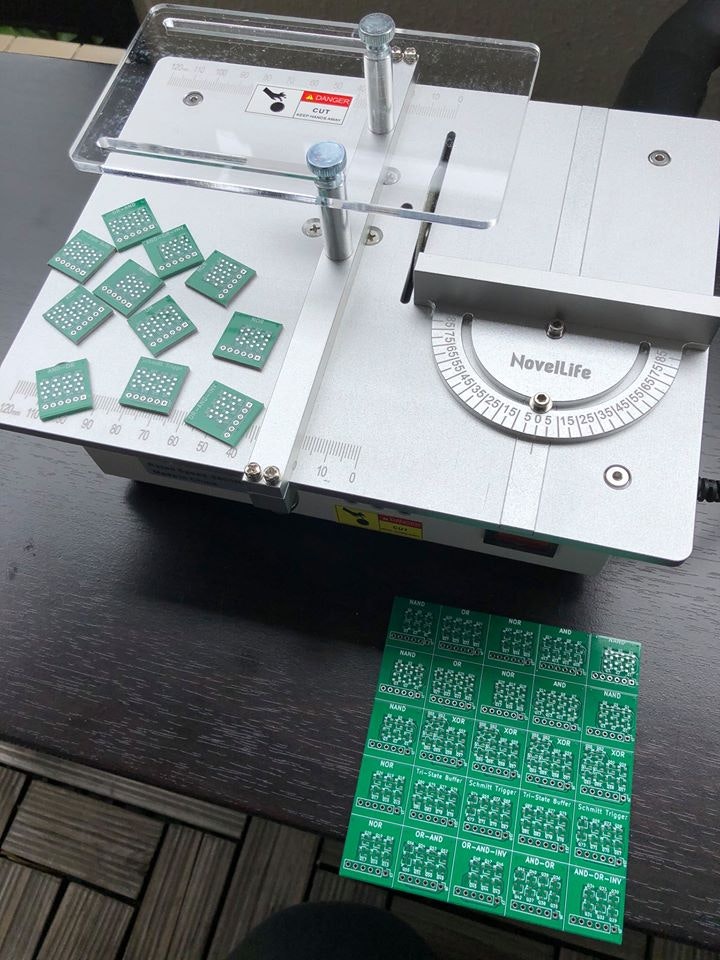

面付けでは、プリント基板を分割するための V カット加工やルータによるスリット加工を部品実装前に施します。しかし JLCPCB の SMT 実装特別価格では、V カットができません。プリント基板の切り出しは、自分で丸鋸盤12でやることとし、面付けのレイアウトも自分で作成します。

ガラスエポキシを切ると細かな粉塵が発生し吸い込むと健康を害します。別途製作したサイクロン集塵装置

片面実装

JLCPCB の SMT 実装特別価格は片面実装が条件です。DIY で丸鋸盤で切り出す場合も片面が有利です。当初、部品を両面に実装しプリント基板のサイズを小さくしようとしましたが、片面に部品を集めます。XOR は MOS-FET が 10 個必要で、これが論理ゲート基板の大きさを決めます。

エッジレールと基準マーク

実装のためには、マウンタやリフロー装置のレールに載せるため基板両端に設けるエッジレール部や位置決めの基準マーク(fiducial)が必要です。エッジレールは製造装置内をスムーズに流れる様に角を丸くします。これらは JLCPCB の技術者が追加設計してくれますが、こちらでもある程度考慮します。エッジレールがない場合、プリント基板の空きスペースに基準マークや製造業者の管理番号が追加されたりします。

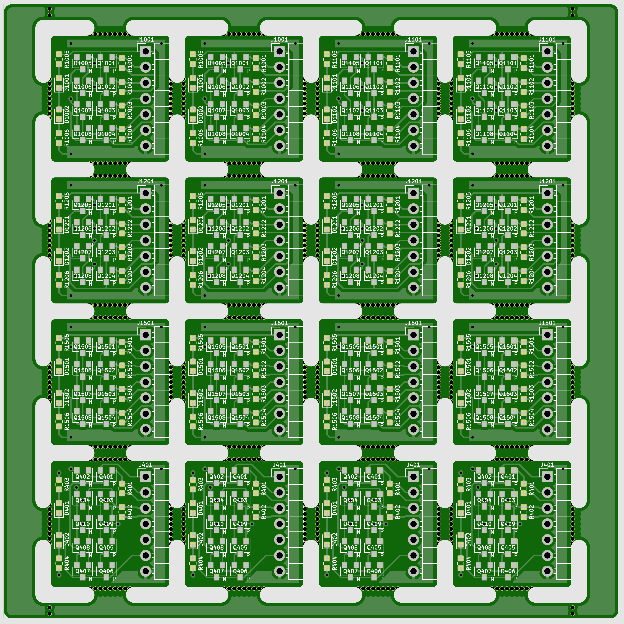

ミシン目(スリット加工)による面付け

ミシン目(スリット)、マウスバイト(mouse bite)による面付けができました16。JLCPCB の SMT 特別価格でも受け付けてくれました。10cm x 10cm に面付けできる数が 16 枚に減りますが、丸鋸盤の騒音や粉塵から解放されます。

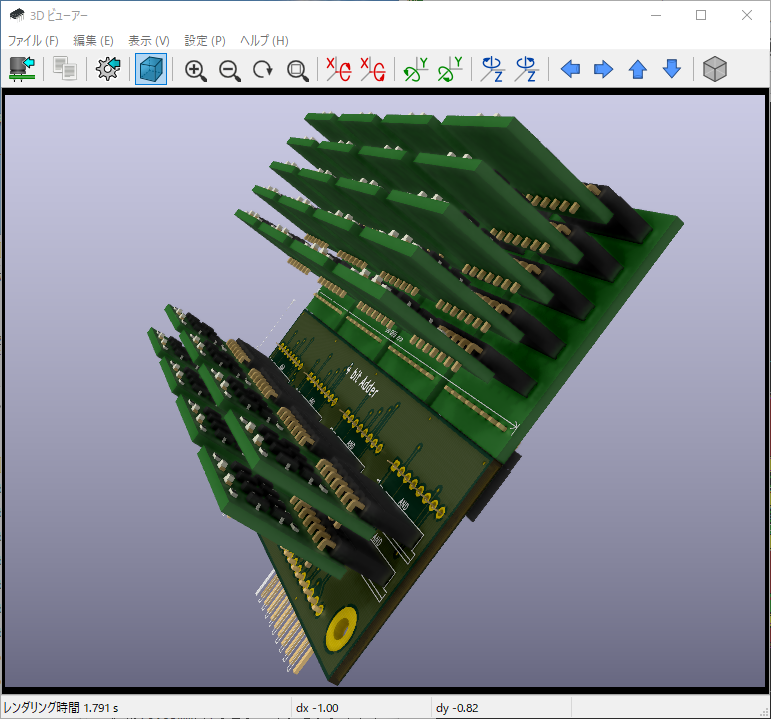

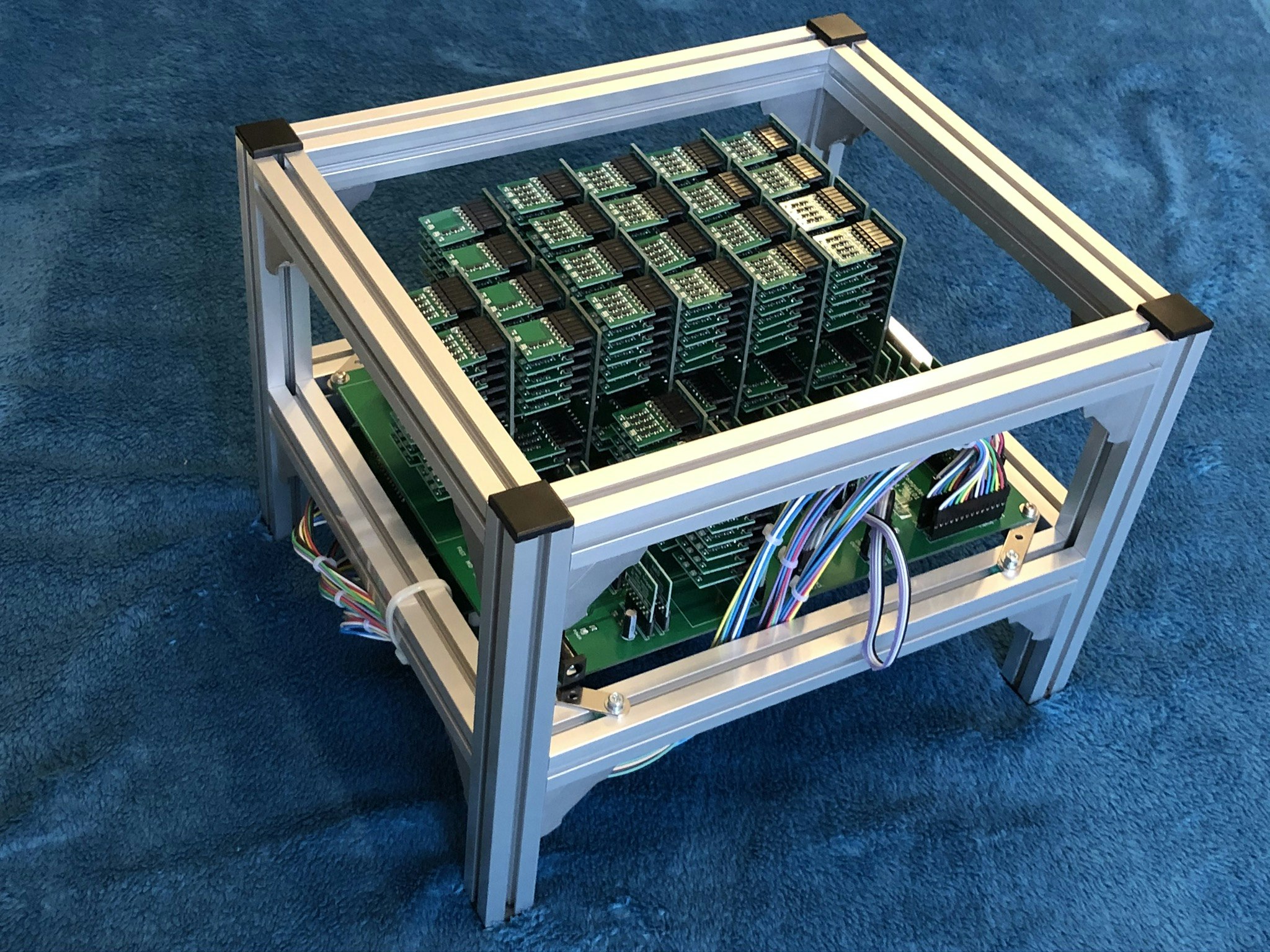

4.3 立体構造にする

階層化した基板を立体的に組み上げてプリント基板面積を節約します。プリント基板を 10 × 10cm 以内に収めることを意識します。論理ゲート基板は、1 端に 2.54mm ピッチ 1 列の L 型ピンヘッダを備えます。

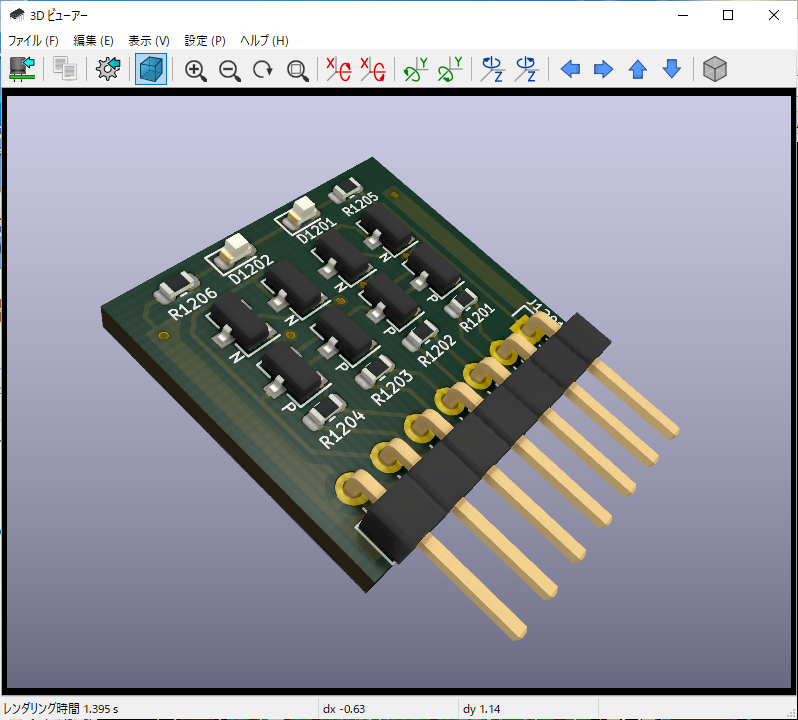

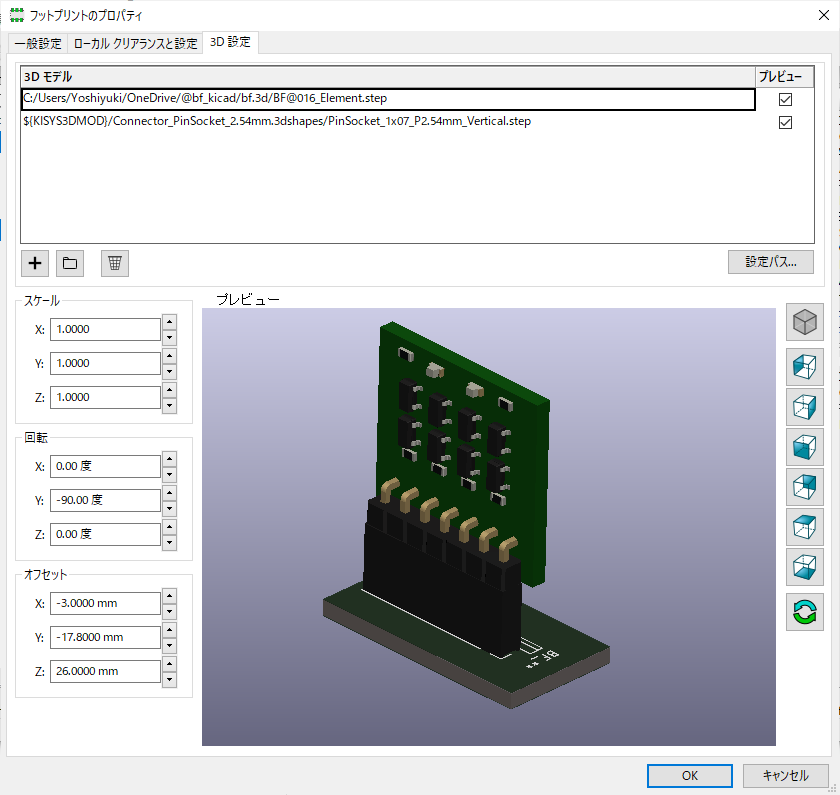

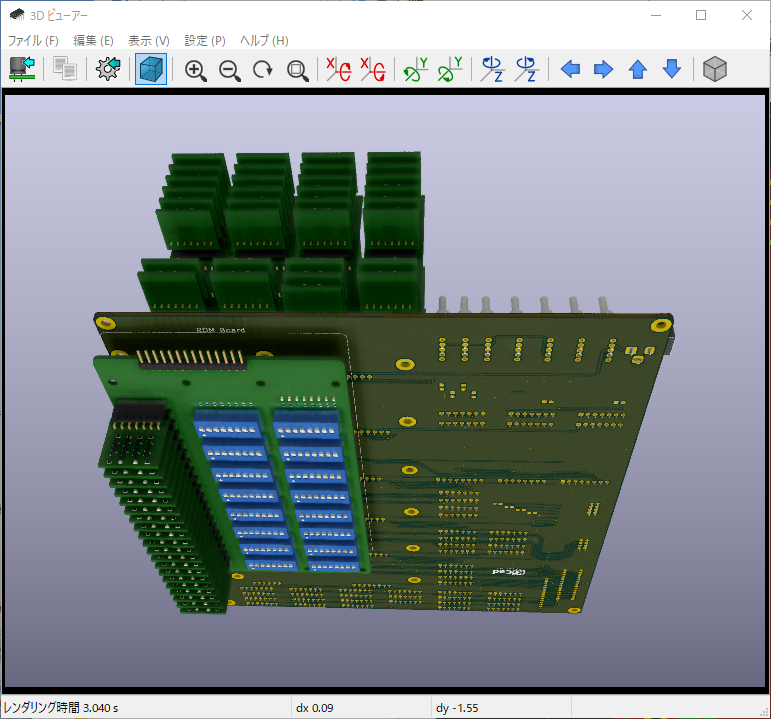

3D 表示

PcbNew でプリント基板の 3D 表示ができます。

フットプリントには 3D 表示データを紐づけできます。PcbNew が生成する 3D 表示データを利用します。ピンソケットの 3D データも必要です。KiCad に添付されているデータを使用します。

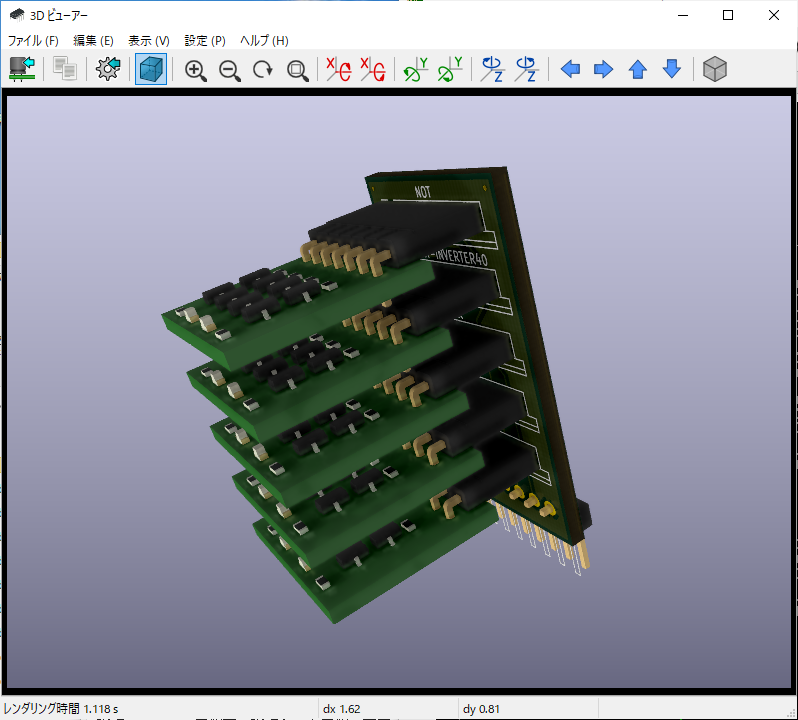

2 種の論理モジュール基板は、論理ゲート基板をドーター基板として垂直に差し込むピンソケットを備えます。論理モジュール基板自身も、1 端に 2.54mm ピッチ 1 列の L 型ピンヘッダを備えます。ピンからの電源の配線を考慮し、かつドーター基板が上を向くようにピンヘッダは裏面に配置します。論理モジュール基板(SR フリップフフロップ)のフットプリントは、垂直挿しと水平挿しの 2 種を作成しましたが、各々に 3D データを作成します。

論理ユニット基板 2 種は、論理モジュールや論理ゲート基板をドーター基板として差し込むピンソケットを備えます。既に立体構造となっている論理モジュールをスペース効率良く搭載するために基板の端に L 型ピンソケットを 4 個配置します。論理ゲート基板の実装方向が揃う様に、ピンソケットは裏面に配置します。論理ユニット基板自身も 2.54mm ピッチ 1 列の L 型ピンヘッダを 1 端に備えます。これら論理ユニット基板には重さを支える機構も設けます。

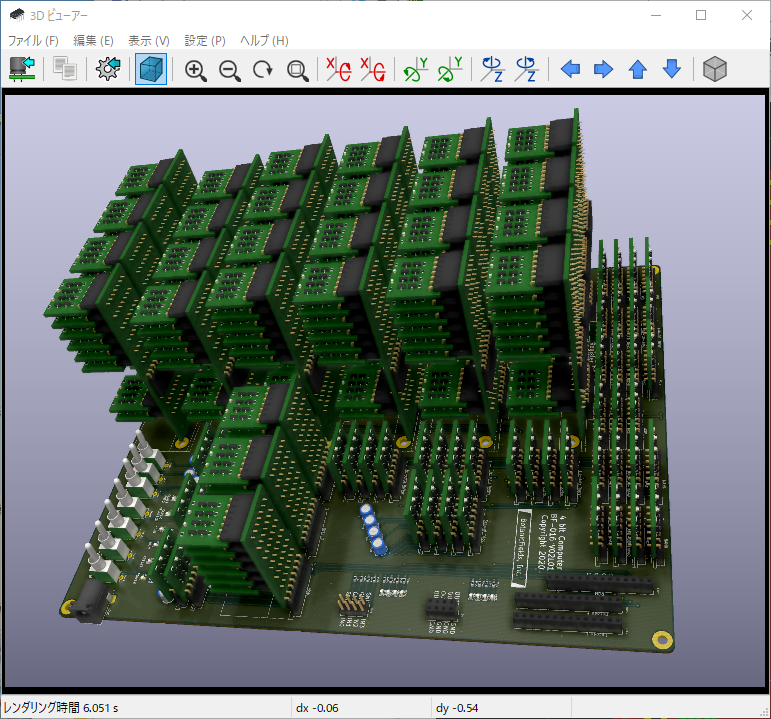

装置全体の 3D 表示です。ネジ、スペーサ、命令デコーダー ROM、ROM への配線は表示がありません。ROM モジュールの取り付け穴は 4 個ずつ 2 組設けました。3 枚を組み上げる場合に論理ゲート基板の高さを避け、ずらして組みます。

KiCad に添付されていない3Dデータ

コンピュータ全体の 3D 表示に必要な DC ジャックとトグルスイッチの 3D データは、KiCad では提供されていません。DC ジャックの 3D データは Digi-Key17から、トグルスイッチは かんぱぱ さん18から拝借しました。

4.4 フレーム

装置全体を保持するフレームは、NIC のアルミフレーム19を用いました。モノタロウ20でカスタムサイズでオーダーし、丈夫で美しいフレームを大変安価に準備することができました。ブラケット、四角ナット、ナットホルダーなども併せて購入しますが、セット商品よりも別々で買った方が安かったり、納期が早かったりするので注意が必要です。

5. 動作

テストプログラムを作成して動作を確認します。

5.1 ROM データの A, B, OUT レジスタへのデータ転送

目視で確認します。

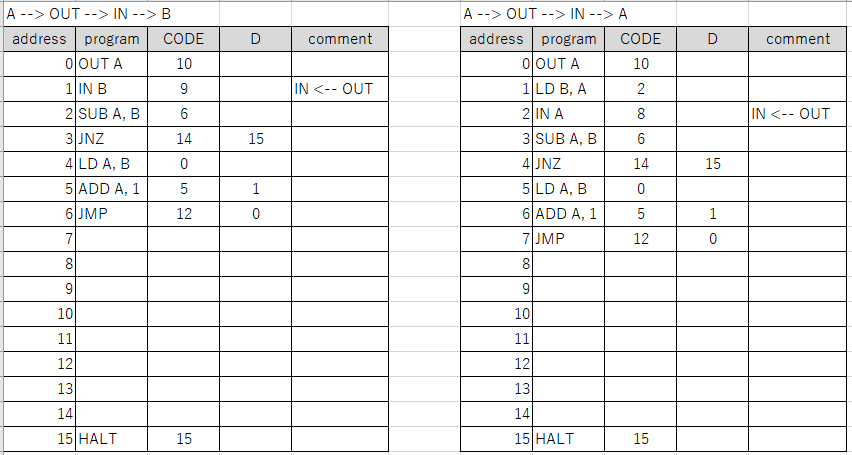

5.2 A, B レジスタと、OUT, IN のデータ転送

OUT 端子と IN 端子を接続(折り返し)して実行します。データの不一致を検出すると、ホールトします。左側のテストプログラムでは、クロック周波数が高いとIN 端子の積分回路のディレイのため不一致を検出します。右側のテストプログラムでは、OUT と IN の間に 1 ステップ入っているために 1 段高い周波数でも動作します。

5.3 最大カウント

A, B, OUT レジスタを使用して 16 x 16 x 16 = 4096 のカウントを繰り返します。目視で確認します。実行中の様子を Youtube21 に置きました。

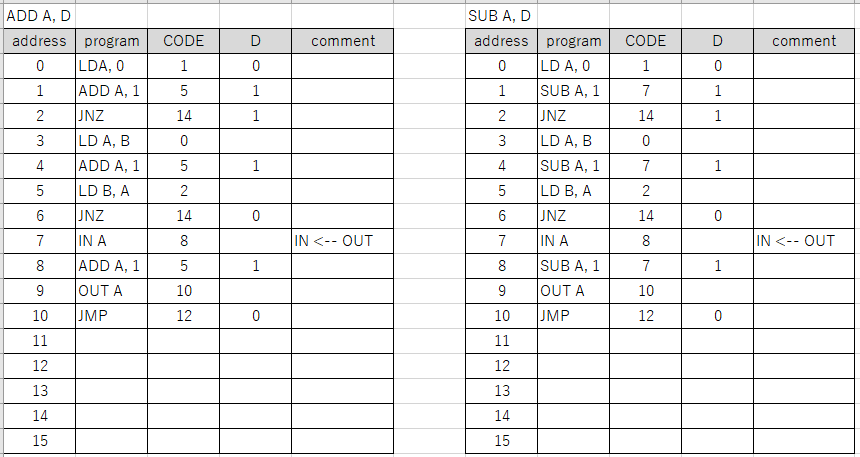

5.4 シフト

ADD A, B を使用して OUT レジスタのシフト動作を繰り返します。目視で確認します。

6. ブレッドボードで使う

論理ゲート基板,論理モジュール基板、論理ユニット基板は、ブレッドボードによる動作確認や実験に便利です。プリント基板の端の 2.54mm ピッチ 1 列の L 型ピンヘッダをブレッドボードに直接挿して、電源・グランド・入力・出力を接続できます。ブレッドボードに垂直に挿すことで、ジャンパ配線の穴を無駄なく利用できます。

細ピンをどうするか?

通常(0.65mm 角)のピンヘッダをブレッドボードに無理に挿すと、接点を痛めるなどブレッドボードを破損する原因になります。細ピン(0.5mm 角)のピンヘッダ22を使用するとブレッドボードに無理なく直接挿すことができます。

通常ピンソケットに細ピンヘッダを挿すことはできません。抜け落ちてしまいます。逆に細ピンソケットに通常のピンヘッダを挿そうとすると、挿せないだけでなくピンソケットが壊れます。

細ピンのピンソケットについては、現状ストレート23のみ入手可能で L 型が見当たりません。L 型を使いたい箇所がありますが、ないものとして考える必要があります。通常ピンと細ピンが混在しない様に注意が必要です。論理ゲート基板には、全て細ピンを使用します。論理モジュール基板、論理ユニット基板には通常のピンヘッダを使用することにします。

細ピンのピンヘッダ、ピンソケットは秋月電子通商で購入できます。通常ピンを細ピンに変換するのにも使える便利な変換基板24もあります。細ピンの L 型ピンソケットを取り扱ってくださいと希望を出しました。L 型ピンソケットは分割タイプが見当たりません。ピン数のバリエーションも問題です。

安全性の問題

現状のピン配置では、論理ゲート基板を左右逆に(裏表逆に)挿すと電源とグランドが逆に接続されてしまい、電源を投入した瞬間に MOS-FET を焼損してしまいます。対策として以下を考える必要があります。

- 逆挿ししても壊れない様にする。例えば、逆挿し時に電源が NC に当たる様にする

- 逆挿しできない様にする。例えば、ピンを1つ増やし逆挿し防止措置を施す

具体的には以下の様なピン配置にすることが課題です。逆挿しできないか、または逆挿ししても電源が接続されないので焼損を避けることができます。

- 入力 1

- NC (ピンヘッダーのピンを抜き、ピンソケットの穴を埋める)

- 入力 2

- 入力 3

- 入力 4

- 出力

- 電源(3.3V)

- GND

出力には特に保護が無いので電源やグランドと短絡すると大電流が流れ焼損します。トライステートバッファのバスファイトも深刻です。短絡やバスファイトから焼損を保護する過電流保護は課題です。

7. おわりに

資料を GitHub25に置きました。今回は私の最大規模でした。動かすことができて大変よかったです。途中、様々なことを発見・経験できました。

論理回路

- MOS-FET による回路(シュミットトリガー、トライステート、..)

- AND-OR を活用した回路

- ダイオードマトリクス(ROM)による命令デコード

- ホールトと同期リセット

- LED、プルアップ、プルダウンなど

プリント基板 CAD

- KiCad による階層設計

- KiCad による3D表示

- KiCad によるフットプリント作成におけるカスタム図形

- KiCad による面付け

プリント基板製造

- 製造業者による部品実装(PCBA)

- 卓上丸鋸盤によるカットと粉塵対策(集塵機、防塵マスク)

- ミシン目による面付け

実装関連

- 立体構造

- 細ピンヘッダ、細ピンソケット

- アルミフレーム

「トラ技」の記事からは、非常に多くの内容を流用させていただきました。心から感謝いたします。また、データ等を提供してくださっている方々に心から感謝いたします。

-

NovelLife Mini Table Saw https://ja.aliexpress.com/item/32845187139.html

13を付けて吸引しながら切りますが、周囲には白い粉が残ります。粉塵対策マスク14をしての作業が必須です。ガラスエポキシの粉塵についての記事15がありました。やはり真っ当な工場で切り出しまで実施すべきです。 ↩ -

Digikey ※Select CAD FormatでDesignSpark Mechanical(.step)を選択 ↩

-

YouTube - BF-016: Discrete MOS-FET Computer - test 3 - 4096 times of add ↩