Windows 10 Pro (v1909)

PYNQ-Z1 (Digilent) (以下、PYNQと表記)

Vivado v2019.1 (64-bit)

概要

- DMAを使ったPS<->PLの転送を行うBlock Designを作成する

- AXI DMAを使う

- AXI FIFOを使ってループバックする

- Tutorialに従うがVivado v2019.1になった変更に対応する

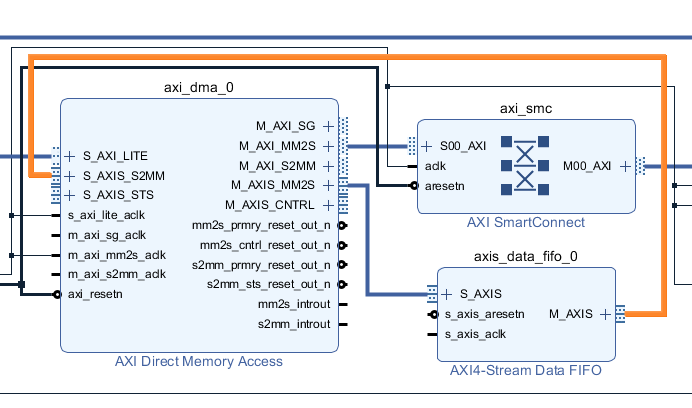

- 旧: AXI Interconnect

- 今回: AXI Smart Connect

- 実際にはVivadoが自動でしてくれる。AXI Interconnectがなく、AXI Smart Connectがあるようになる。

Tutorial

- Using the AXI DMA in Vivado

- http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html

- 2014年8月6日

- Vivado 2017.2での作成

- ビデオ (27分)もある

Vivado v2019.1での操作

- Part: cv7z020clg400-1

- ZYNQ Processing System追加

- ZYNQ Processing Systemダブルクリック

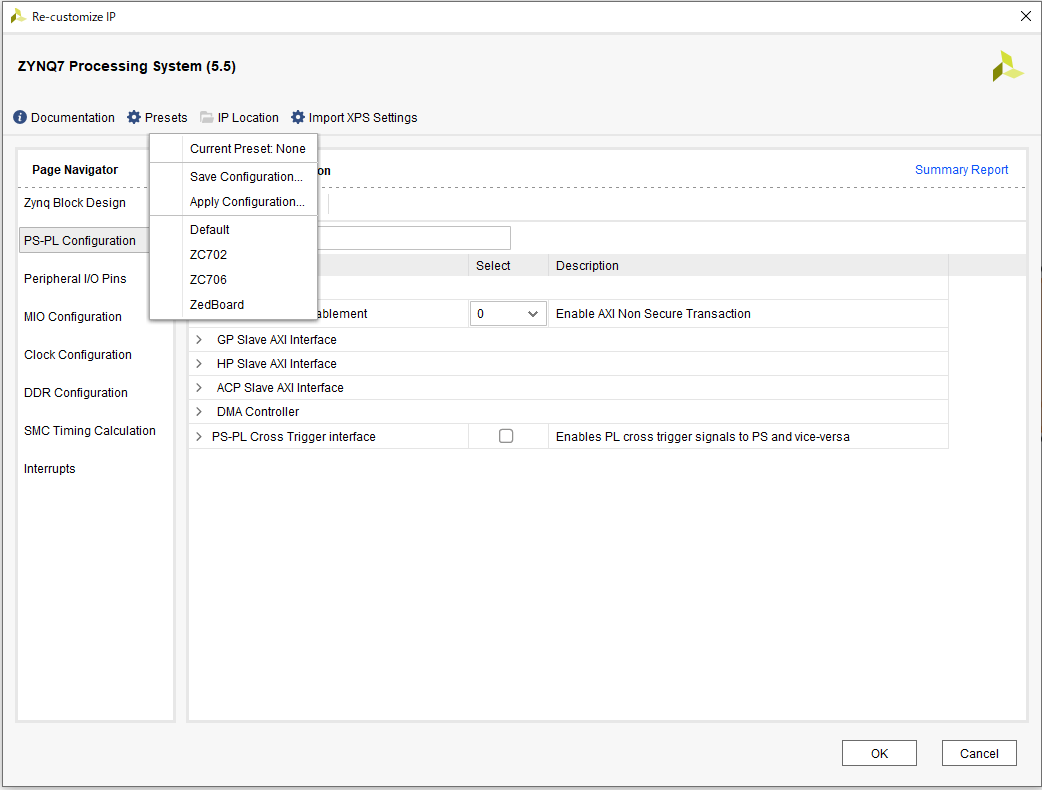

- Presets > Apply Configuration

- pynq_revC.tcl 読み込み (PYNQ-Z1用のプリセット)

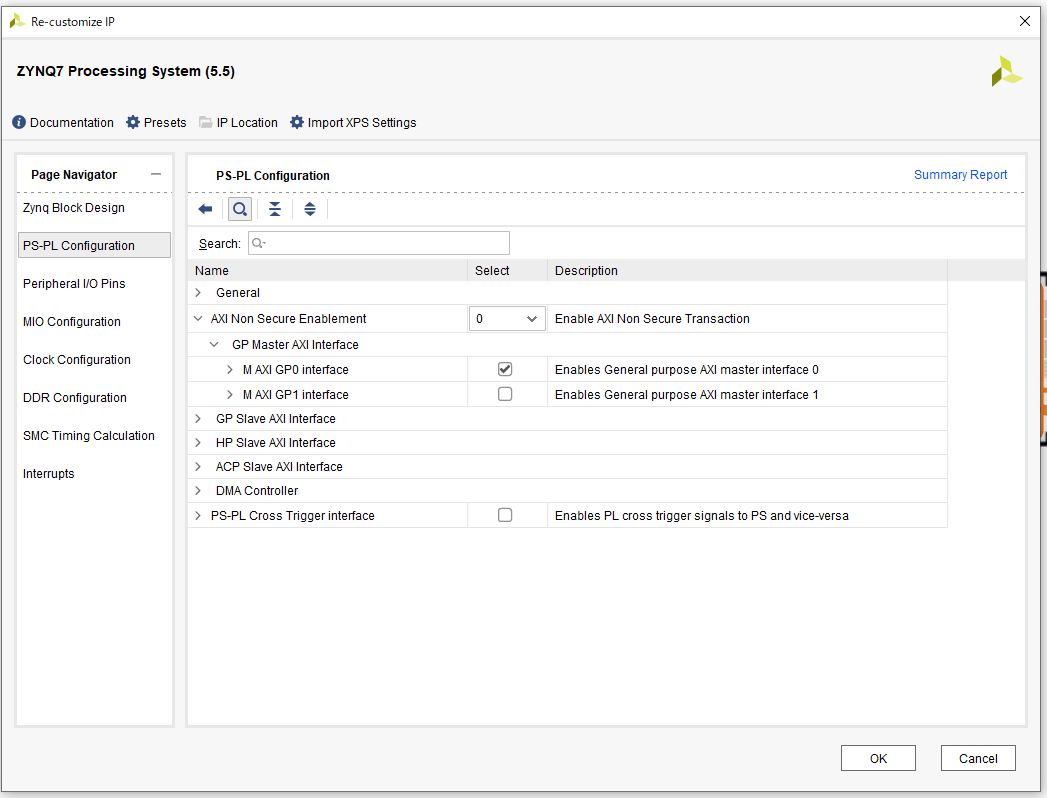

- PS-PL Configuration

- M AXI GP0 interfaceチェック

- ( AXI Non Secure Enablement > GP Master AXI Interface以下にある )

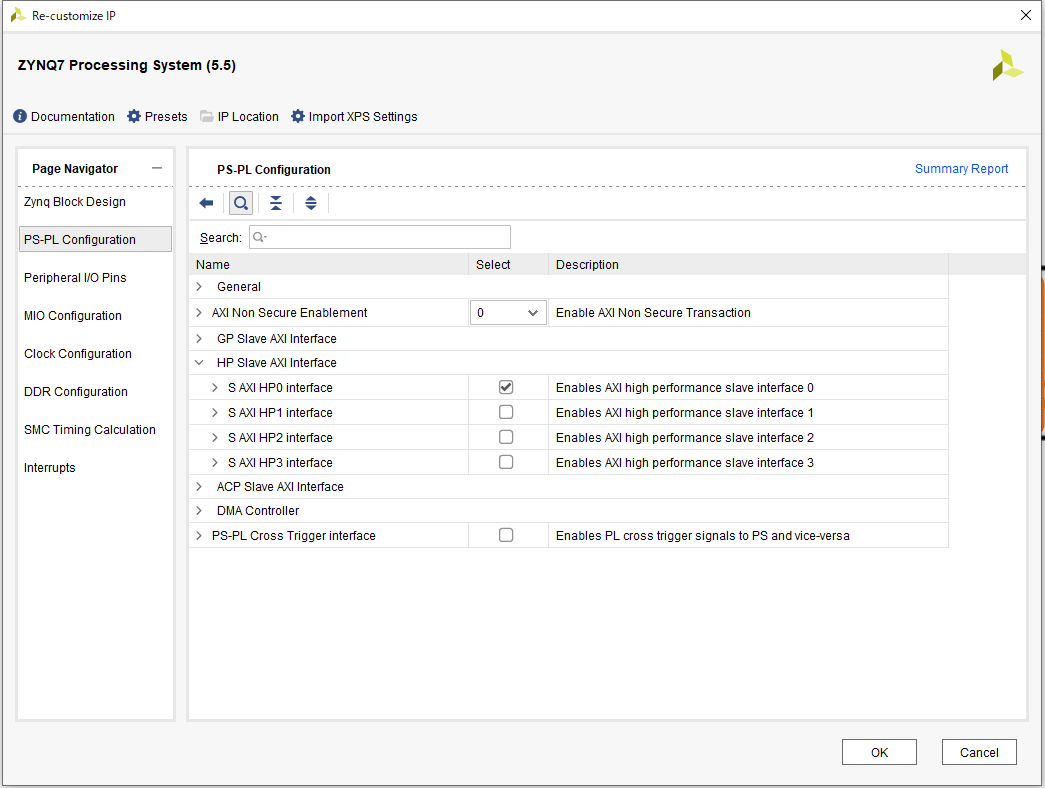

- S AXI HP0 interfaceチェック

- ( HP Slave AXI Interface 以下にある)

- High performanceだそうな (要確認)

- M AXI GP0 interfaceチェック

- Presets > Apply Configuration

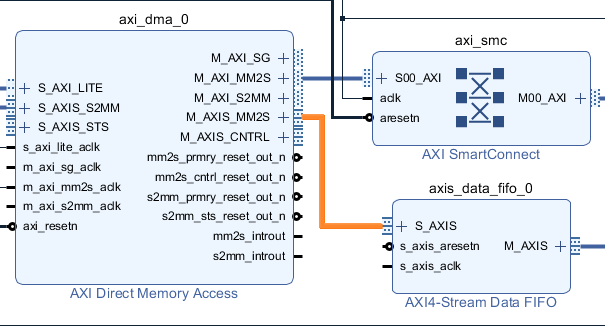

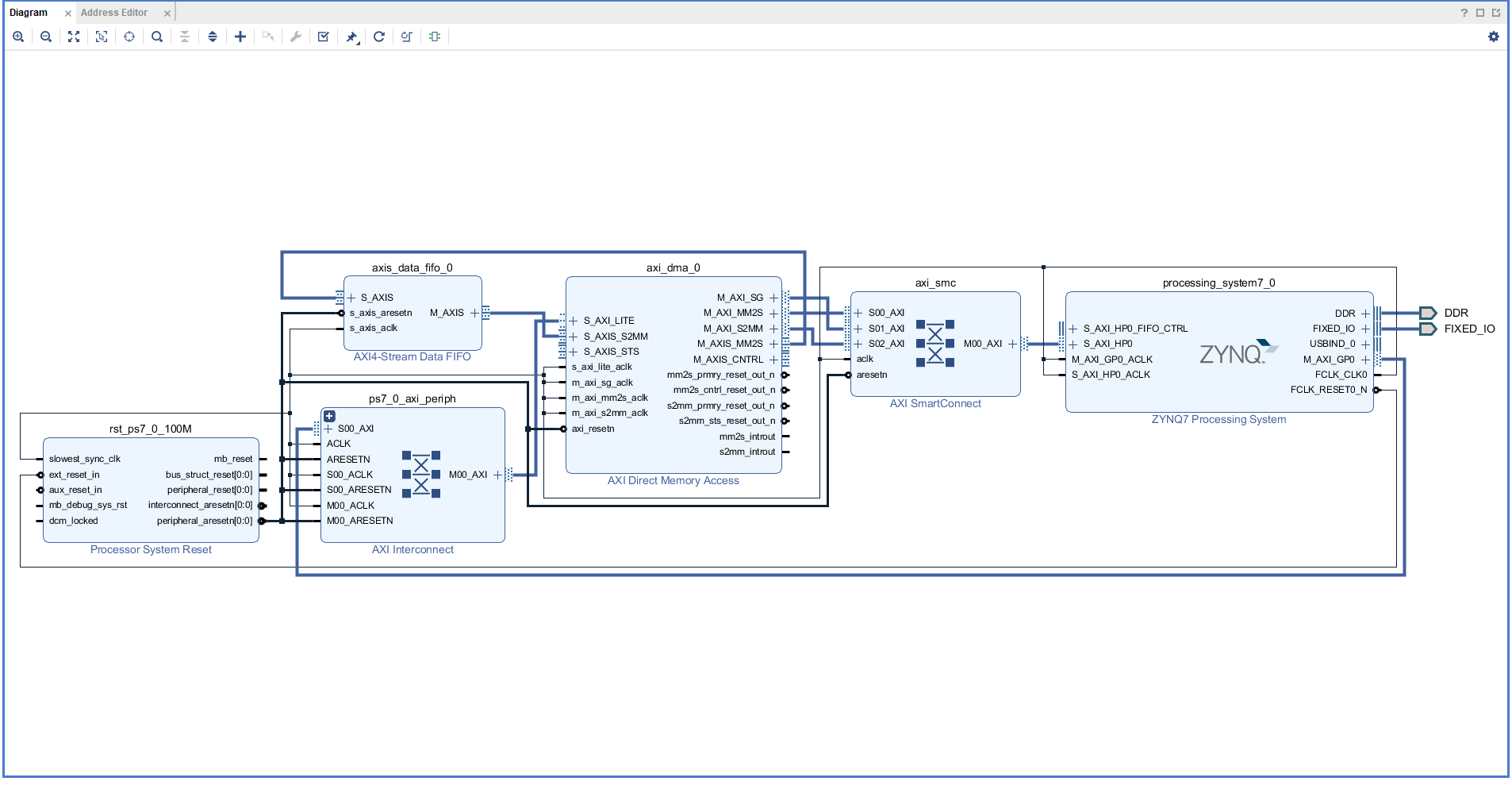

- AXI Direct Memory Access 追加

- AXI4-Stream Data FIFO追加

- Run Block Automation実行

- 設定そのまま OK

- Run Connection Automation実行

- S_AXI_LITE選択

- S_AXI_HP0選択

- Master: /axi_dma_0/M_AXI_MM2S を選択

- AXI4-Stream Data FIFOとAXI Direct Memory Accessを接続

- S_AXIS <-> M_AXIS_MM2S

- M_AXI_MM2Sではなく、M_AXIS_MM2S

- M_AXIS <-> S_AXIS_S2MM

- S_AXIS <-> M_AXIS_MM2S

- Run Connection Automation

- M_AXI_S2MM チェック

- M_AXI_SG チェック

- s_axix_aclkチェック

あとは「Create HDL Wrapper」をしてRun Synthesisを実施して、それ以降を逐次実施するとbistreamが完成する。

Core i7-6700K 4.00GHzで15分はかかる。

Warningがいくつか出る。このあたりは今後学習する項目。

完成したBlock Design

今後

PYNQでDMA関連の処理を実装する予定。

- Docs » PYNQ Libraries » DMA

問題はallocateがPYNQのv2.5でないと動かないこと。

PYNQのバージョンを上げるか、別の方法を探すことになる。

DigilentにあるPYNQ-Z1 Imageはv2.4?。

関連

情報整理で見つけた気になる記事。AXI DMAでなくBRAMを使う。

-

PYNQ を使って Python で手軽に FPGA を活用 (5)

-

Digilentが提供するPYNQ-Z1のImage v2.4に対応するDMAの実装

その後 (2020-08-08)

上記で生成したBlock Designではうまく動作しなかった。

代わりに下記を参考にしたものではうまく動作した。

https://github.com/Xilinx/PYNQ_Workshop/blob/master/Session_4/6_dma_tutorial.ipynb

https://github.com/Xilinx/PYNQ_Workshop/tree/master/Session_4/bitstream