動作環境

Windows 10 Pro (v1909)

PYNQ-Z1 (Digilent) (以下、PYNQと表記)

Vivado v2019.1 (64-bit)

概要

- HDMI出力を試す

- PYNQ-Z2のTutorialをPYNQ-Z1で試した

- XSDKでC実装の記載だが、Pythonで実行できた

Tutorial

配線についてはRun Automation...ではなく、手作業で接続していき、最終的にtclファイルで残りをつなげる。

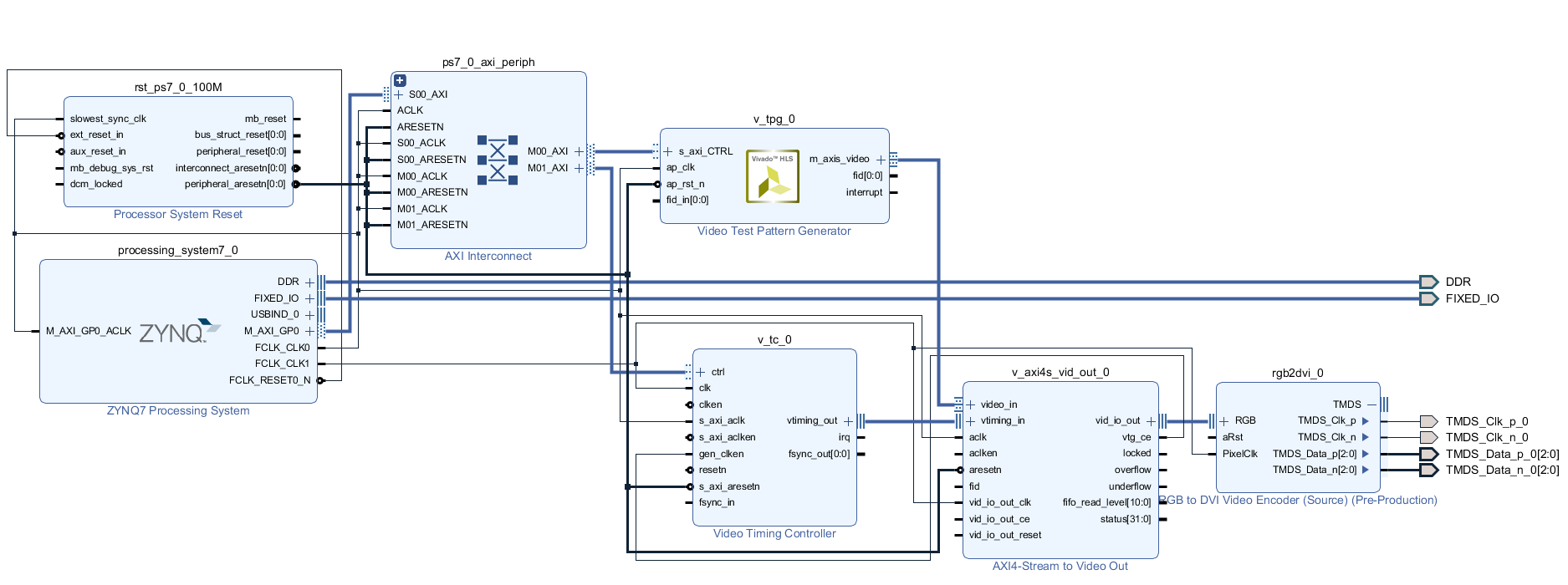

Block Design

完成したBlock Designは以下となった。

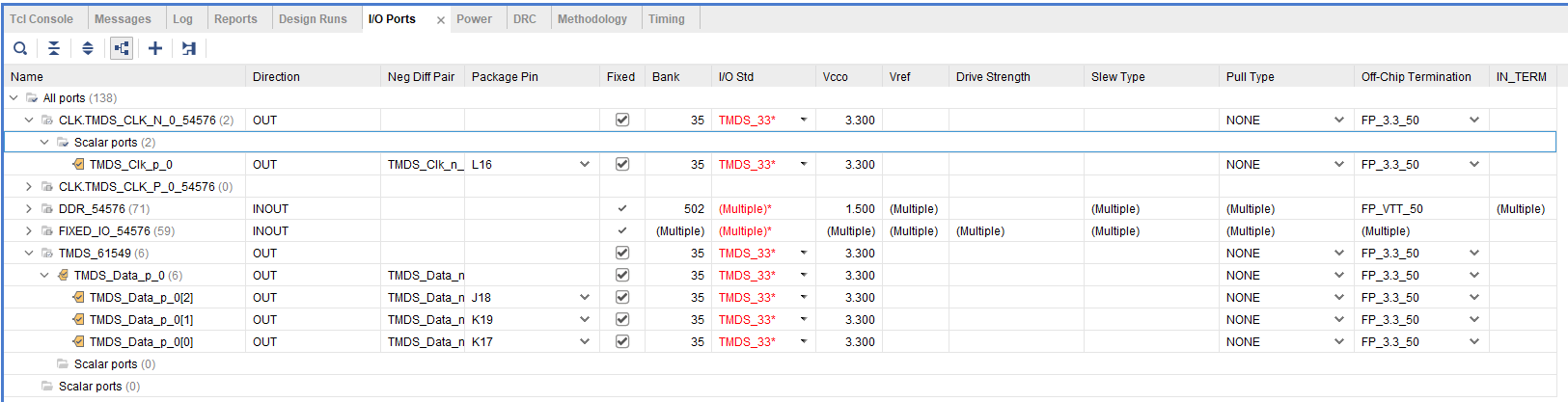

I/O Ports

Pythonコード

XSDKで実行ではなく、ブラウザ接続でPythonで動かした。

上記のTutorialのコメントにあるコードで動いた。

bitstreamの指定だけ違うので、以下のようにした。

from pynq import Overlay

from pynq import PL

OL = Overlay("/home/xilinx/pynq/overlays/base/HDMIout_PYNQZ2_2020_06_14.bit")

OL.download()

ov = OL

tpg = ov.v_tpg_0

vtc = ov.v_tc_0

tpg.write(0x10,600) # height

tpg.write(0x18,800) # width

tpg.write(0x40,0) # Set color space to RGB

tpg.write(0x20,9) # set pattern to color bar

tpg.write(0x00,0x81)

vtc.write(0x00,0x01)

参考にしているScriptがマジックナンバーだらけでよくはない。

XSDK実装を参考に上記のコメントを追加した。

結果

補足

HDMI出力に関しては様々な方法が見つかったが、PYNQを使うのであれば、上記のTutorialでとりあえず試してみるのがいいと思った。

もう少し自由度の高いことをする場合は、学習を進めてから。

まだまだ理解は浅い。

関連

以下は上記にたどり着くまでにHDMI出力について調べて気になった記事 (+ 後で見つけて気になった記事)。

-

なひたふJTAG日記: 特電Spartan-6ボードでHDMI出力に成功

- 2013.08.16

- XAPP495での実装例

- FPGAの部屋: ZYBOのHDMI入力をVGA出力に出力する1(プロジェクトの作製)

-

FPGAでHDMI出力(Full-HD):その①同期信号/画素データ生成

- @cyebu1103 さん

- 1から3まであります

- FPGA(Pynq Z1)を用いたHDMI動画出力(verilogHDL)

-

aster_ismの工作室: BASYS3でディスプレイ出力

- こちらのBlock Designはよりシンプルかもしれない

皆様、情報感謝です。

関連資料

-

Video Test Pattern Generator v8.0 > LogiCORE IP Product Guide

- PG103 December 17, 2019

- p19. BACKGROUND_PATTERN_ID (0x0020) Register にカラーパターンの値が記載されている

-

AXI4-Stream Video IP and System Design Guide

- UG934 October 30, 2019

- p33

- Frame Buffer Read/Write

- high-bandwidth direct memory access between memory and AXI4-Stream video type target pheripherals

- 下記のIPがVivadoで使える

- Video Frame Buffer Read

- Video Frame Buffer Writer

関連キーワード

Block Designで使っているIPなど。

- Video Test Pattern Generator

- Video Timing Controller

- AXI4-Stream to Video Out

- rgb2dvi

- RGB to DVI Video Encoder