参考: VHDLによるFPGA設計 & デバッグ by 松村謙 & 坂巻 佳壽美

実装

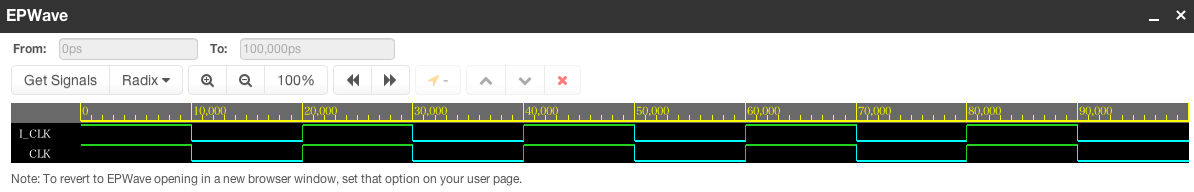

- 10nsごとにH,Lを切替えるCLKの生成

- 100nsで停止する

code

上記の本の情報を元に、自分なりに考えてみた。

design.vhd

library IEEE;

use IEEE.std_logic_1164.all;

entity CLOCK is

port ( CLK: in std_logic);

end CLOCK;

architecture RTL of CLOCK is

begin

end;

testbench.vhd

library IEEE;

use IEEE.std_logic_1164.all;

entity testbench is

end testbench;

architecture SIM of testbench is

signal I_CLK : std_logic := '1';

component CLOCK

port ( CLK: in std_logic);

end component;

begin

process begin

I_CLK <= '1';

wait for 10 ns;

I_CLK <= '0';

wait for 10 ns;

end process;

process begin

wait for 100 ns;

-- to end the testbench

assert false

report "end." severity FAILURE;

end process;

U1: CLOCK port map(CLK => I_CLK);

end SIM;

testbenchの1つめのprocess beginでCLKを生成しつつ、2つめのprocess beginでシミュレーションを停止する時間を100nsとしている。