動作確認

Vivado 2015.4 on Windows 8.1 pro (64bit)

パルスカウンタなどで使うと思われるカウント値のホールド機能を考えてみた。

言葉しか知らないラッチ回路やフリップフロップ回路と関係あるのか今は未消化。

仕組みとしては、以下で実装したカウンタ機能において、trigの立ち上がりエッジ時にカウンタ値を別のstd_logic_vector型にコピーするということにした。

http://qiita.com/7of9/items/b669e37d52721273c923

code

countStore.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity countStore is

port( clk : in std_logic;

reset : in std_logic;

cnt_d : inout std_logic_vector (3 downto 0); -- counter

trig : in std_logic; -- trigger to store the cnt_d value

str_d : out std_logic_vector (3 downto 0) -- store of the counter value

);

end countStore;

architecture Behavior of countStore is

signal DFF_4 : std_logic_vector (3 downto 0) := "0000";

begin

process(trig)

begin

if ( trig'event and trig = '1') then

str_d <= cnt_d;

end if;

end process;

process(Clk, Reset)

begin

cnt_d <= DFF_4;

if (Reset = '1') then

DFF_4 <= (others => '0');

elsif ( clk'event and clk = '1') then

if (DFF_4 = "1111") then

DFF_4 <= (others => '0');

end if;

DFF_4 <= DFF_4 + 1;

end if;

end process;

end Behavior;

countStore.tb

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity testbench is

end testbench;

architecture behavior of testbench is

signal clk : std_logic;

signal reset : std_logic;

signal cnt_d : std_logic_vector (3 downto 0);

signal trig : std_logic;

signal str_d : std_logic_vector (3 downto 0);

constant clk_period : time := 10 ns;

begin

uut: entity work.countStore PORT MAP (

clk => clk,

reset => reset,

cnt_d => cnt_d,

trig => trig,

str_d => str_d);

trigger : process

begin

wait for 5 * clk_period / 2; -- for delay (5: arbitrary)

wait for 20 * clk_period / 2; -- (20: arbitrary)

trig <= '1';

wait for 20 * clk_period / 2;

trig <= '0';

end process;

stimulus : process

begin

wait for 32 * clk_period / 2;

reset <= '1';

wait for 32 * clk_period / 2;

reset <= '0';

-- wait for 300 ns;

end process;

clk_process : process

begin

clk <= '0';

wait for clk_period / 2;

clk <= '1';

wait for clk_period / 2;

end process;

end behavior;

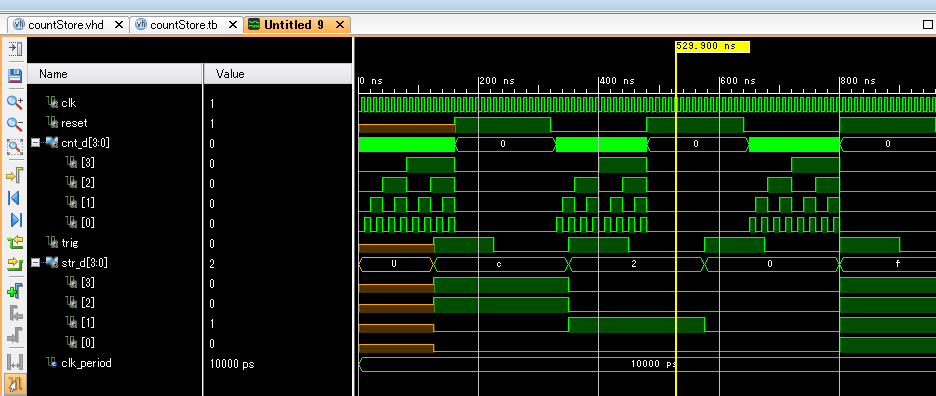

結果

trigの立ち上がりエッジ時のcnt_dの値がstr_dにコピーされている。

図でオレンジ色になっている部分は初期化処理が失敗している。このあたりはこれからの課題。